飞利浦 半导体

lpc2104/2105/2106

单独的-碎片 32-位 微控制器

产品 数据 rev. 04 — 05 二月 2004 7 的 32

9397 750 12792

© koninklijke 飞利浦 electronics n.v. 2004. 所有 权利 保留.

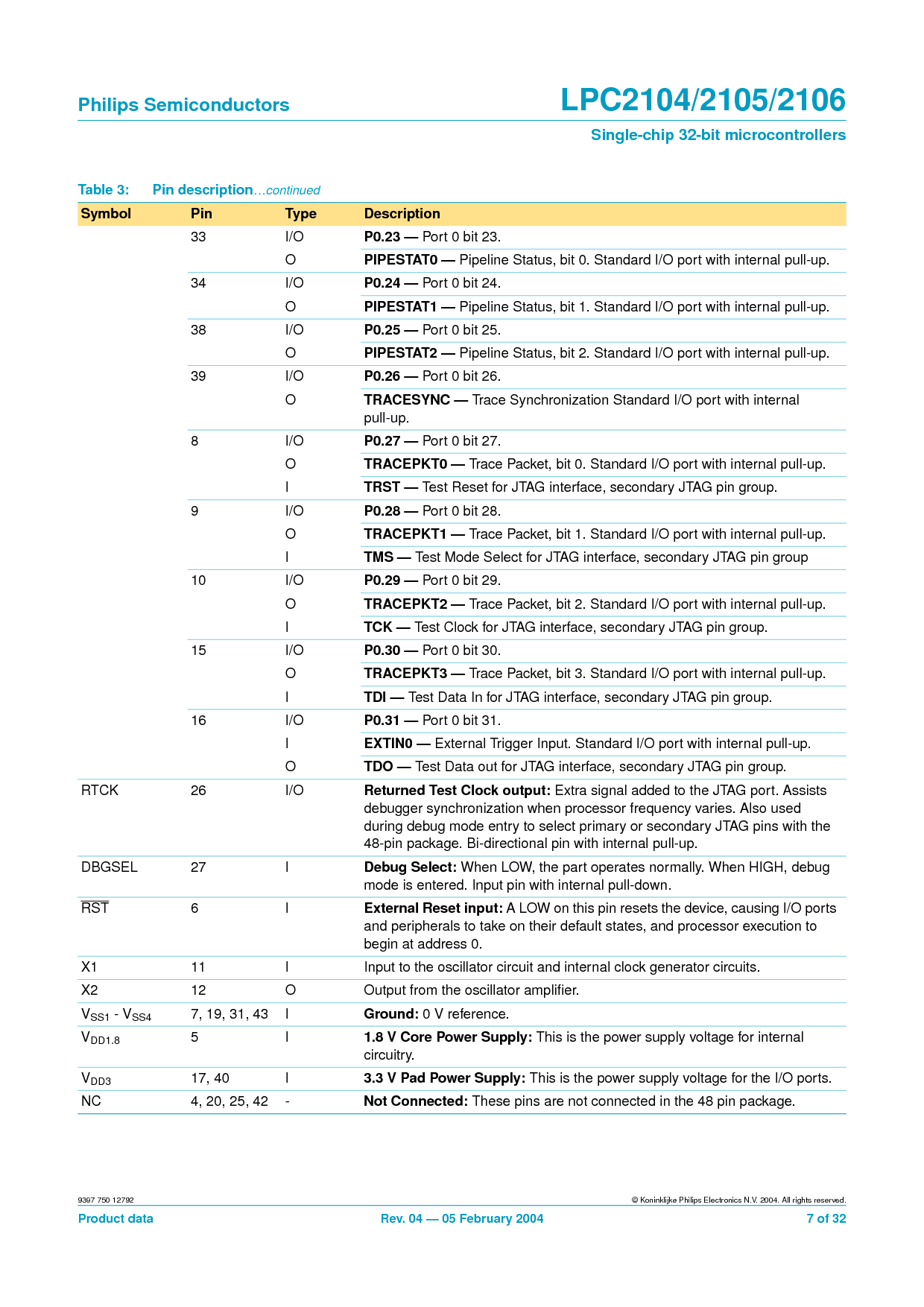

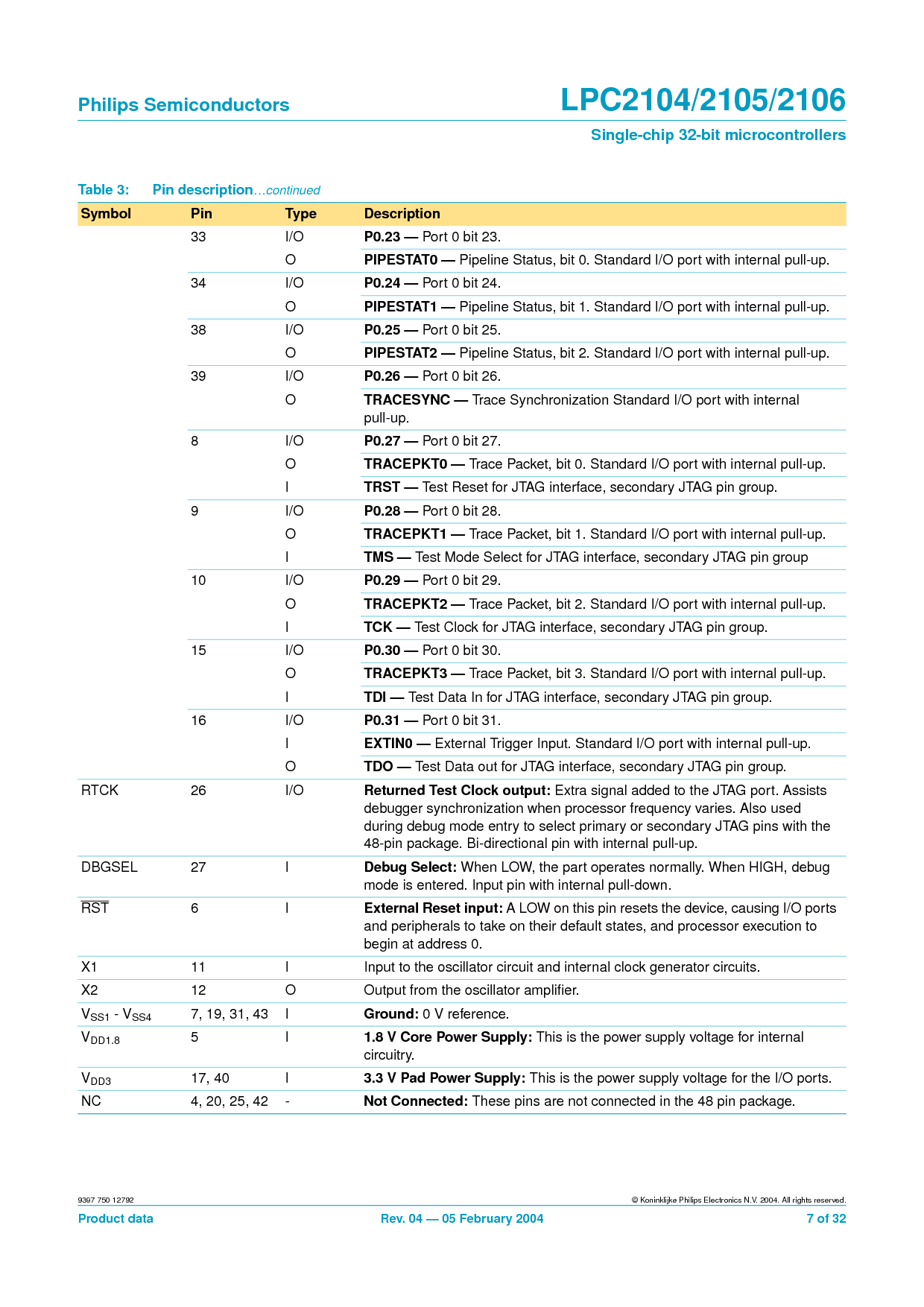

33 i/o

p0.23 —

端口 0 位 23.

O

pipestat0 —

pipeline 状态, 位 0. 标准 i/o 端口 和 内部的 拉-向上.

34 i/o

p0.24 —

端口 0 位 24.

O

pipestat1 —

pipeline 状态, 位 1. 标准 i/o 端口 和 内部的 拉-向上.

38 i/o

p0.25 —

端口 0 位 25.

O

pipestat2 —

pipeline 状态, 位 2. 标准 i/o 端口 和 内部的 拉-向上.

39 i/o

p0.26 —

端口 0 位 26.

O

tracesync —

查出 同步 标准 i/o 端口 和 内部的

拉-向上.

8 i/o

p0.27 —

端口 0 位 27.

O

tracepkt0 —

查出 小包装板盒, 位 0. 标准 i/o 端口 和 内部的 拉-向上.

I

trst —

测试 重置 为 jtag 接口, secondary jtag 管脚 组.

9 i/o

p0.28 —

端口 0 位 28.

O

tracepkt1 —

查出 小包装板盒, 位 1. 标准 i/o 端口 和 内部的 拉-向上.

I

tms —

测试 模式 选择 为 jtag 接口, secondary jtag 管脚 组

10 i/o

p0.29 —

端口 0 位 29.

O

tracepkt2 —

查出 小包装板盒, 位 2. 标准 i/o 端口 和 内部的 拉-向上.

I

tck —

测试 时钟 为 jtag 接口, secondary jtag 管脚 组.

15 i/o

p0.30 —

端口 0 位 30.

O

tracepkt3 —

查出 小包装板盒, 位 3. 标准 i/o 端口 和 内部的 拉-向上.

I

tdi —

测试 数据 在 为 jtag 接口, secondary jtag 管脚 组.

16 i/o

p0.31 —

端口 0 位 31.

I

extin0 —

外部 触发 输入. 标准 i/o 端口 和 内部的 拉-向上.

O

tdo —

测试 数据 输出 为 jtag 接口, secondary jtag 管脚 组.

RTCK 26 i/o

returned 测试 时钟 输出:

extra 信号 增加 至 这 jtag 端口. assists

debugger 同步 当 处理器 频率 varies. 也 使用

在 debug 模式 entry 至 选择 primary 或者 secondary jtag 管脚 和 这

48-管脚 包装. bi-directional 管脚 和 内部的 拉-向上.

DBGSEL 27 I

debug 选择:

当 低, 这 部分 运作 正常情况下. 当 高, debug

模式 是 entered. 输入 管脚 和 内部的 拉-向下.

RST 6 I

外部 重置 输入:

一个 低 在 这个 管脚 resets 这 设备, 造成 i/o 端口

和 peripherals 至 引领 在 它们的 default states, 和 处理器 执行 至

begin 在 地址 0.

X1 11 I 输入 至 这 振荡器 电路 和 内部的 时钟 发生器 电路.

X2 12 O 输出 从 这 振荡器 amplifier.

V

SS1

- v

SS4

7, 19, 31, 43 I

地面:

0 v 涉及.

V

dd1.8

5I

1.8 v 核心 电源 供应:

这个 是 这 电源 供应 电压 为 内部的

电路系统.

V

DD3

17, 40 I

3.3 v 垫子 电源 供应:

这个 是 这 电源 供应 电压 为 这 i/o 端口.

NC 4, 20, 25, 42 -

不 连接:

这些 管脚 是 不 连接 在 这 48 管脚 包装.

表格 3: 管脚 描述

…continued

标识 管脚 类型 描述