AD7801

–8–

rev. 0

涉及

这 ad7801 有 这 能力 至 使用 也 一个 外部 涉及

应用 通过 这 refin 管脚 或者 一个 内部的 涉及 发生

从 v

DD

. 图示 20 显示 这 涉及 输入 arrangement

在哪里 也 这 内部的 v

DD

/2 或者 这 externally 应用 涉及

能 是选择.

这 内部的 涉及 是 选择 用 tying 这 refin 管脚 至

V

DD

. 如果 一个 外部 涉及 是 至 是 使用, 这个 能 是 直接地

应用 至 这 refin 管脚 和 如果 这个 是 1 v 在下 v

DD

, 这

内部的 电路系统 将 选择 这个 externally 应用 涉及 作

这 涉及 源 为 这 dac.

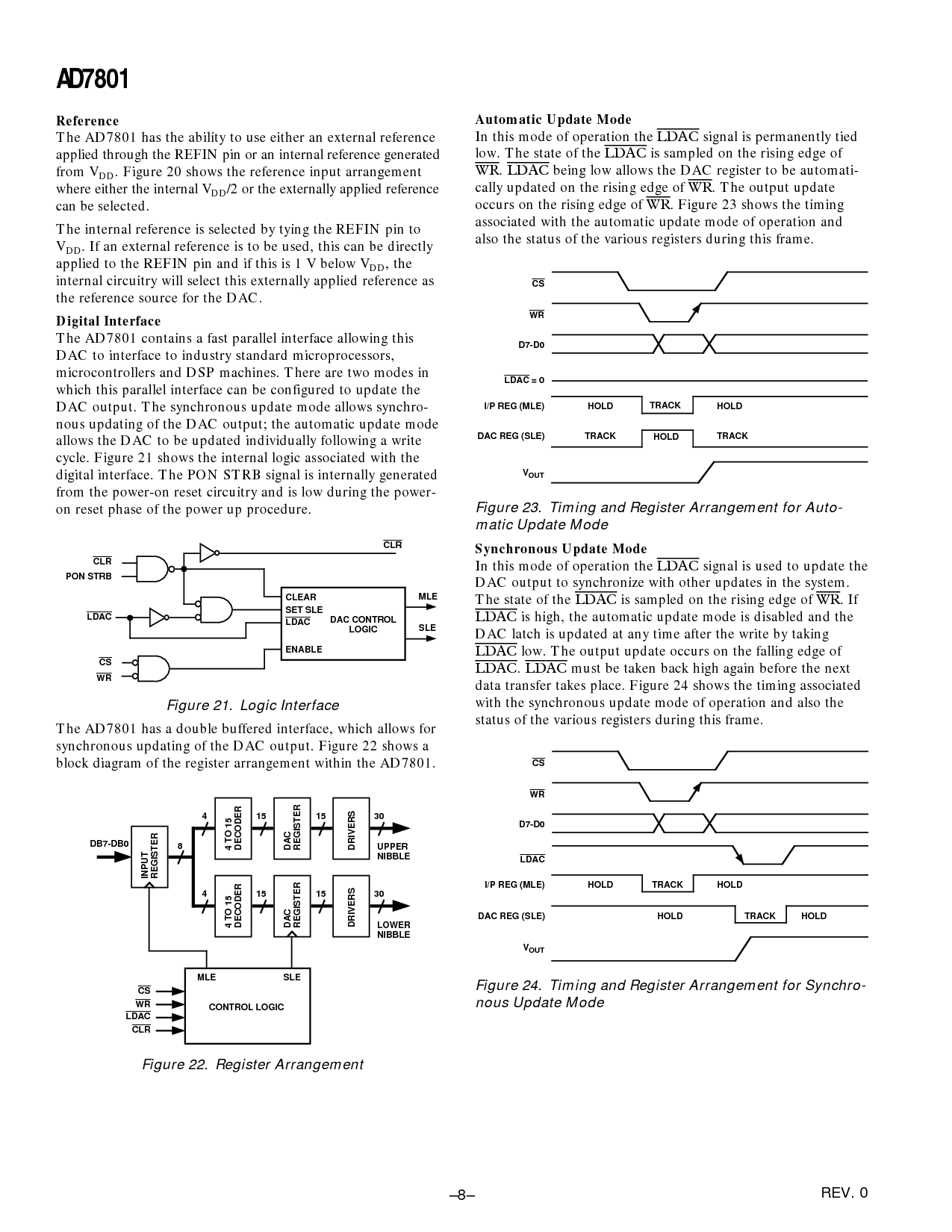

数字的 接口

这 ad7801 包含 一个 快 并行的 接口 准许 这个

dac 至 接口 至 工业 标准 微处理器,

微控制器 和 dsp machines. 那里 是 二 模式 在

这个 这个 并行的 接口 能 是 配置 至 更新 这

dac 输出. 这 同步的 更新 模式 准许 synchro-

nous updating 的 这 dac 输出; 这 自动 更新 模式

准许 这 dac 至 是 updated individually 下列的 一个 写

循环. 图示 21 显示 这 内部的 逻辑 有关联的 和 这

数字的 接口. 这 pon strb 信号 是 内部 发生

从 这 电源-在 重置 电路系统 和 是 低 在 这 电源-

在 重置 阶段 的 这 电源 向上 程序.

CLEAR

设置 sle

LDAC

使能

dac 控制

逻辑

MLE

SLE

CLR

pon strb

CLR

LDAC

CS

WR

图示 21. 逻辑 接口

这 ad7801 有 一个 翻倍 缓冲 接口, 这个 准许 为

同步的 updating 的 这 dac 输出. 图示 22 显示 一个

块 图解 的 这 寄存器 arrangement 在里面 这 ad7801.

MLE SLE

控制 逻辑

CS

WR

LDAC

CLR

4

15 15 30

8

输入

寄存器

4 至 15

解码器

DAC

寄存器

4

15 15 30

4 至 15

解码器

DAC

寄存器

驱动器

更小的

NIBBLE

UPPER

NIBBLE

db7-db0

驱动器

图示 22. 寄存器 arrangement

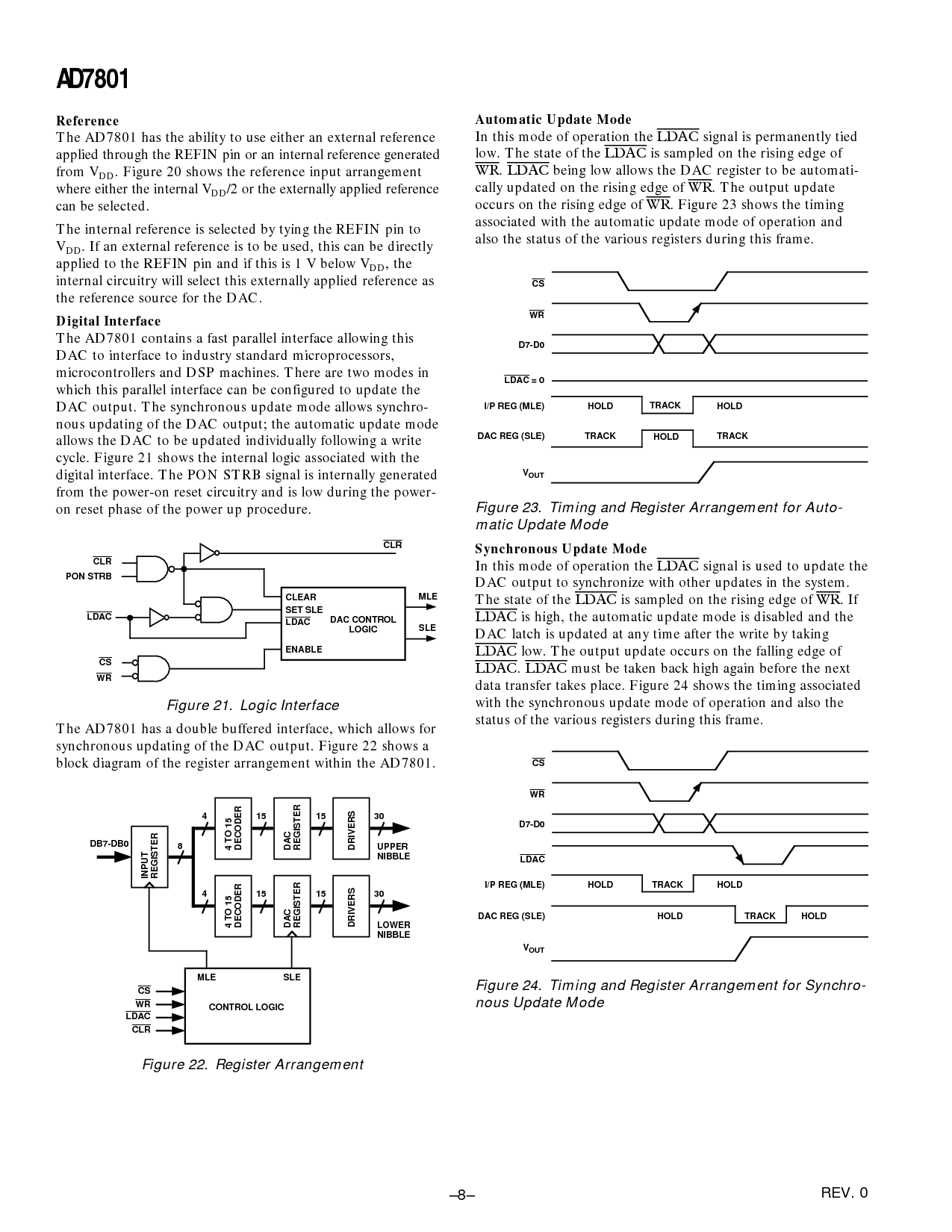

自动 更新 模式

在 这个 模式 的 运作 这

LDAC

信号 是 permanently 系

低. 这 状态 的 这

LDAC

是 抽样 在 这 rising 边缘 的

WR

.

LDAC

正在 低 准许 这 dac 寄存器 至 是 自动地-

cally updated 在 这 rising 边缘 的

WR

. 这 输出 更新

occurs 在 这 rising 边缘 的

WR

. 图示 23 显示 这 定时

有关联的 和 这 自动 更新 模式 的 运作 和

也 这 状态 的 这 各种各样的 寄存器 在 这个 框架.

支撑 支撑

追踪 追踪

d7-d0

WR

CS

LDAC

= 0

i/p reg (mle)

dac reg (sle)

V

输出

追踪

支撑

图示 23. 定时 和 寄存器 arrangement 为 自动-

matic 更新 模式

同步的 更新 模式

在 这个 模式 的 运作 这

LDAC

信号 是 使用 至 更新 这

dac 输出 至 同步 和 其它 updates 在 这 系统.

这 状态 的 这

LDAC

是 抽样 在 这 rising 边缘 的

WR

. 如果

LDAC

是 高, 这 自动 更新 模式 是 无能 和 这

dac 获得 是 updated 在 任何 时间 之后 这 写 用 带去

LDAC

低. 这 输出 更新 occurs 在 这 下落 边缘 的

LDAC

.

LDAC

必须 是 带去 后面的 高 又一次 在之前 这 next

数据 转移 takes 放置. 图示 24 显示 这 定时 有关联的

和 这 同步的 更新 模式 的 运作 和 也 这

状态 的 这 各种各样的 寄存器 在 这个 框架.

支撑 支撑

d7-d0

WR

CS

LDAC

i/p reg (mle)

dac reg (sle)

V

输出

支撑 支撑追踪

追踪

图示 24. 定时 和 寄存器 arrangement 为 synchro-

nous 更新 模式