ad7834/ad7835

rev. 一个

–9–

表格 i. d23 控制

D23 控制 函数

0 ignore 下列的 23 位 的 信息.

1 使用 下列的 23 位 的 地址 和

数据 作 正常的.

d22 和 d21:

解码 至 选择 一个 的 这 四 dac 途径

在里面 一个 设备. 这 真实 表格 为 d22 和 d21 是 作 显示

在下 在 表格 ii.

表格 ii. d22, d21 控制

D22 D21 控制 函数

0 0 选择 频道 1

0 1 选择 频道 2

1 0 选择 频道 3

1 1 选择 频道 4

D20–D16

: 确定 这 包装 地址. 这 five 地址

位 准许 向上 至 32 独立的 包装 至 是 individually de-

coded. successful 解码 是 accomplished 当 这些 five 位

相一致 向上 和 这 five hardwired 管脚 在 这 物理的 包装.

D15–D0

: dac 数据 至 是 承载 在 identified dac 输入

寄存器. 这个 数据 必须 有 二 leading 0s followed 用 14 位

的 数据, msb 第一. 这 msb 是 在 location d13 的 这 24-位

数据 stream.

数据 loading—ad7835, 并行的 加载 设备

数据 能 是 承载 在 这 ad7835 在 也 笔直地 14-位

宽 words 或者 在 二 8-位 字节.

在 系统 这个 能 转移 14-位 宽 数据, 这

BYSHF

输入 应当 是 hardwired 至 v

CC

. 这个 sets 向上 这 ad7835

作 一个 笔直地 14-位 并行的-加载 dac.

在 8-位 总线 系统 在哪里 它 是 必需的 至 转移 数据 在 二

字节, 它 是 需要 至 有 这

BYSHF

输入 下面 逻辑 con-

trol. 在 此类 一个 系统 这 顶 6 管脚 的 这 设备 数据 总线,

db8–db13, 必须 是 hardwired 至 dgnd. 新 低 字节 数据

是 承载 在 这 更小的 8 places 的 这 选择 输入 寄存器 用

carrying 输出 一个 写 运作 当 支持

BYSHF

高. 一个

第二 写 运作 是 subsequently executed 和

BYSHF

低 和 这 6 msbs 在 这 db0–db5 输入 (db5 = msb).

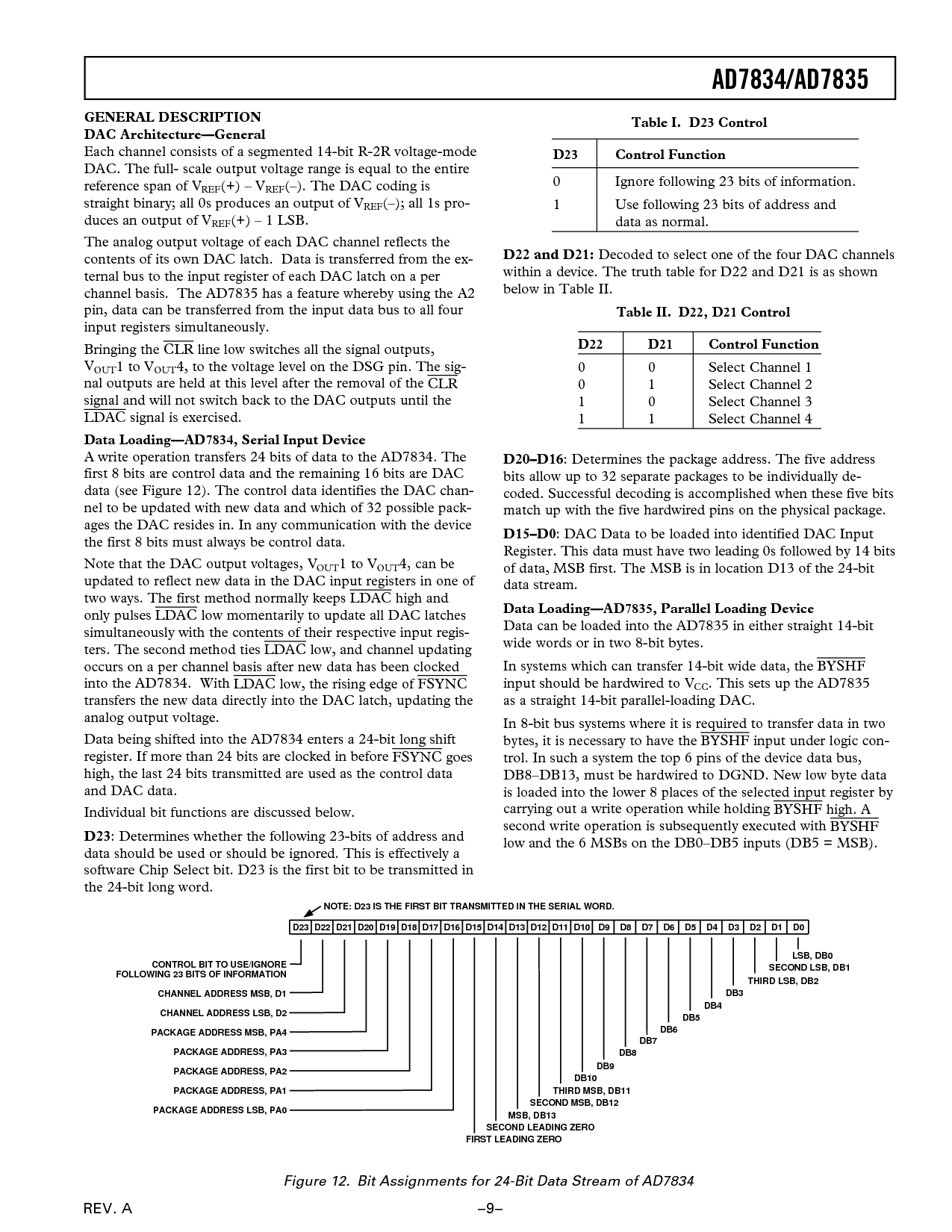

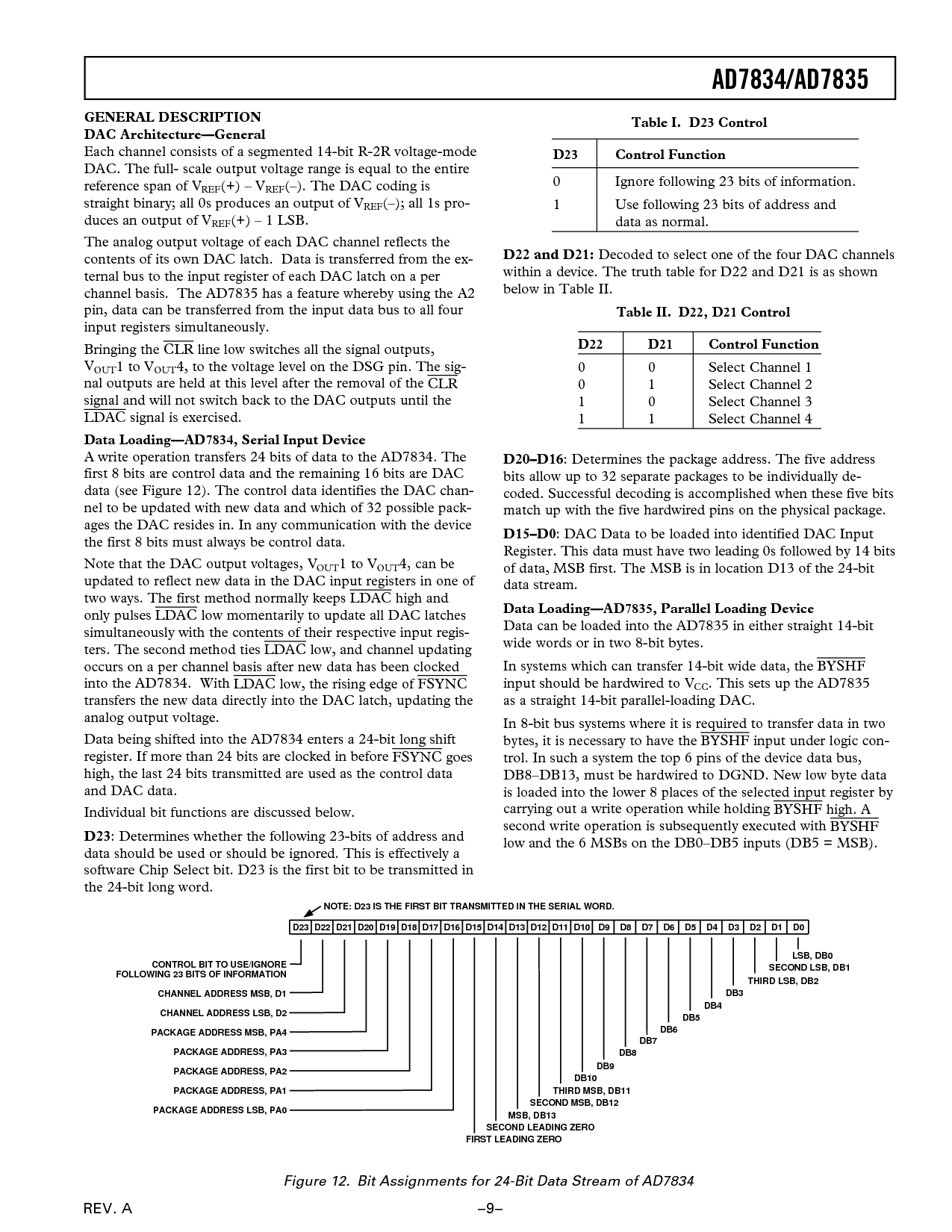

D23 D22 D21 D20

D19

D18 D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

便条: d23 是 这 第一 位 transmitted 在 这 串行 文字.

控制 位 至 使用/ignore

下列的 23 位 的 信息

频道 地址 msb, d1

频道 地址 lsb, d2

包装 地址 msb, pa4

包装 地址, pa3

包装 地址, pa2

包装 地址, pa1

包装 地址 lsb, pa0

lsb, db0

第二 lsb, db1

第三 lsb, db2

DB3

DB4

DB5

DB6

DB7

DB8

DB9

DB10

第三 msb, db11

第二 msb, db12

msb, db13

第二 leading 零

第一 leading 零

图示 12. 位 assignments 为 24-位 数据 stream 的 ad7834

一般 描述

dac architecture—general

各自 频道 组成 的 一个 segmented 14-位 r-2r 电压-模式

dac. 这 全部- 规模 输出 电压 范围 是 equal 至 这 全部

涉及 span 的 v

REF

(+) – v

REF

(–). 这 dac 编码 是

笔直地 二进制的; 所有 0s 生产 一个 输出 的 v

REF

(–); 所有 1s pro-

duces 一个 输出 的 v

REF

(+) – 1 lsb.

这 相似物 输出 电压 的 各自 dac 频道 reflects 这

内容 的 它的 自己的 dac 获得. 数据 是 transferred 从 这 ex-

ternal 总线 至 这 输入 寄存器 的 各自 dac 获得 在 一个 每

频道 基准. 这 ad7835 有 一个 特性 凭此 使用 这 a2

管脚, 数据 能 是 transferred 从 这 输入 数据 总线 至 所有 四

输入 寄存器 同时发生地.

bringing 这

CLR

线条 低 switches 所有 这 信号 输出,

V

输出

1 至 v

输出

4, 至 这 电压 水平的 在 这 dsg 管脚. 这 sig-

nal 输出 是 使保持 在 这个 水平的 之后 这 除去 的 这

CLR

信号 和 将 不 转变 后面的 至 这 dac 输出 直到 这

LDAC

信号 是 exercised.

数据 loading—ad7834, 串行 输入 设备

一个 写 运作 transfers 24 位 的 数据 至 这 ad7834. 这

第一 8 位 是 控制 数据 和 这 remaining 16 位 是 dac

数据 (看 图示 12). 这 控制 数据 identifies 这 dac chan-

nel 至 是 updated 和 新 数据 和 这个 的 32 可能 包装-

ages 这 dac resides 在. 在 任何 交流 和 这 设备

这 第一 8 位 必须 总是 是 控制 数据.

便条 那 这 dac 输出 电压, v

输出

1 至 v

输出

4, 能 是

updated 至 反映 新 数据 在 这 dac 输入 寄存器 在 一个 的

二 方法. 这 第一 方法 正常情况下 keeps

LDAC

高 和

仅有的 脉冲

LDAC

低 短促地 至 更新 所有 dac latches

同时发生地 和 这 内容 的 它们的 各自的 输入 regis-

ters. 这 第二 方法 ties

LDAC

低, 和 频道 updating

occurs 在 一个 每 频道 基准 之后 新 数据 有 被 clocked

在 这 ad7834. 和

LDAC

低, 这 rising 边缘 的

FSYNC

transfers 这 新 数据 直接地 在 这 dac 获得, updating 这

相似物 输出 电压.

数据 正在 shifted 在 这 ad7834 enters 一个 24-位 长 变换

寄存器. 如果 更多 比 24 位 是 clocked 在 在之前

FSYNC

变得

高, 这 last 24 位 transmitted 是 使用 作 这 控制 数据

和 dac 数据.

单独的 位 功能 是 discussed 在下.

D23

: 确定 whether 这 下列的 23-位 的 地址 和

数据 应当 是 使用 或者 应当 是 ignored. 这个 是 effectively 一个

软件 碎片 选择 位. d23 是 这 第一 位 至 是 transmitted 在

这 24-位 长 文字.