rev. b

AD7865

–11–

ad7865-3

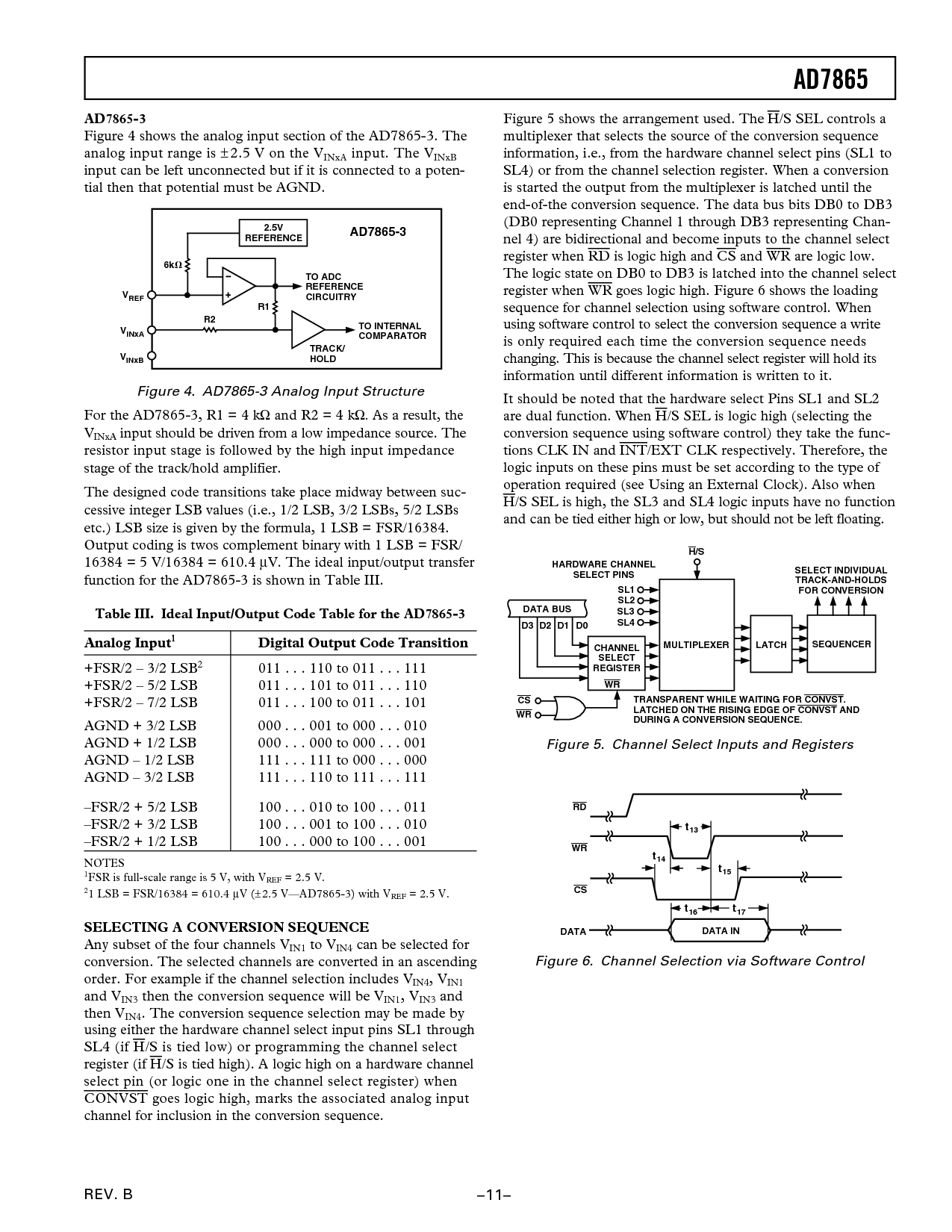

图示 4 显示 这 相似物 输入 部分 的 这 ad7865-3. 这

相似物 输入 范围 是

±

2.5 v 在 这 v

INxA

输入. 这 v

INxB

输入 能 是 left unconnected 但是 如果 它 是 连接 至 一个 poten-

tial 然后 那 潜在的 必须 是 agnd.

ad7865-3

V

INxA

追踪/

支撑

至 模数转换器

涉及

电路系统

至 内部的

比较器

R1

R2

6k

2.5v

涉及

V

INxB

V

REF

图示 4. ad7865-3 相似物 输入 结构

为 这 ad7865-3, r1 = 4 k

Ω

和 r2 = 4 k

Ω.

作 一个 结果, 这

V

INxA

输入 应当 是 驱动 从 一个 低 阻抗 源. 这

电阻 输入 平台 是 followed 用 这 高 输入 阻抗

平台 的 这 追踪/支撑 放大器.

这 设计 代号 transitions 引领 放置 midway 在 suc-

cessive integer lsb 值 (i.e., 1/2 lsb, 3/2 lsbs, 5/2 lsbs

等.) lsb 大小 是 给 用 这 formula, 1 lsb = fsr/16384.

输出 编码 是 twos complement 二进制的 和 1 lsb = fsr/

16384 = 5 v/16384 = 610.4

µ

v. 这 完美的 输入/输出 转移

函数 为 这 ad7865-3 是 显示 在 表格 iii.

表格 iii. 完美的 输入/输出 代号 表格 为 这 ad7865-3

相似物 输入

1

数字的 输出 代号 转变

+fsr/2

–

3/2 lsb

2

011 . . . 110 至 011 . . . 111

+fsr/2

–

5/2 lsb 011 . . . 101 至 011 . . . 110

+fsr/2

–

7/2 lsb 011 . . . 100 至 011 . . . 101

agnd + 3/2 lsb 000 . . . 001 至 000 . . . 010

agnd + 1/2 lsb 000 . . . 000 至 000 . . . 001

AGND

–

1/2 lsb 111 . . . 111 至 000 . . . 000

AGND

–

3/2 lsb 111 . . . 110 至 111 . . . 111

–

fsr/2 + 5/2 lsb 100 . . . 010 至 100 . . . 011

–

fsr/2 + 3/2 lsb 100 . . . 001 至 100 . . . 010

–

fsr/2 + 1/2 lsb 100 . . . 000 至 100 . . . 001

注释

1

fsr 是 全部-规模 范围 是 5 v, 和 v

REF

= 2.5 v.

2

1 lsb = fsr/16384 = 610.4

µ

v (

±

2.5 v

—

ad7865-3) 和 v

REF

= 2.5 v.

selecting 一个 转换 sequence

任何 subset 的 这 四 途径 v

IN1

至 v

IN4

能 是 选择 为

转换. 这 选择 途径 是 转变 在 一个 ascending

顺序. 为 例子 如果 这 频道 选择 包含 v

IN4

, v

IN1

和 v

IN3

然后 这 转换 sequence 将 是 v

IN1

, v

IN3

和

然后 v

IN4

. 这 转换 sequence 选择 将 是 制造 用

使用 也 这 硬件 频道 选择 输入 管脚 sl1 通过

sl4 (如果

H

/s 是 系 低) 或者 程序编制 这 频道 选择

寄存器 (如果

H

/s 是 系 高). 一个 逻辑 高 在 一个 硬件 频道

选择 管脚 (或者 逻辑 一个 在 这 频道 选择 寄存器) 当

CONVST

变得 逻辑 高, marks 这 有关联的 相似物 输入

频道 为 包括 在 这 转换 sequence.

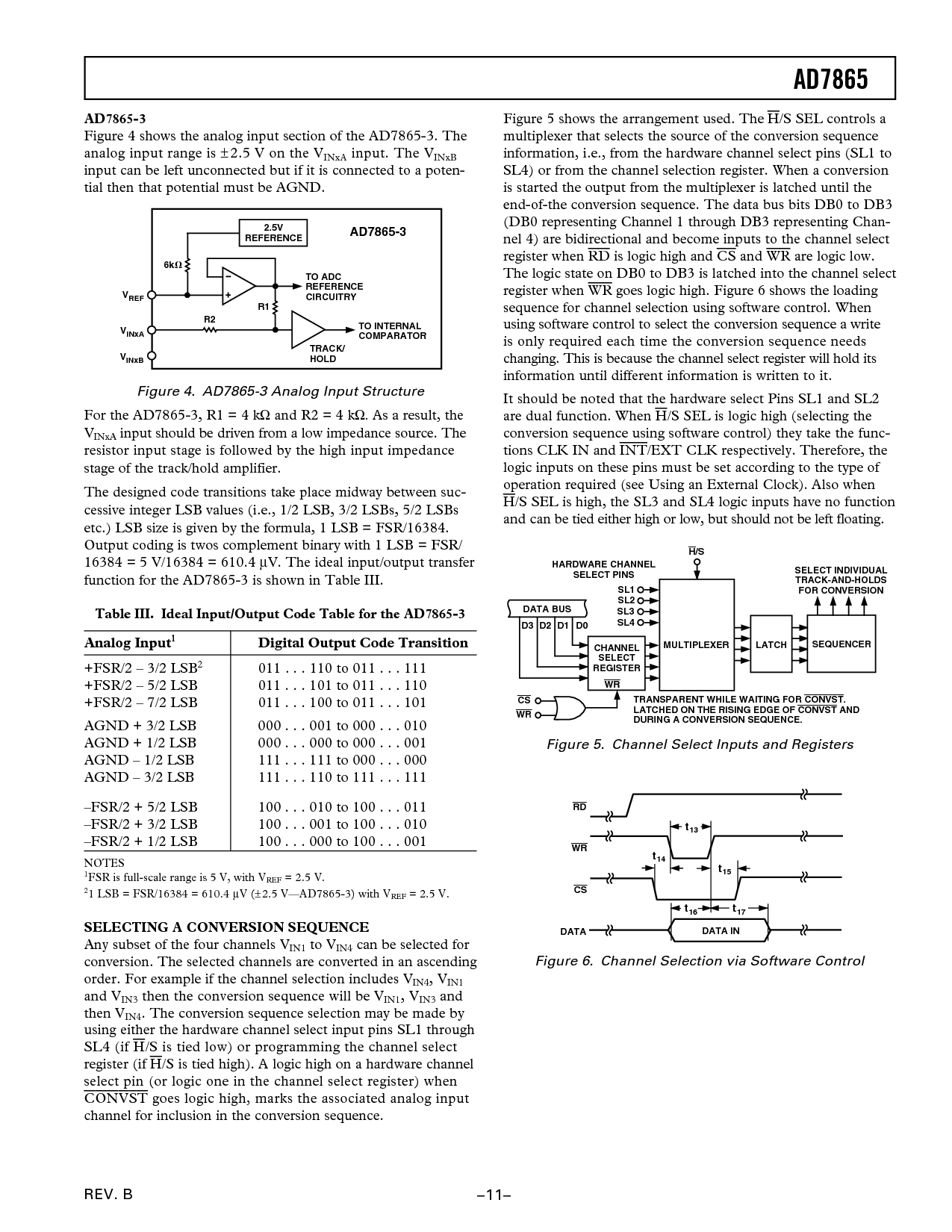

图示 5 显示 这 arrangement 使用. 这

H

/s sel 控制 一个

多路调制器 那 选择 这 源 的 这 转换 sequence

信息, i.e., 从 这 硬件 频道 选择 管脚 (sl1 至

sl4) 或者 从 这 频道 选择 寄存器. 当 一个 转换

是 started 这 输出 从 这 多路调制器 是 latched 直到 这

终止-的-这 转换 sequence. 这 数据 总线 位 db0 至 db3

(db0 representing 频道 1 通过 db3 representing chan-

nel 4) 是 双向的 和 变为 输入 至 这 频道 选择

寄存器 当

RD

是 逻辑 高 和

CS

和

WR

是 逻辑 低.

这 逻辑 状态 在 db0 至 db3 是 latched 在 这 频道 选择

寄存器 当

WR

变得 逻辑 高. 图示 6 显示 这 加载

sequence 为 频道 选择 使用 软件 控制. 当

使用 软件 控制 至 选择 这 转换 sequence 一个 写

是 仅有的 必需的 各自 时间 这 转换 sequence needs

changing. 这个 是 因为 这 频道 选择 寄存器 将 支撑 它的

信息 直到 不同的 信息 是 写 至 它.

它 应当 是 指出 那 这 硬件 选择 管脚 sl1 和 sl2

是 双 函数. 当

H

/s sel 是 逻辑 高 (selecting 这

转换 sequence 使用 软件 控制) 它们 引领 这 func-

tions clk 在 和

INT

/ext clk 各自. 因此, 这

逻辑 输入 在 这些 管脚 必须 是 设置 符合 至 这 类型 的

运作 必需的 (看 使用 一个 外部 时钟). 也 当

H

/s sel 是 高, 这 sl3 和 sl4 逻辑 输入 有 非 函数

和 能 是 系 也 高 或者 低, 但是 应当 不 是 left floating.

数据 总线

D0D1D2D3

WR

CS

WR

频道

选择

寄存器

SL1

SL2

SL3

SL4

硬件 频道

选择 管脚

H

/s

transparent 当 waiting 为

CONVST

.

latched 在 这 rising 边缘 的

CONVST

和

在 一个 转换 sequence.

多路调制器 获得

SEQUENCER

选择 单独的

追踪-和-holds

为 转换

图示 5. 频道 选择 输入 和 寄存器

RD

WR

CS

数据

t

16

t

17

t

14

t

15

数据 在

t

13

图示 6. 频道 选择 通过 软件 控制