管脚 描述

V

REF

在 (1):

这 V

REF

在 管脚 提供 这 涉及 为 这

相似物 输入 信号. 这个 管脚 应当 是 片面的 在 half 的

这 供应 电压, V

DD

, 作 显示 在

图示 1

和

图示

6

.

输出 (2):

这 attenuated 相似物 输出 信号 comes 从

这个 管脚.

地 (3):

这 地 管脚 references 这 数字的 输入 信号

和 是 这 更小的 电压 涉及 为 这 ic. 典型地 这个

管脚 将 是 labeled “V

SS

” 但是 这 地面 涉及 为

这 数字的 逻辑 输入 控制 是 系 至 这个 一样 要点. 和

一个 高等级的 管脚-计数 那里 将 一般地 是 独立的 管脚

为 这些 功能; V

SS

和 逻辑 地面. 它 是 将

那 这 LM1971 总是 是 运作 使用 一个 单独的 volt-

age 供应 配置, 为 这个 管脚 3 (地) 应当 al-

方法 是 在 系统 地面. 如果 一个 双极 或者 分割-供应 con-

figuration 是 desired, 水平的 shifting 电路系统 是 需要 为

这 数字的 逻辑 控制 管脚 作 它们 将 是 关联

通过 管脚 3 这个 将 是 在 这 负的 供应. 它 是

高级地 推荐, 不管怎样, 那 这 LM1971 是 使用

在 一个 单极的 或者 单独的-供应 配置.

加载 (4):

这 加载 输入 accepts 一个 TTL 或者 CMOS 水平的

信号. 这个 是 这 使能 管脚 的 这 设备, 准许 数据

至 是 clocked 在 当 这个 输入 是 低 (0v). 这 地 管脚

是 这 涉及 为 这个 信号.

数据 (5):

这 数据 输入 accepts 一个 TTL 或者 CMOS 水平的

信号. 这个 管脚 是 使用 至 接受 串行 数据 从 一个 微观的-

控制 那 将 是 latched 和 解码 至 改变 这

channel’s attenuation 水平的. 这 地 管脚 是 这 涉及

为 这个 信号.

时钟 (6):

这 时钟 输入 accepts 一个 TTL 或者 CMOS

水平的 信号. 这 时钟 输入 是 使用 至 加载 数据 在 这

内部的 变换 寄存器 在 这 rising 边缘 的 这 输入 时钟

波形. 这 地 管脚 是 这 涉及 为 这个 信号.

V

DD

(7):

这 积极的 电压 供应 应当 是 放置 至

这个 管脚.

在 (8):

这 相似物 输入 信号 应当 是 放置 至 这个

管脚.

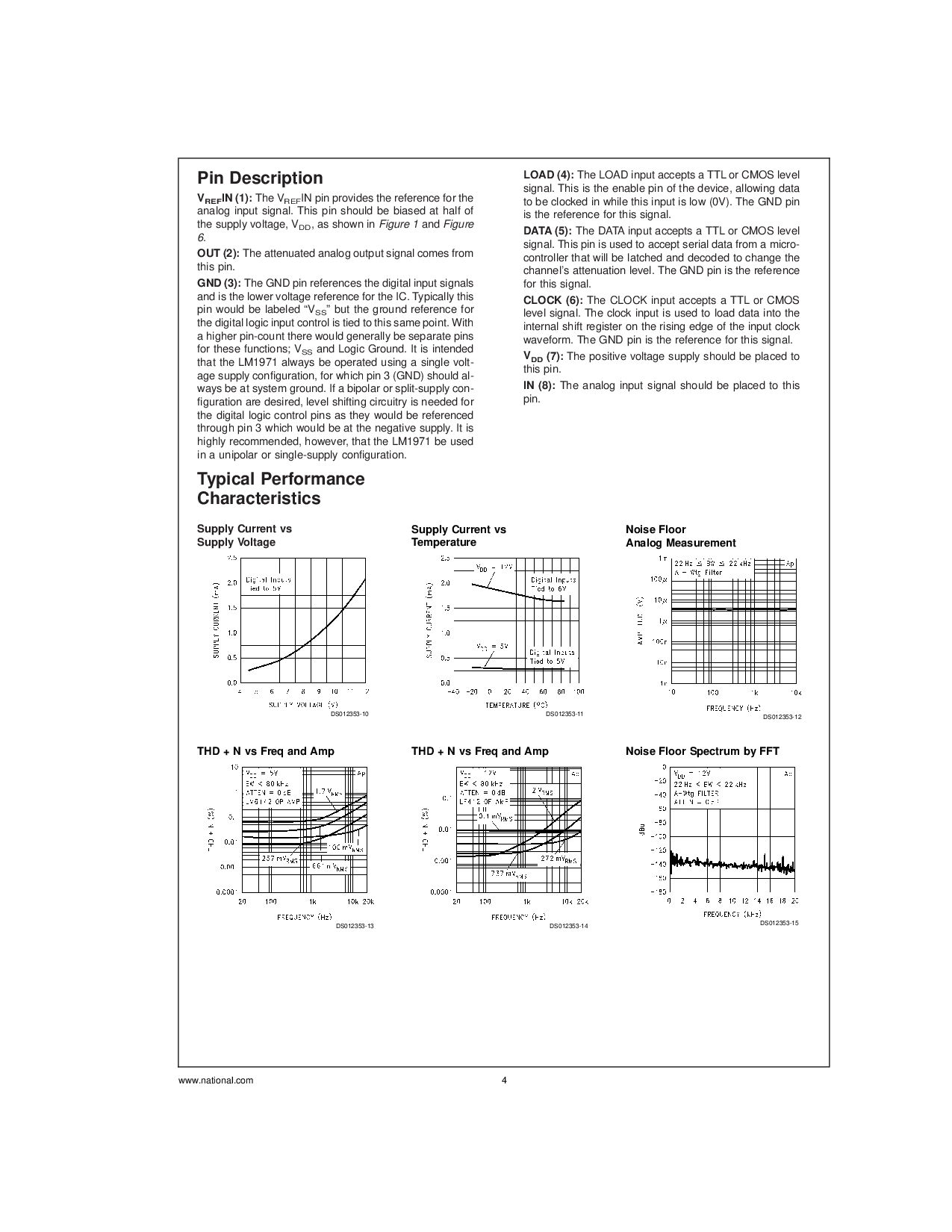

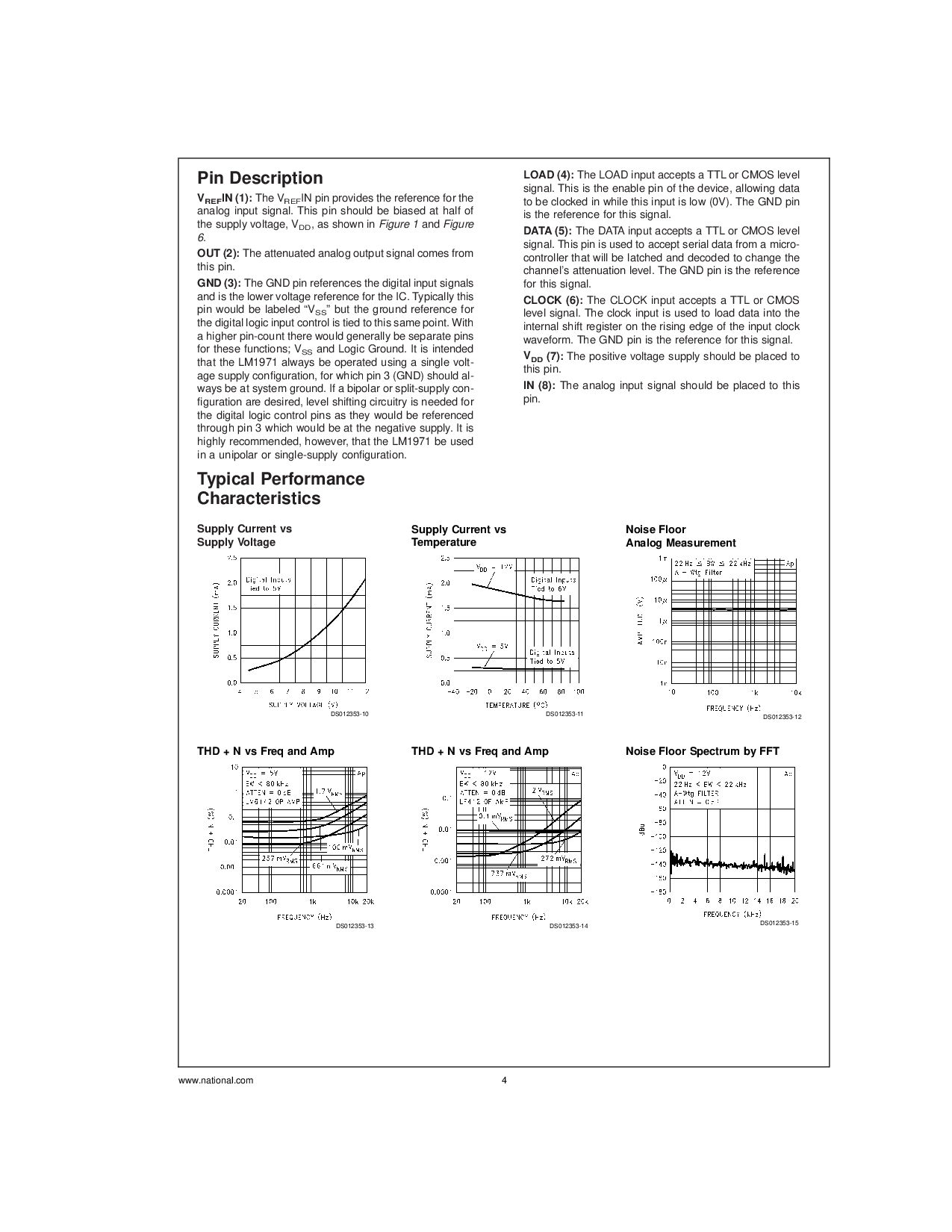

典型 效能

特性

供应 电流 vs

供应 电压

ds012353-10

供应 电流 vs

温度

ds012353-11

噪音 Floor

相似物 度量

ds012353-12

THD+NvsFreq 和 放大

ds012353-13

THD+NvsFreq 和 放大

ds012353-14

噪音 Floor Spectrum 用 FFT

ds012353-15

www.国家的.com 4