CY7C4255

CY7C4265

8

注释:

16. 这 clocks (rclk, wclk) 能 是 自由-运动 在 重置.

17. 之后 重置, 这 输出 将 是 低 如果 oe

= 0 和 三-状态 如果 oe= 1.

18. 当 t

SKEW2

>最小 规格, t

FRL

(最大) = t

CLK

+ t

SKEW2

. 当 t

SKEW2

< 最小 规格, t

FRL

(最大) = 也 2*t

CLK

+ t

SKEW2

或者 t

CLK

+ t

SKEW2

.

这 latency 定时 应用 仅有的 在 这 empty boundary (ef= 低).

19. 这 第一 文字 是 有这 循环 之后 ef变得 高, 总是.

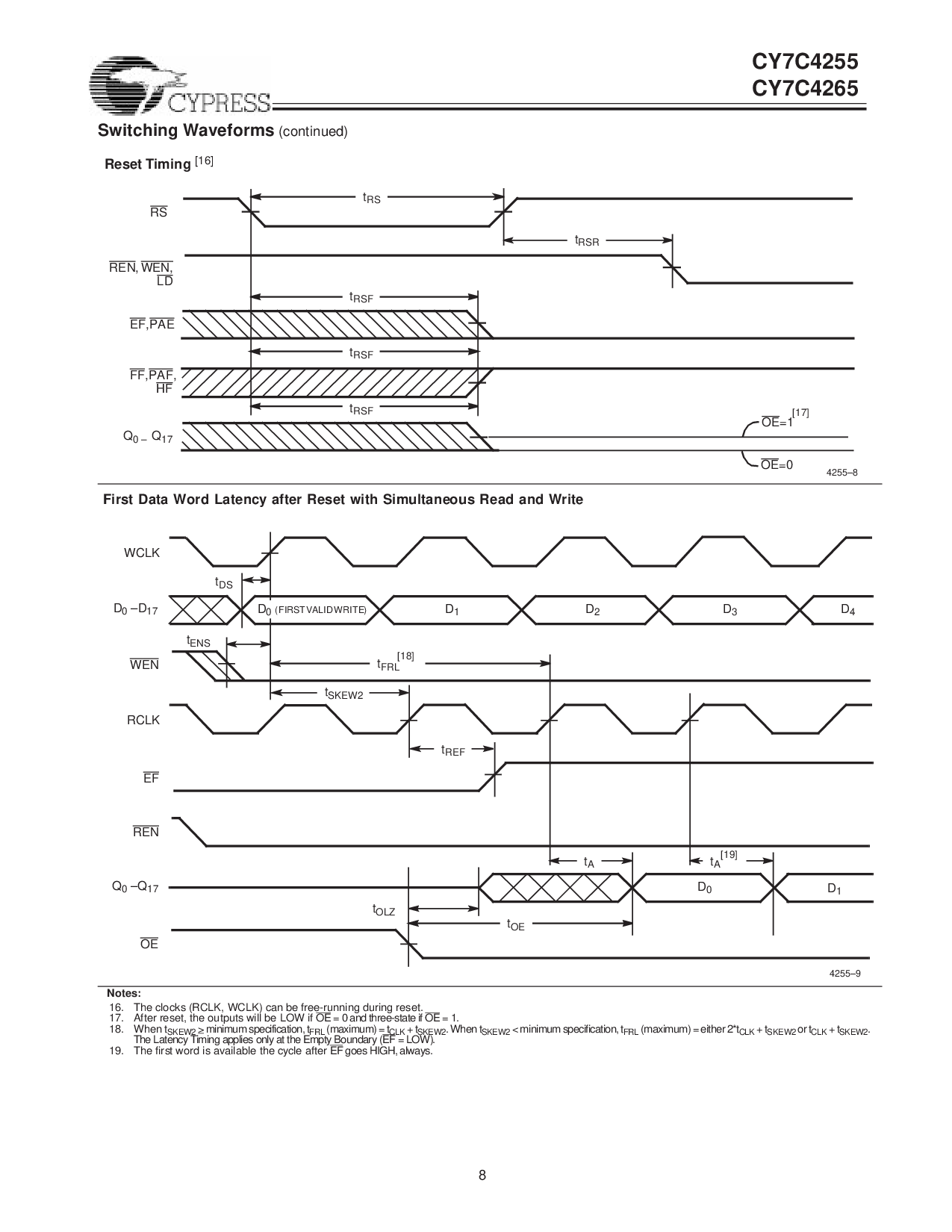

切换 波形

(持续)

重置 定时

t

RS

t

RSR

Q

0–

Q

17

RS

t

RSF

t

RSF

t

RSF

OE=1

OE

=0

REN

, wen,

LD

EF,pae

FF,paf,

HF

4255–8

[16]

[17]

D

0

(第一有效的写)

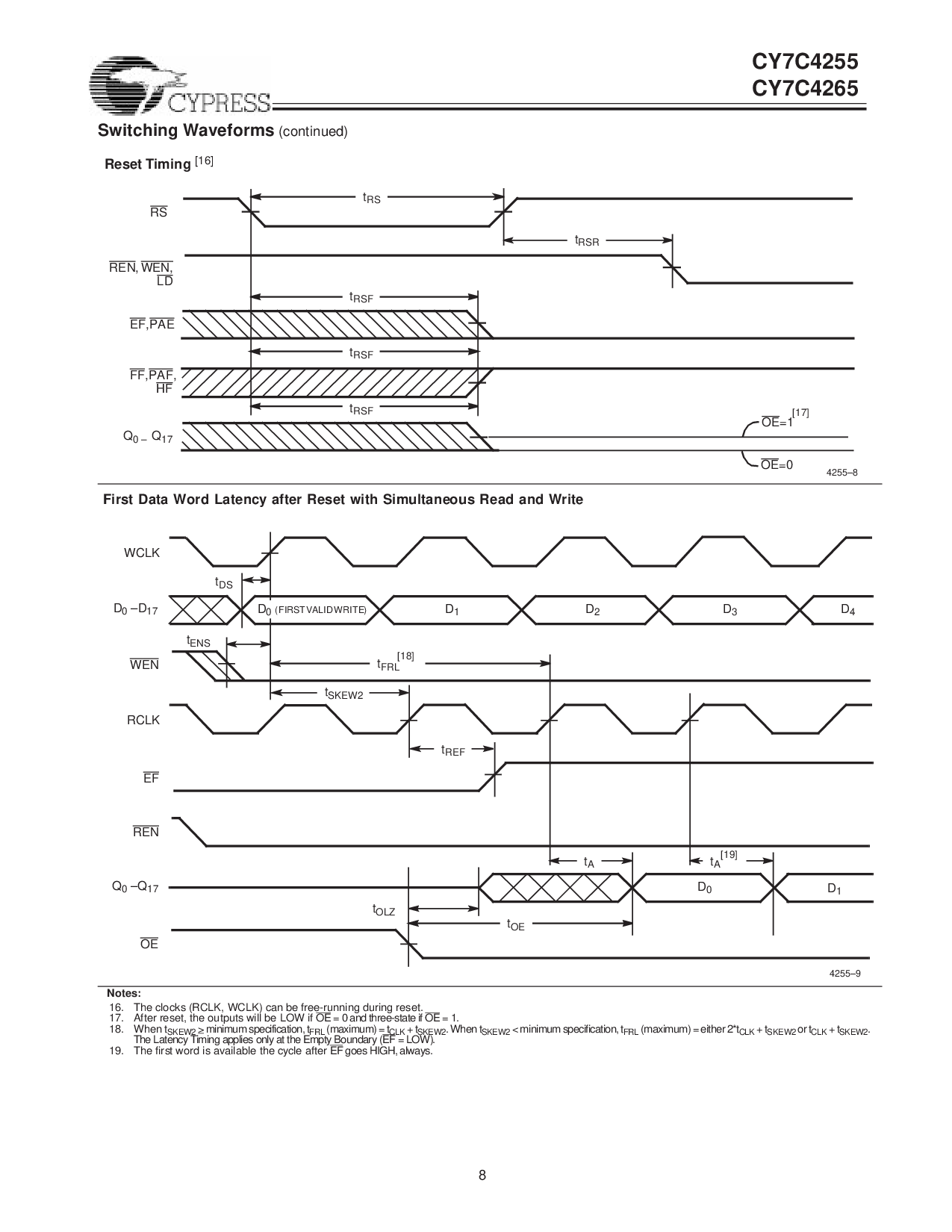

第一 数据 文字 Latency 之后 重置 和 Simultaneous 读 和 写

t

SKEW2

WEN

WCLK

Q

0

–Q

17

EF

REN

OE

t

OE

t

ENS

t

OLZ

t

DS

RCLK

t

REF

t

一个

t

FRL

D

1

D

2

D

3

D

4

D

0

D

1

D

0

–D

17

4255–9

t

一个

[18]

[19]