CY2081

6

注释:

•

如果 管脚 8 是 oe, pd或者 suspend, fill 在 仅有的 一个 值 为

CLKA

•

缓冲 涉及 时钟 是 有 在 所有 输出.

•

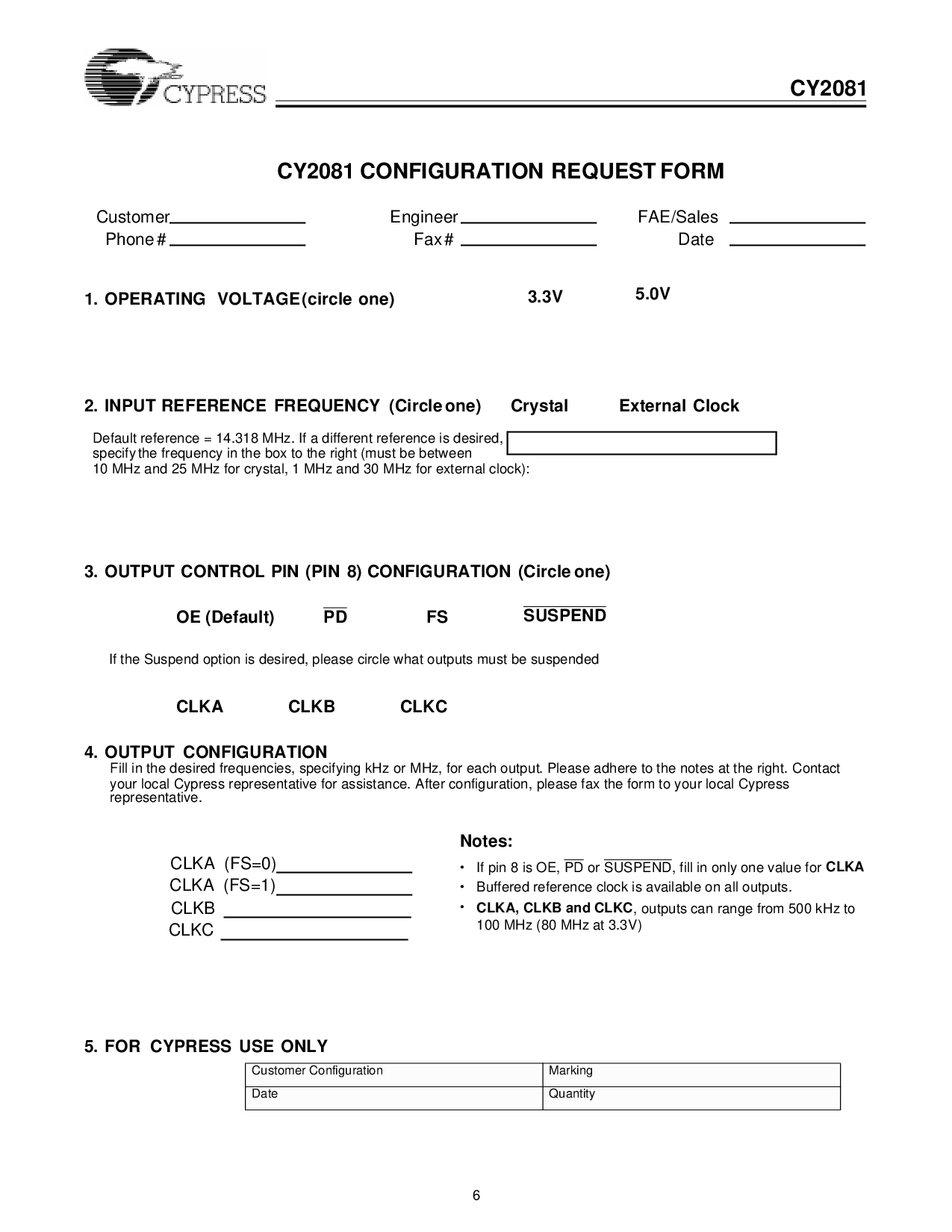

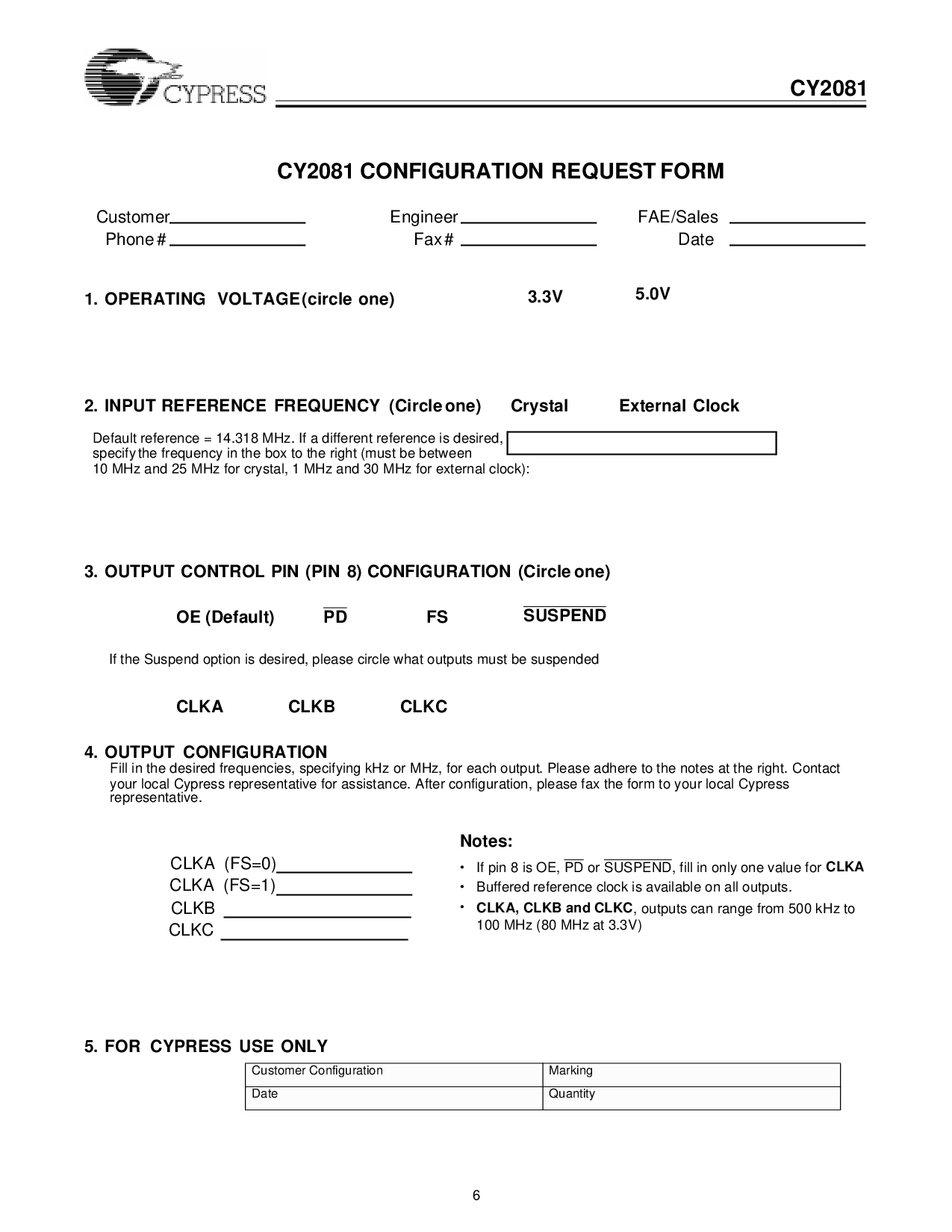

CY2081 配置 要求 表格

1. 运行 电压(circle 一个)

2. 输入 涉及 频率 (circle 一个)

3.3v

5.0v

Default 涉及 = 14.318 mhz. 如果 一个 不同的 涉及 是 desired,

具体说明 这 频率 在 这 盒 至 这 正确的 (必须 是 在

10 MHz 和 25 MHz 为 结晶, 1 MHz 和 30 MHz 为 外部 时钟):

4. 输出 配置

CLKB

CLKC

Fill 在 这 desired 发生率, specifying kHz 或者 mhz, 为 各自 输出. 请 adhere 至 这 注释 在 这 正确的. 联系

your local Cypress 代表 为 帮助. 之后 配置, 请 传真 这 表格 至 your local Cypress

结晶 外部 时钟

5. 为 CYPRESS 使用 仅有的

客户 Engineer fae/销售

Phone # 传真

# 日期

3. 输出 控制 管脚 (管脚 8) 配置 (circle 一个)

CLKA

(fs=0)

CLKA

(fs=1)

oe (default) PD

FS

SUSPEND

如果 这 Suspend 选项 是 desired, 请 circle what 输出 必须 是 suspended

CLKA CLKB CLKC

代表.

客户 配置 标记

日期 Quantity

clka, clkb 和 clkc

, 输出 能 范围 从 500 khz 至

100 mhz (80 mhz 在 3.3v)