低-费用 三-pll 时钟 发生器

CY2081

Cypress 半导体 公司

• 3901 北 第一 街道 • San Jose • ca 95134 • 408-943-2600

九月 1995 - 修订 jul

y1996

特性

• 工厂-非易失存储器 configurable 为 快 有效性 和

prototyping.

• 一般 目的 时钟 synthesizer 为 所有 产品

– 此类 作 modems, disk 驱动, cd-只读存储器 驱动, video

cd 播放机, games, 设置-顶 boxes, data/telecommuni-

cations, 等

• 三 独立 configurable 时钟 输出

• 输出 ranging 从 500 khz 至 100 mhz (5v) 和 向上

至 80 mhz 为 3.3v 运作

• configurable 输出 控制 管脚 (管脚 8) 能 是 使用 作

一个 输出 使能, 电源-向下, suspend 或者 选择 线条.

• 阶段-锁 循环 振荡器 输入 获得 从 exter-

nal 结晶 (10 mhz 至 25 mhz) 或者 外部 涉及

时钟 (1 mhz 至 30 mhz)

• 3.3v 或者 5v 运作 (工厂 配置)

• 8-管脚 150-mil 包装 achieves 最小 footprint

为 空间-核心的 产品

• sophisticated 内部的 循环 过滤 需要 非 外部

组件 或者 制造 tweaks 作 commonly re-

quired 和 外部 过滤

函数的 描述

这 cy2081 是 一个 一般-目的 时钟 synthesizer 设计

为 使用 在 产品 此类 作 modems, disk 驱动, cd-只读存储器

驱动, video cd 播放机, games, 设置-顶 boxes 和 data/tele-

communications. 这个 设备 提供 三 configurable 时钟

输出 在 一个 8-管脚 150-mil soic 包装 和 能 是 config-

ured 至 运作 止 也 一个 3.3v 或者 5v 电源 供应. 这

在-碎片 涉及 振荡器 是 设计 为 10 mhz 至 25 mhz

crystals. alternatively, 一个 涉及 时钟 在 1 mhz 和

30 mhz 能 是 使用.

这 cy2081 也 特性 一个 输出 控制 管脚 (管脚 8) 这个

能 是 配置 作 一个 输出 使能, 电源 向下, frequen-

cy 选择, 或者 suspend 输入. 这个 给 这 用户 这 能力 至

三-状态 这 输出, 电源 向下 这 设备, 改变 这

clka 输出 频率 在 运作, 或者 suspend 任何 的

这 输出. asserting 这 pd

输入 将 结果 在 所有 这 plls

和 这 输出 正在 shut 向下. 这 plls 将 有 至 re-锁

当 这 pd

输入 是 deasserted.

这 cy2081 输出 三 clocks: clka, clkb, 和 clkc,

谁的 发生率 能 possess 任何 值 在里面 这 指定

范围. additionally, 这 涉及 频率 能 是 得到

在 任何 输出. custom 配置 和 用户-定义 fea-

tures 和 发生率 能 是 得到 用 filling 输出 这 custom

配置 表格 located 在 这 后面的 的 这个 数据 薄板 和

contacting your local cypress 代表.

这 cy2081 能 替代 多样的 metal 能 oscillators

(mco) 在 一个 同步的 系统, 供应 费用 和 板

空间 savings 至 manufacturers. hence, 这个 设备 是 ideally

suited 为 产品 那 需要 多样的, 精确, 和 sta-

ble clocks synthesized 从 低-费用 发生器 在 小 包装-

ages. 一个 hard disk 驱动 是 一个 例子 的 此类 一个 应用.

在 这个 情况, clka 驱动 这 pll 在 这 读 控制, 当

clkb 和 clkc 驱动 这 mcu 和 有关联的 sequencers.

考虑 使用 这 cy2291, cy2292, 或者 cy2907 为 applica-

tions 那 需要 更多 比 三 输出 clocks.

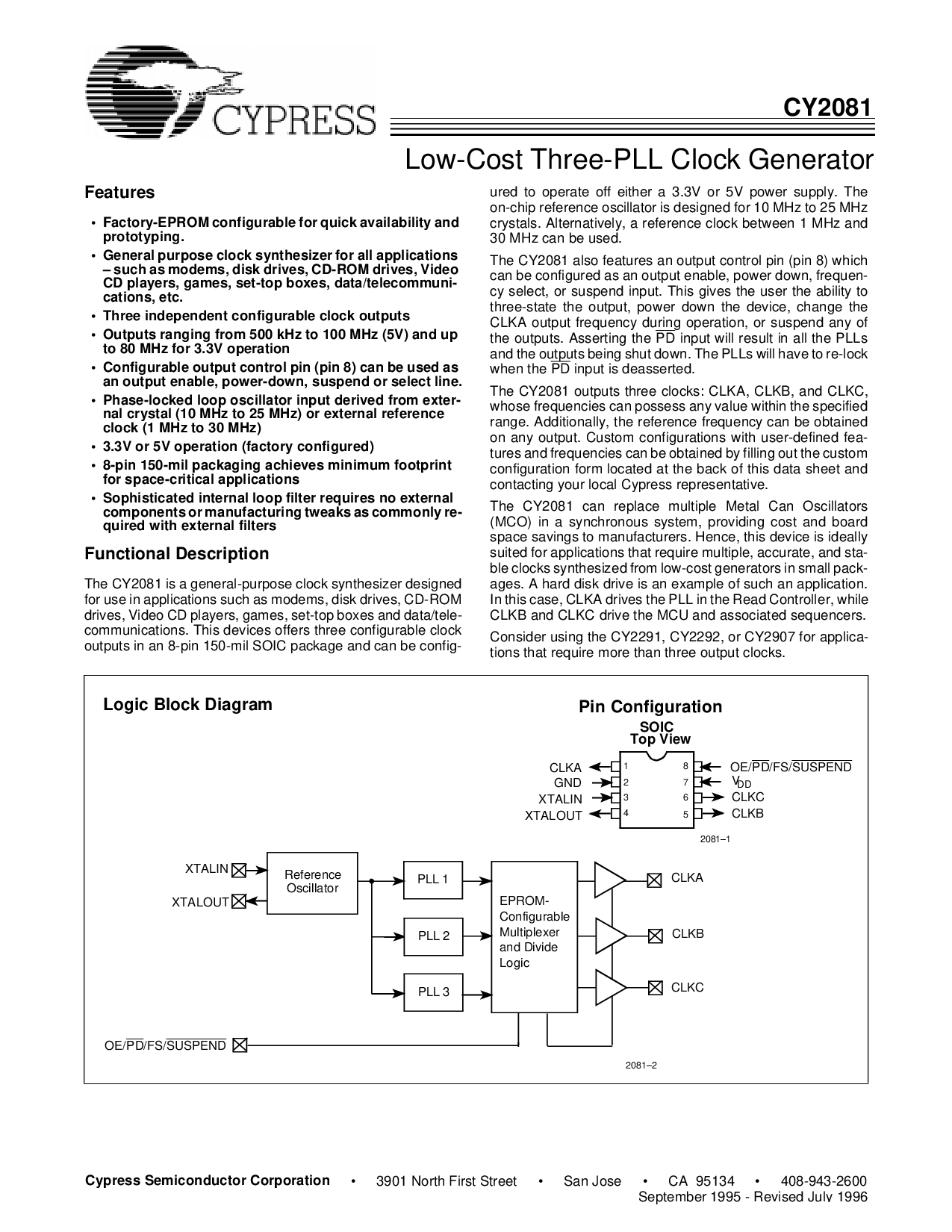

管脚 配置

2081–1

1

2

3

4

5

8

7

6

CLKA

地

XTALIN

XTALOUT

V

DD

CLKC

CLKB

SOIC

顶 视图

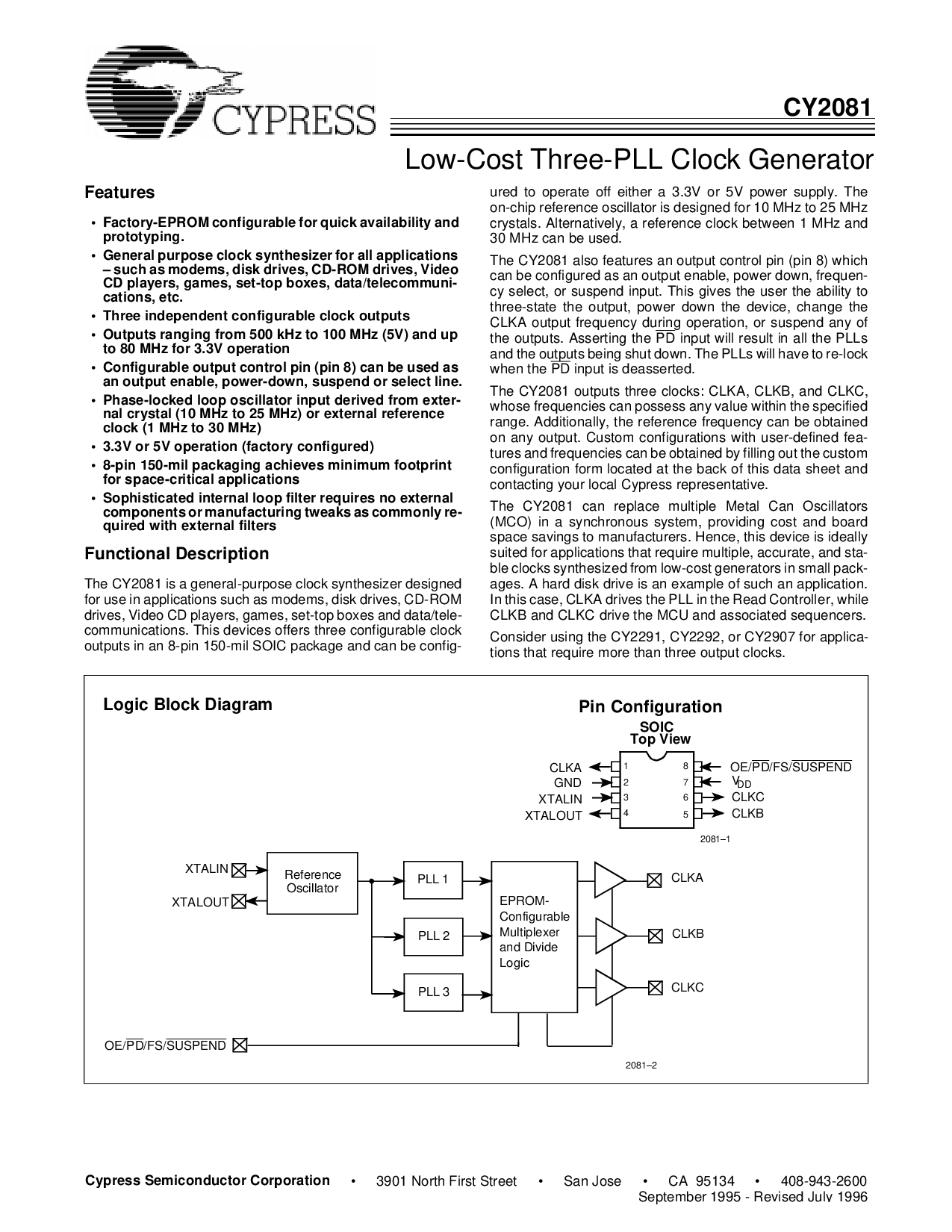

逻辑 块 图解

XTALOUT

XTALIN

涉及

振荡器

PLL

1

CLKA

2081–2

CLKB

CLKC

非易失存储器-

Configurable

多路调制器

和 分隔

逻辑

PLL 2

PLL

3

oe/pd/fs/suspend

oe/pd/fs/suspend