飞利浦 半导体 产品 规格

74LV4066四方形 bilateral switches

1998 六月 23

5

V

高

(从 使能 输入)

I

是

nZ

地

nY

V

是

= 0 至 v

CC

– 地

SV01673

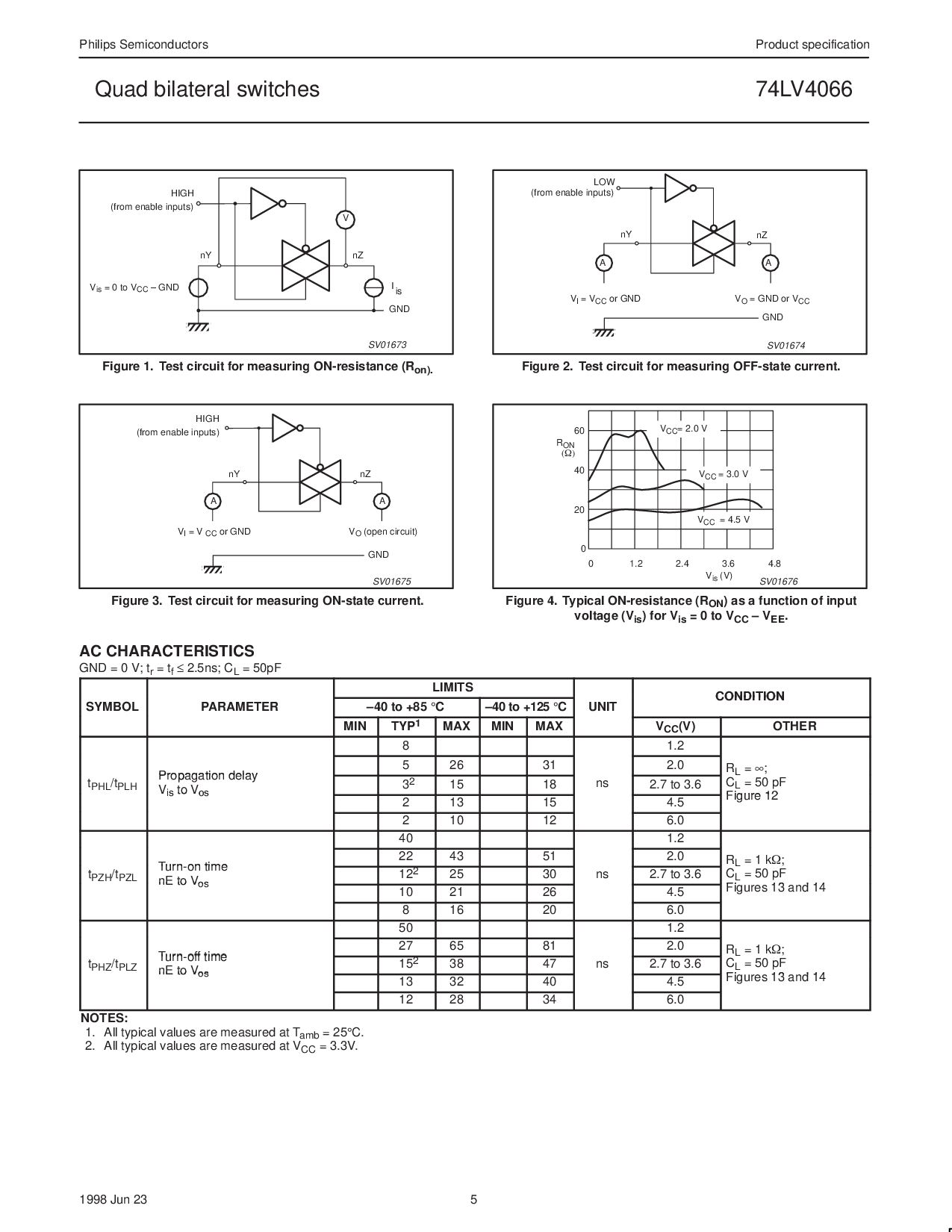

图示 1.

测试 电路 为 测量 在-阻抗 (r

在).

一个

低

(从 使能 输入)

nZ

地

nY

V

I

= v

CC

或者 地 V

O

= 地 或者 v

CC

一个

SV01674

图示 2.

测试 电路 为 测量 止-状态 电流.

一个

高

(从 使能 输入)

nZ

地

nY

V

I

= v

CC

或者 地 V

O

(打开 电路)

一个

SV01675

图示 3.

测试 电路 为 测量 在-状态 电流.

0

V

CC

= 2.0 v

V

CC

= 3.0 v

V

CC

= 4.5 v

0 1.2 2.4 3.6

V

是

(v)

4.8

20

40

60

R

在

(

)

SV01676

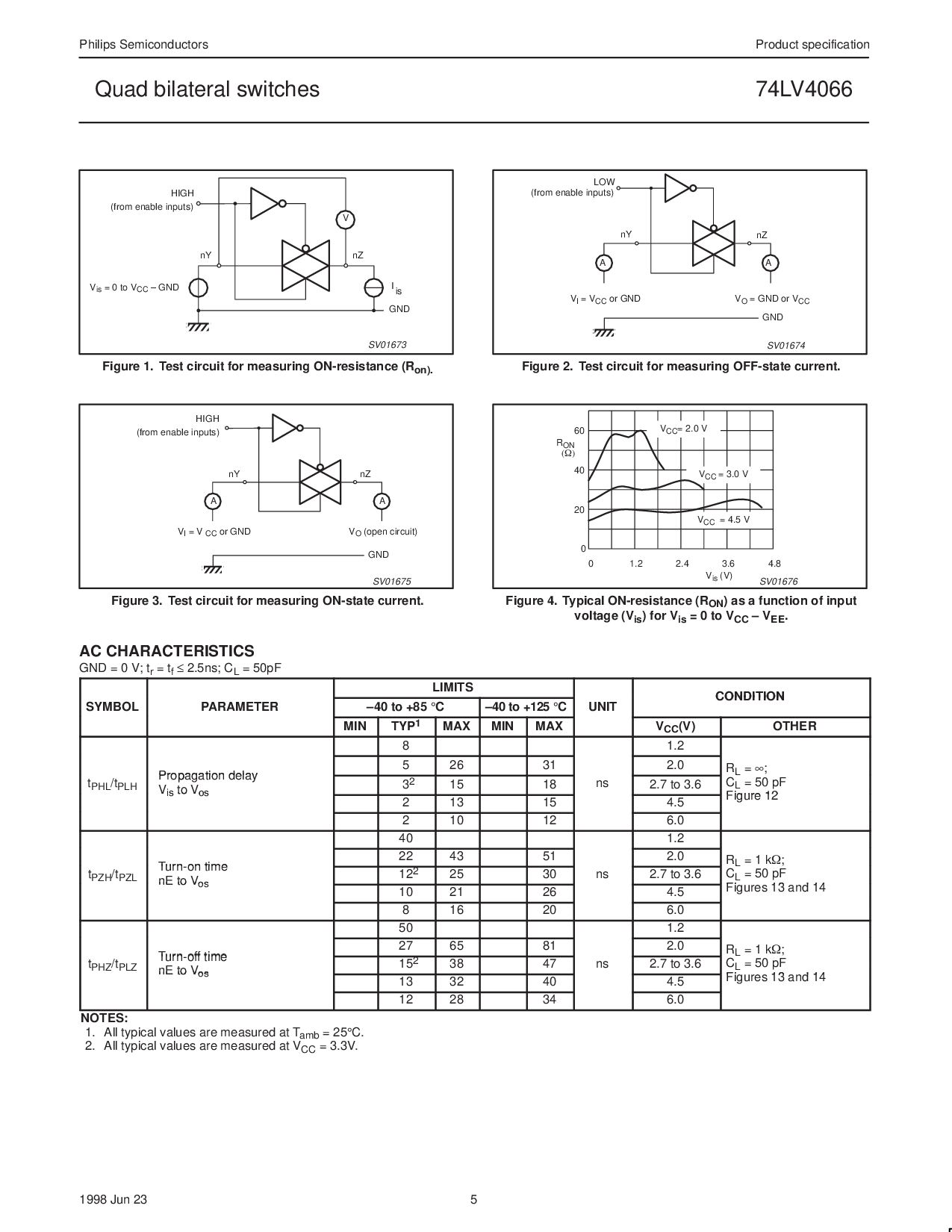

图示 4.

典型 在-阻抗 (r

在

) 作 一个 函数 的 输入

电压 (v

是

) 为 v

是

= 0 至 v

CC

– v

EE

.

交流 特性

地 = 0 v; t

r

= t

f

≤

2.5ns; c

L

= 50pf

限制

情况

标识 参数

–40 至 +85

°

C –40 至 +125

°

C

单位

情况

最小值 典型值

1

最大值 最小值 最大值 V

CC

(v) 其它

8 1.2

传播 延迟

5 26 31 2.0

R

L

=

∞

;

t

PHL

/t

PLH

传播 延迟

V

是

至 v

os

3

2

15 18

ns

2.7 至 3.6

L

C

L

= 50 pf

图示 12

V

是

至 v

os

2 13 15 4.5

图示 12

2 10 12 6.0

40 1.2

转变 在 时间

22 43 51 2.0

R

L

= 1 k

;

t

PZH

/t

PZL

转变-在 时间

nE 至 V

os

12

2

25 30 ns 2.7 至 3.6

L

C

L

= 50 pf

Fi 13 d 14

nE至 v

os

10 21 26 4.5

Figures 13 一个d 14

8 16 20 6.0

50 1.2

转变 止 时间

27 65 81 2.0

R

L

= 1 k

;

t

PHZ

/t

PLZ

转变-止 时间

nE 至 V

os

15

2

38 47 ns 2.7 至 3.6

L

C

L

= 50 pf

Fi 13 d 14

nE至 v

os

13 32 40 4.5

Figures 13 一个d 14

12 28 34 6.0

注释:

1. 所有 典型 值 是 量过的 在 t

amb

= 25

°

c.

2. 所有 典型 值 是 量过的 在 v

CC

= 3.3v.