AD7890

–5–

rev. 一个

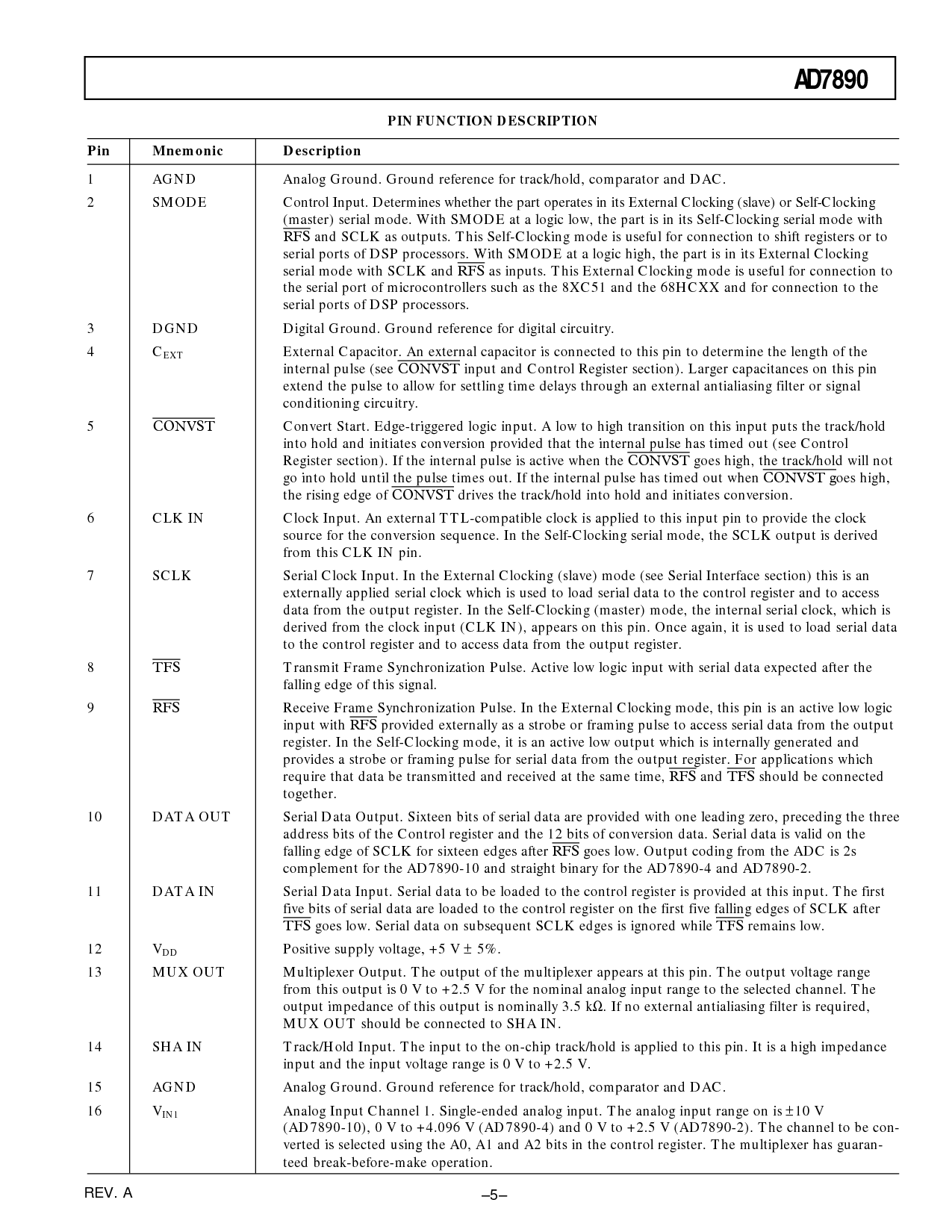

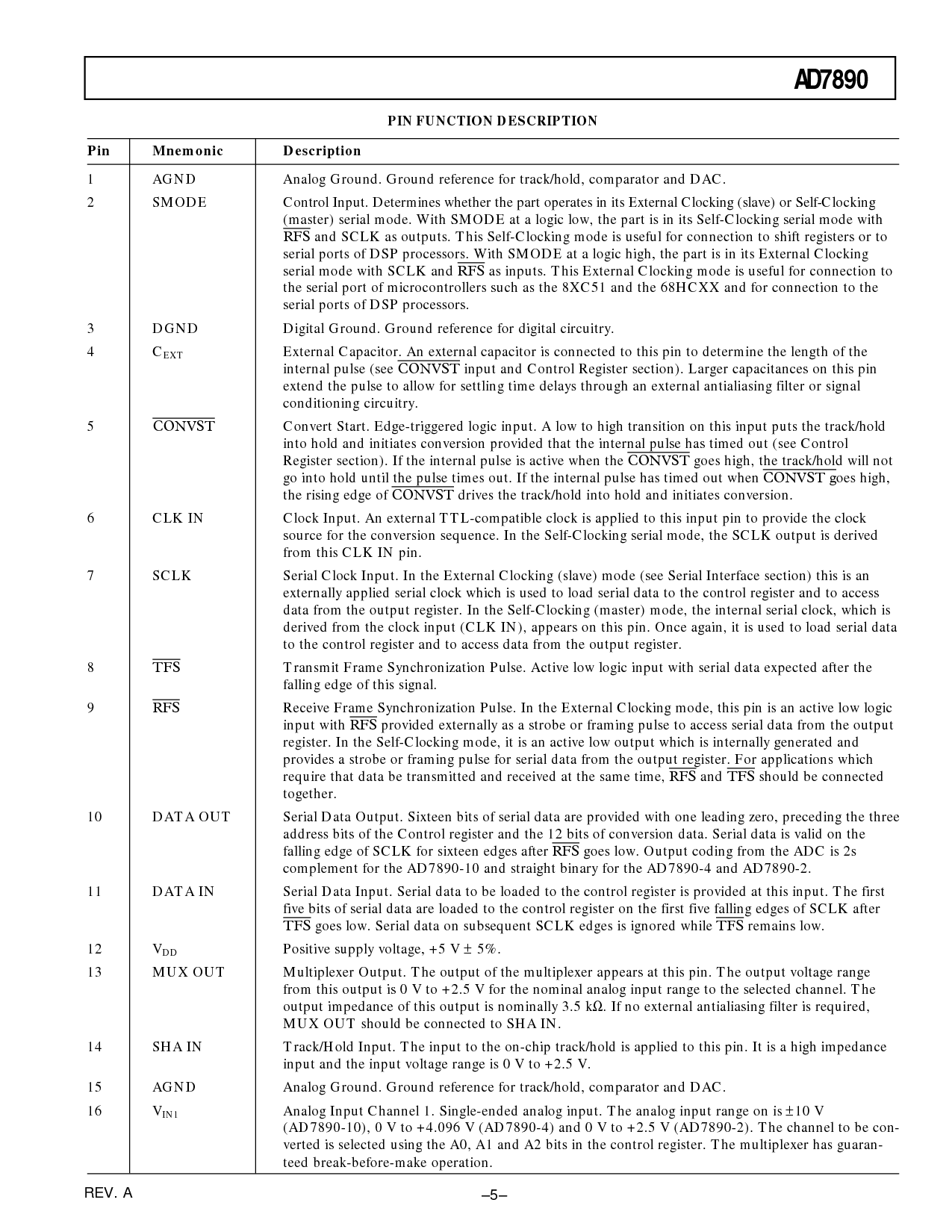

管脚 函数 描述

管脚 Mnemonic 描述

1 AGND 相似物 地面. 地面 涉及 为 追踪/支撑, 比较器 和 dac.

2 SMODE 控制 输入. 确定 whether 这 部分 运作 在 它的 外部 clocking (从动装置) 或者 自-Clocking

(主控) 串行 模式. 和 smode 在 一个 逻辑 低, 这 部分 是 在 它的 自-clocking 串行 模式 和

RFS

和 sclk 作 输出. 这个 自-clocking 模式 是 有用的 为 连接 至 变换 寄存器 或者 至

串行 端口 的 dsp processors. 和 smode 在 一个 逻辑 高, 这 部分 是 在 它的 外部 clocking

串行 模式 和 sclk 和

RFS

作 输入. 这个 外部 clocking 模式 是 有用的 为 连接 至

这 串行 端口 的 微控制器 此类 作 这 8xc51 和 这 68hcxx 和 为 连接 至 这

串行 端口 的 dsp processors.

3 DGND 数字的 地面. 地面 涉及 为 数字的 电路系统.

4C

EXT

外部 电容. 一个 外部 电容 是 连接 至 这个 管脚 至 决定 这 长度 的 这

内部的 脉冲波 (看

CONVST

输入 和 控制 寄存器 部分). 大 capacitances 在 这个 管脚

扩展 这 脉冲波 至 准许 为 安排好 时间 延迟 通过 一个 外部 消除走样 过滤 或者 信号

conditioning 电路系统.

5

CONVST

转变 开始. 边缘-triggered 逻辑 输入. 一个 低 至 高 转变 在 这个 输入 puts 这 追踪/支撑

在 支撑 和 initiates 转换 提供 那 这 内部的 脉冲波 有 安排时间 输出 (看 控制

寄存器 部分). 如果 这 内部的 脉冲波 是 起作用的 当 这

CONVST

变得 高, 这 追踪/支撑 将 不

go 在 支撑 直到 这 脉冲波 时间 输出. 如果 这 内部的 脉冲波 有 安排时间 输出 当

convst g

oes 高,

这 rising 边缘 的

CONVST

驱动 这 追踪/支撑 在 支撑 和 initiates 转换.

6 clk 在 时钟 输入. 一个 外部 ttl-兼容 时钟 是 应用 至 这个 输入 管脚 至 提供 这 时钟

源 为 这 转换 sequence. 在 这 自-clocking 串行 模式, 这 sclk 输出 是 获得

从 这个 clk 在 管脚.

7 SCLK 串行 时钟 输入. 在 这 外部 clocking (从动装置) 模式 (看 串行 接口 部分) 这个 是 一个

externally 应用 串行 时钟 这个 是 使用 至 加载 串行 数据 至 这 控制 寄存器 和 至 进入

数据 从 这 输出 寄存器. 在 这 自-clocking (主控) 模式, 这 内部的 串行 clock, 这个 是

获得 从 这 时钟 输入 (clk 在), 呈现 在 这个 管脚. once 又一次, 它 是 使用 至 加载 串行 数据

至 这 控制 寄存器 和 至 进入 数据 从 这 输出 寄存器.

8

TFS

transmit 框架 同步 脉冲波. 起作用的 低 逻辑 输入 和 串行 数据 预期的 之后 这

下落 边缘 的 这个 信号.

9

RFS

receive 框架 同步 脉冲波. 在 这 外部 clocking 模式, 这个 管脚 是 一个 起作用的 低 逻辑

输入 和

RFS

提供 externally 作 一个 strobe 或者 framing 脉冲波 至 进入 串行 数据 从 这 输出

寄存器. 在 这 自-clocking 模式, 它 是 一个 起作用的 低 输出 这个 是 内部 发生 和

提供 一个 strobe 或者 framing 脉冲波 为 串行 数据 从 这 输出 寄存器. 为 产品 这个

需要 那 数据 是 transmitted 和 received 在 这 一样 时间,

RFS

和

TFS

应当 是 连接

一起.

10 数据 输出 串行 数据 输出. 十六 位 的 串行 数据 是 提供 和 一个 leading 零, preceding 这 三

地址 位 的 这 控制 寄存器 和 这 12 位 的 转换 数据. 串行 数据 是 有效的 在 这

下落 边缘 的 sclk 为 十六 edges 之后

RFS

变得 低. 输出 编码 从 这 模数转换器 是 2s

complement 为 这 ad7890-10 和 笔直地 二进制的 为 这 ad7890-4 和 ad7890-2.

11 数据 在 串行 数据 输入. 串行 数据 至 是 承载 至 这 控制 寄存器 是 提供 在 这个 输入. 这 第一

five 位 的 串行 数据 是 承载 至 这 控制 寄存器 在 这 第一 five 下落 edges 的 sclk 之后

TFS

变得 低. 串行 数据 在 subsequent sclk edges 是 ignored 当

TFS

仍然是 低.

12 V

DD

积极的 供应 电压, +5 v

±

5%.

13 mux 输出 多路调制器 输出. 这 输出 的 这 多路调制器 呈现 在 这个 管脚. 这 输出 电压 范围

从 这个 输出 是 0 v 至 +2.5 v 为 这 名义上的 相似物 输入 范围 至 这 选择 频道. 这

输出 阻抗 的 这个 输出 是 nominally 3.5 k

Ω

. 如果 非 外部 消除走样 过滤 是 必需的,

mux 输出 应当 是 连接 至 sha 在.

14 sha 在 追踪/支撑 输入. 这 输入 至 这 在-碎片 追踪/支撑 是 应用 至 这个 pin. 它 是 一个 高 阻抗

输入 和 这 输入 电压 范围 是 0 v 至 +2.5 v.

15 AGND 相似物 地面. 地面 涉及 为 追踪/支撑, 比较器 和 dac.

16 V

IN1

相似物 输入 频道 1. 单独的-结束 相似物 输入. 这 相似物 输入 范围 在 是

±

10 v

(ad7890-10), 0 v 至 +4.096 v (ad7890-4) 和 0 v 至 +2.5 v (ad7890-2). 这 频道 至 是 con-

verted 是 选择 使用 这 a0, a1 和 a2 位 在 这 控制 寄存器. 这 多路调制器 有 guaran-

teed 破裂-在之前-制造 运作.