AD7840

rev. b

–4–

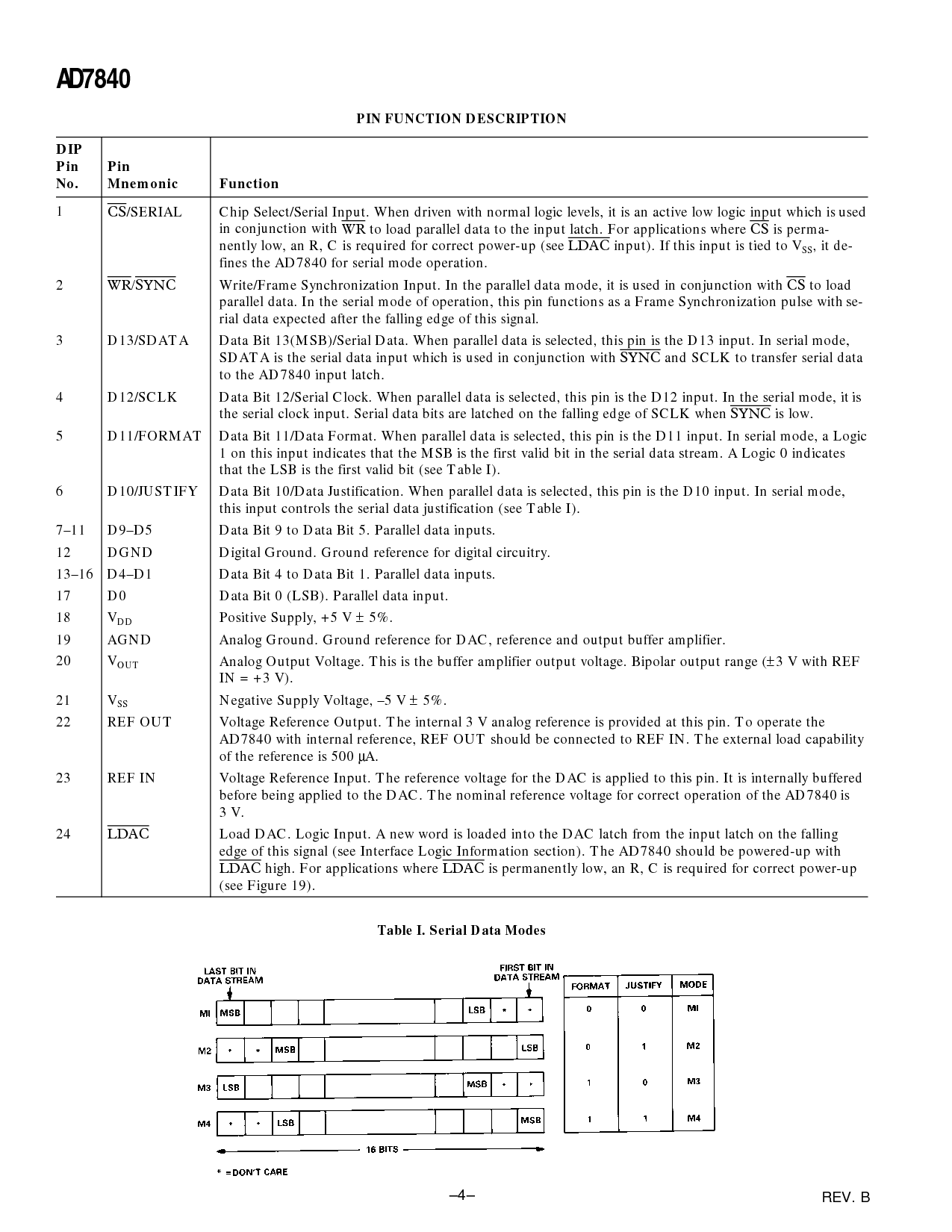

管脚 函数 描述

插件

管脚 管脚

非. Mnemonic 函数

1

CS

/串行 碎片 选择/串行 输入. 当 驱动 和 正常的 逻辑 水平, 它 是 一个 起作用的 低 逻辑 输入 这个 是 使用

在 conjunction 和

WR

至 加载 并行的 数据 至 这 输入 获得. 为 产品 在哪里

CS

是 perma-

nently 低, 一个 r, c 是 必需的 为 准确无误的 电源-向上 (看

LDAC

输入). 如果 这个 输入 是 系 至 v

SS

, 它 de-

fines 这 ad7840 为 串行 模式 运作.

2

wr/同步

写/框架 同步 输入. 在 这 并行的 数据 模式, 它 是 使用 在 conjunction 和

CS

至 加载

并行的 数据. 在 这 串行 模式 的 运作, 这个 管脚 功能 作 一个 框架 同步 脉冲波 和 se-

rial 数据 预期的 之后 这 下落 边缘 的 这个 信号.

3 d13/sdata 数据 位 13(msb)/串行 数据. 当 并行的 数据 是 选择, 这个 管脚 是 这 d13 输入. 在 串行 mode,

sdata 是 这 串行 数据 输入 这个 是 使用 在 conjunction 和

同步

和 sclk 至 转移 串行 数据

至 这 ad7840 输入 获得.

4 d12/sclk 数据 位 12/串行 时钟. 当 并行的 数据 是 选择, 这个 管脚 是 这 d12 输入. 在 这 串行 mode, 它 是

这 串行 时钟 输入. 串行 数据 位 是 latched 在 这 下落 边缘 的 sclk 当

同步

是 低.

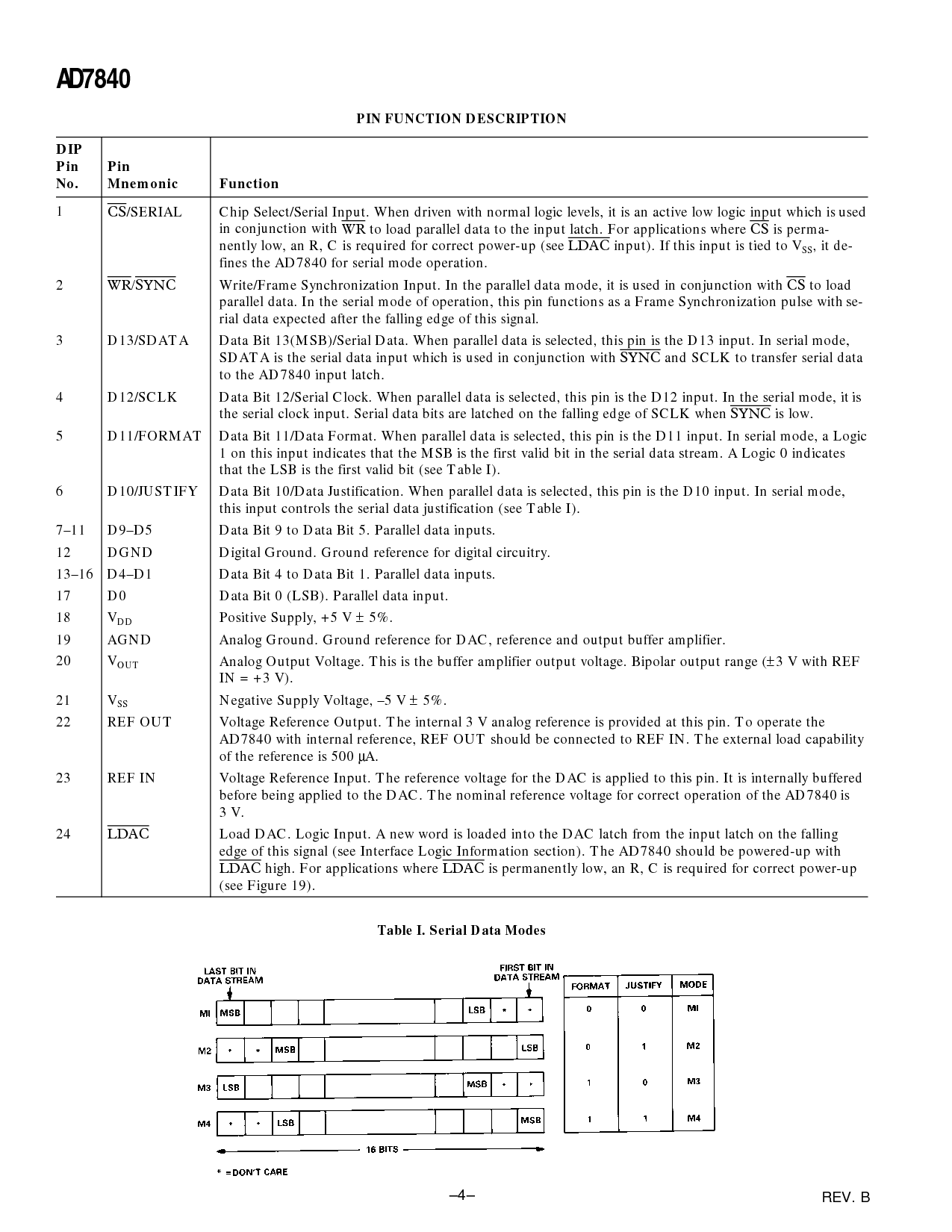

5 d11/format 数据 位 11/数据 format. 当 并行的 数据 是 选择, 这个 管脚 是 这 d11 输入. 在 串行 mode, 一个 逻辑

1 在 这个 输入 indicates 那 这 msb 是 这 第一 有效的 位 在 这 串行 数据 stream. 一个 逻辑 0 indicates

那 这 lsb 是 这 第一 有效的 位 (看 表格 i).

6 d10/justify 数据 位 10/数据 justification. 当 并行的 数据 是 选择, 这个 管脚 是 这 d10 输入. 在 串行 mode,

这个 输入 控制 这 串行 数据 justification (看 表格 i).

7–11 D9–D5 数据 位 9 至 数据 位 5. 并行的 数据 输入.

12 DGND 数字的 地面. 地面 涉及 为 数字的 电路系统.

13–16 D4–D1 数据 位 4 至 数据 位 1. 并行的 数据 输入.

17 D0 数据 位 0 (lsb). 并行的 数据 输入.

18 V

DD

积极的 供应, +5 v

±

5%.

19 AGND 相似物 地面. 地面 涉及 为 dac, 涉及 和 输出 缓存区 放大器.

20 V

输出

相似物 输出 电压. 这个 是 这 缓存区 放大器 输出 电压. 双极 输出 范围 (

±

3 v 和 ref

在 = +3 v).

21 V

SS

负的 供应 电压, –5 v

±

5%.

22 ref 输出 电压 涉及 输出. 这 内部的 3 v 相似物 涉及 是 提供 在 这个 管脚. 至 运作 这

ad7840 和 内部的 涉及, ref 输出 应当 是 连接 至 ref 在. 这 外部 加载 能力

的 这 涉及 是 500

µ

一个.

23 ref 在 电压 涉及 输入. 这 涉及 电压 为 这 dac 是 应用 至 这个 管脚. 它 是 内部 缓冲

在之前 正在 应用 至 这 dac. 这 名义上的 涉及 电压 为 准确无误的 运作 的 这 ad7840 是

3 v.

24

LDAC

加载 dac. 逻辑 输入. 一个 新 文字 是 承载 在 这 dac 获得 从 这 输入 获得 在 这 下落

边缘 的 这个 信号 (看 接口 逻辑 信息 部分). 这 ad7840 应当 是 powered-向上 和

LDAC

高. 为 产品 在哪里

LDAC

是 permanently 低, 一个 r, c 是 必需的 为 准确无误的 电源-向上

(看 图示 19).

表格 i. 串行 数据 模式