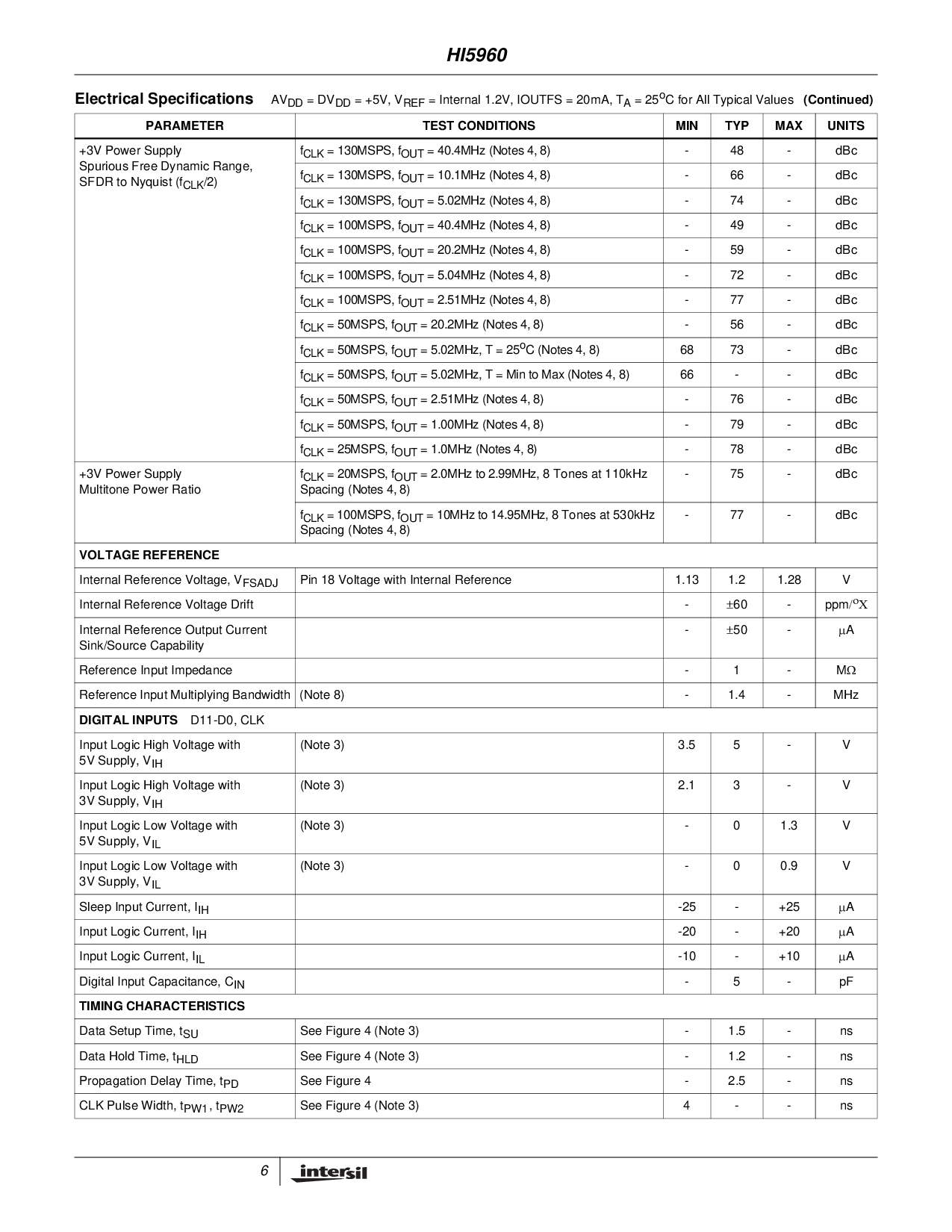

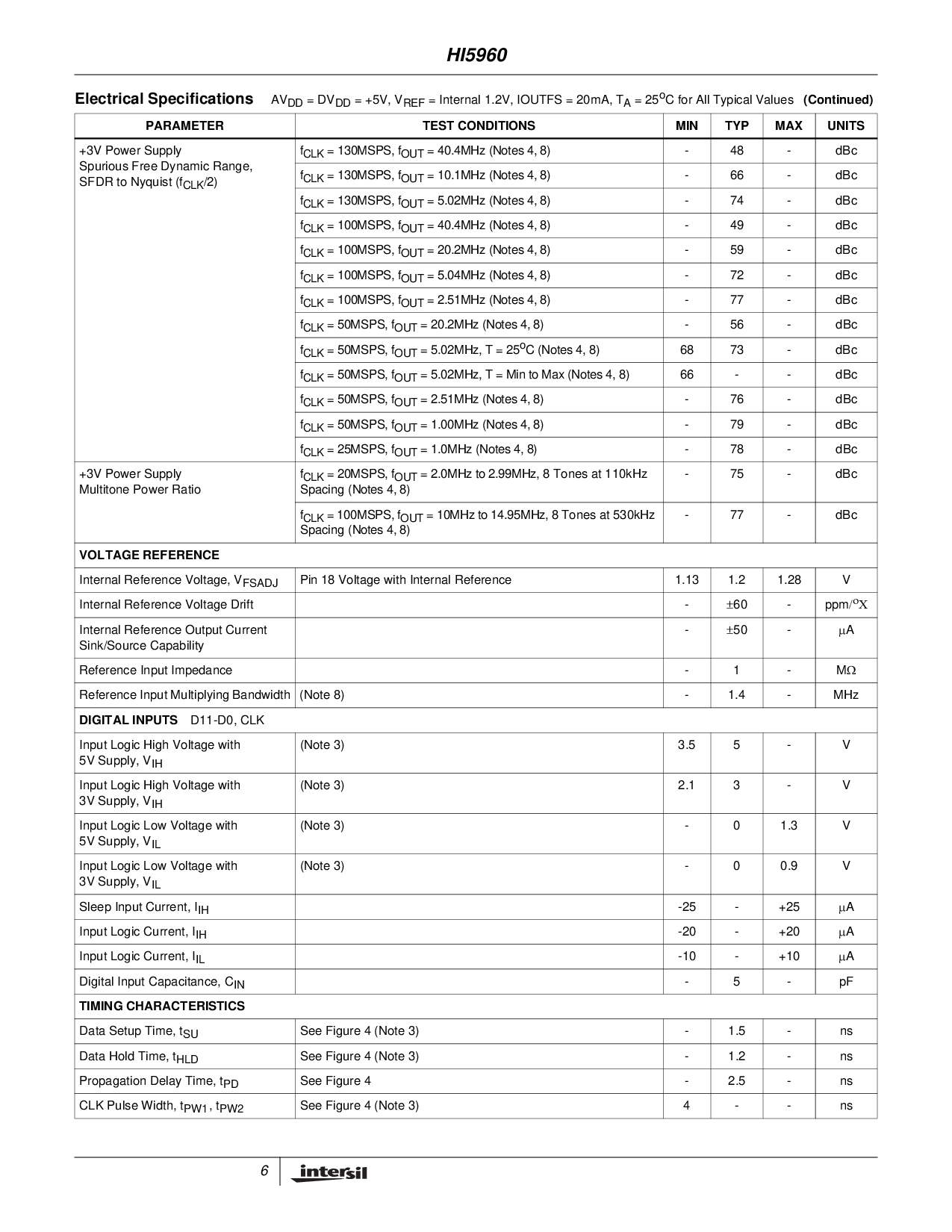

6

+3v 电源 供应

spurious 自由 动态 范围,

sfdr 至 nyquist (f

CLK

/2)

f

CLK

= 130msps, f

输出

= 40.4mhz (注释 4, 8) - 48 - dBc

f

CLK

= 130msps, f

输出

= 10.1mhz (注释 4, 8) - 66 - dBc

f

CLK

= 130msps, f

输出

= 5.02mhz (注释 4, 8) - 74 - dBc

f

CLK

= 100msps, f

输出

= 40.4mhz (注释 4, 8) - 49 - dBc

f

CLK

= 100msps, f

输出

= 20.2mhz (注释 4, 8) - 59 - dBc

f

CLK

= 100msps, f

输出

= 5.04mhz (注释 4, 8) - 72 - dBc

f

CLK

= 100msps, f

输出

= 2.51mhz (注释 4, 8) - 77 - dBc

f

CLK

= 50msps, f

输出

= 20.2mhz (注释 4, 8) - 56 - dBc

f

CLK

= 50msps, f

输出

= 5.02mhz, t = 25

o

c (注释 4, 8) 68 73 - dBc

f

CLK

= 50msps, f

输出

= 5.02mhz, t = 最小值 至 最大值 (注释 4, 8) 66 - - dBc

f

CLK

= 50msps, f

输出

= 2.51mhz (注释 4, 8) - 76 - dBc

f

CLK

= 50msps, f

输出

= 1.00mhz (注释 4, 8) - 79 - dBc

f

CLK

= 25msps, f

输出

= 1.0mhz (注释 4, 8) - 78 - dBc

+3v 电源 供应

multitone 电源 比率

f

CLK

= 20msps, f

输出

= 2.0mhz 至 2.99mhz, 8 tones 在 110khz

间隔 (注释 4, 8)

-75 - dBc

f

CLK

= 100msps, f

输出

= 10mhz 至 14.95mhz, 8 tones 在 530khz

间隔 (注释 4, 8)

-77 - dBc

电压 涉及

内部的 涉及 电压, v

FSADJ

管脚 18 电压 和 内部的 涉及 1.13 1.2 1.28 V

内部的 涉及 电压 逐渐变化 -

±

60 - ppm

/

ο

Χ

内部的 涉及 输出 电流

下沉/源 能力

-

±

50 -

µ

一个

涉及 输入 阻抗 -1 -m

Ω

涉及 输入 乘以 带宽 (便条 8) - 1.4 - MHz

数字的 输入

d11-d0, clk

输入 逻辑 高 电压 和

5v 供应, v

IH

(便条 3) 3.5 5 - V

输入 逻辑 高 电压 和

3v 供应, v

IH

(便条 3) 2.1 3 - V

输入 逻辑 低 电压 和

5v 供应, v

IL

(便条 3) - 0 1.3 V

输入 逻辑 低 电压 和

3v 供应, v

IL

(便条 3) - 0 0.9 V

睡眠 输入 电流, i

IH

-25 - +25

µ

一个

输入 逻辑 电流, i

IH

-20 - +20

µ

一个

输入 逻辑 电流, i

IL

-10 - +10

µ

一个

数字的 输入 电容, c

在

-5 - pF

定时 特性

数据 建制 时间, t

SU

看 图示 4 (便条 3) - 1.5 - ns

数据 支撑 时间, t

HLD

看 图示 4 (便条 3) - 1.2 - ns

传播 延迟 时间, t

PD

看 图示 4 - 2.5 - ns

clk 脉冲波 宽度, t

PW1

, t

PW2

看 图示 4 (便条 3) 4 - - ns

电的 规格

AV

DD

= dv

DD

= +5v, v

REF

= 内部的 1.2v, ioutfs = 20ma, t

一个

= 25

o

c 为 所有 典型 值

(持续)

参数 测试 情况 最小值 典型值 最大值 单位

HI5960