初步的

cy28346-2

文档 #: 38-07509 rev. *b 页 2 的 20

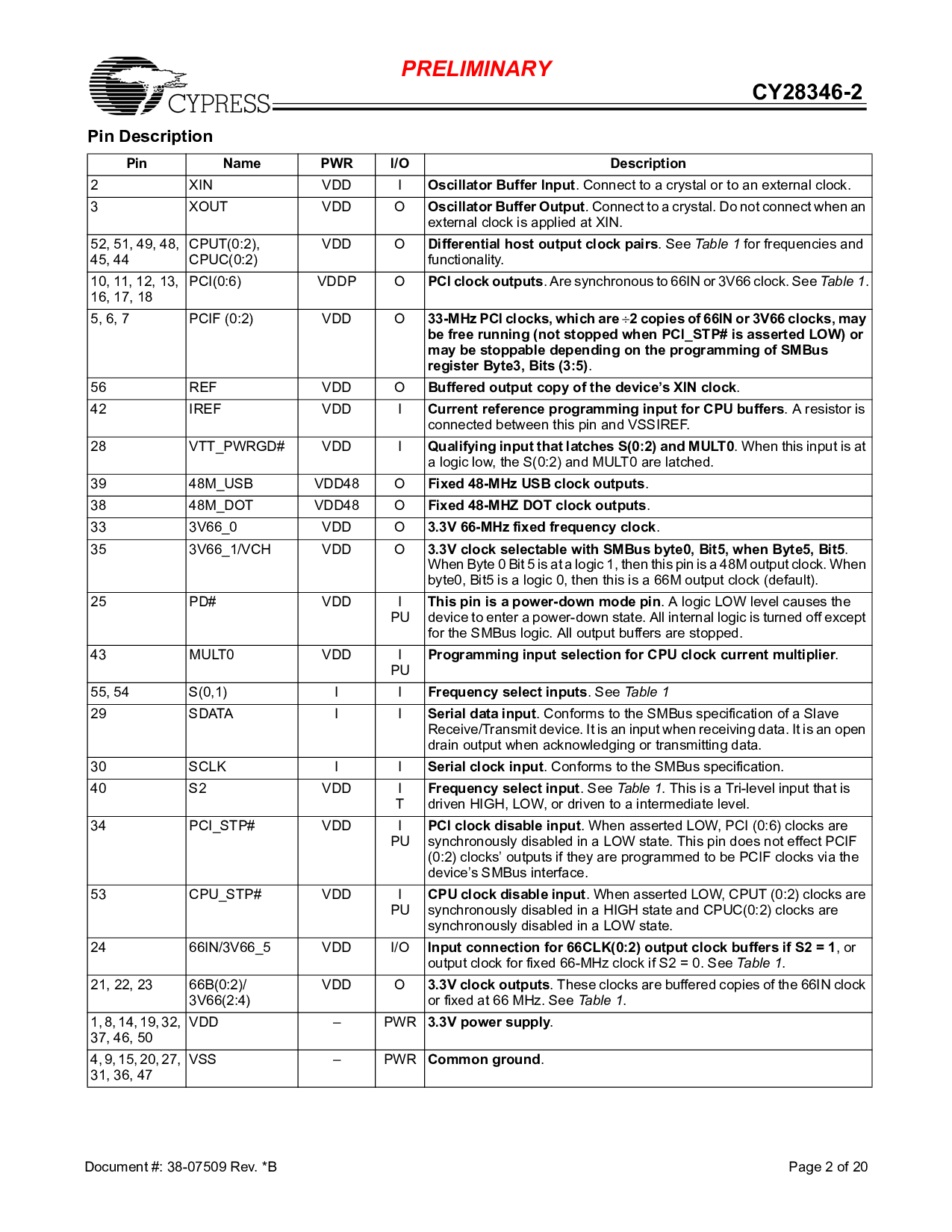

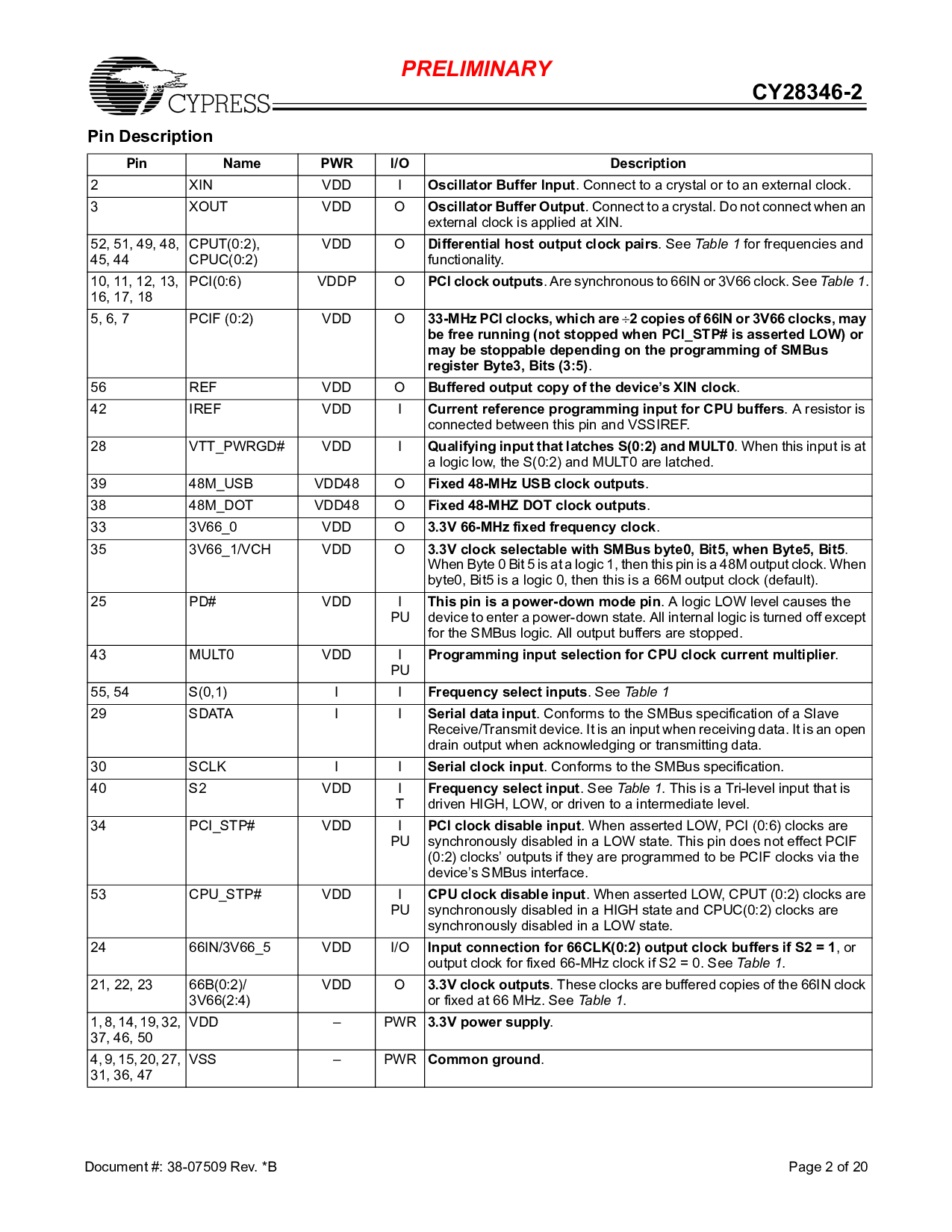

管脚 描述

管脚 名字 PWR i/o 描述

2XIN VDDI

振荡器 缓存区 输入

. 连接 至 一个 结晶 或者 至 一个 外部 时钟.

3XOUT VDDO

振荡器 缓存区 输出

.

连接 至 一个 结晶. 做 不 连接 当 一个

外部 时钟 是 应用 在 xin.

52, 51, 49, 48,

45, 44

cput(0:2),

cpuc(0:2)

VDD O

差别的 host 输出 时钟 pairs

. 看

表格 1

为 发生率 和

符合实际.

10, 11, 12, 13,

16, 17, 18

pci(0:6) VDDP O

pci 时钟 输出

. 是 同步的 至 66in 或者 3v66 时钟. 看

Table 1

.

5, 6, 7 pcif (0:2) VDD O

33-mhz pci clocks, 这个 是

÷

2 copies 的 66in 或者 3v66 clocks, 将

是 自由 运动 (不 stopped 当 pci_stp# 是 asserted 低) 或者

将 是 stoppable 取决于 在 这 程序编制 的 smbus

寄存器 byte3, 位 (3:5)

.

56 REF VDD O

缓冲 输出 copy 的 这 设备的 xin 时钟

.

42 IREF VDD I

电流 涉及 programming 输入 为 cpu 缓存区

. 一个 电阻 是

连接 在 th是 管脚 和 vssiref.

28 vtt_pwrgd# VDD I

qualifying 输入 那 latches s(0:2) 和 mult0

. 当 这个 输入 是 在

一个 逻辑 低, 这 s(0:2) 和 mult0 是 latched.

39 48m_usb VDD48 O

fixed 48-mhz usb 时钟 输出

.

38 48m_点 VDD48 O

fixed 48-mhz 点 时钟 输出

.

33 3v66_0 VDD O

3.3v 66-mhz fixed 频率 时钟

.

35 3v66_1/vch VDD O

3.3v 时钟 可选择的 和 smbus byte0, bit5, 当 byte5, bit5

.

当 字节 0 位 5 是 在 一个 逻辑 1, 然后这个 管脚 是 一个 48m 输出 时钟. 当

byte0, bit5 是 一个 逻辑 0, 然后 这个 是 一个 66m 输出 时钟 (default).

25 PD# VDD I

PU

这个 管脚 是 一个 电源-向下 模式 管脚

. 一个 逻辑 低 水平的 导致 这

设备 至 enter 一个 电源-向下 状态. 所有 内部的 逻辑 是 转变 止 除了

为 这 smbus 逻辑. 所有 输出 缓存区 是 stopped.

43 MULT0 VDD I

PU

程序编制 输入 选择 for cpu 时钟 电流 乘法器

.

55, 54 s(0,1) I I

频率 选择 输入

. 看

表格 1

29 SDATA I I

串行 数据 输入

. 遵从 至 这 smbus 规格 的 一个 从动装置

receive/transmit 设备. 它 是 一个 输入 当 接到 数据. 它 是 一个 打开

流 输出 当 acknowledging 或者 transmitting 数据.

30 SCLK I I

串行 时钟 输入

. 遵从 至 这 smbus 规格.

40 S2 VDD I

T

频率 选择 输入

. 看

表格 1

. 这个 是 一个 触发-水平的 输入 那 是

驱动 高, 低, 或者 驱动 至 一个 intermediate 水平的.

34 pci_stp# VDD I

PU

pci 时钟 使不能运转 输入

. 当 asserted 低, pci (0:6) clocks 是

synchronously 无能 在 一个 低 状态. 这个 管脚 做 不 效应 pcif

(0:2) clocks’ 输出 如果 它们 是 programmed 至 是 pcif clocks 通过 这

设备的 smbus 接口.

53 cpu_stp# VDD I

PU

cpu 时钟 使不能运转 输入

. 当 asserted 低,cput (0:2) clocks 是

synchronously 无能 在 一个 高 状态 和 cpuc(0:2) clocks 是

synchronously 无能 在 一个 低 状态.

24 66in/3v66_5 VDD i/o

输入 连接 为 66clk(0:2) 输出 时钟 缓存区 如果 s2 = 1

, 或者

输出 时钟 为 fixed 66-mhz时钟 如果 s2 = 0. 看

Table 1

.

21, 22, 23 66b(0:2)/

3v66(2:4)

VDD O

3.3v 时钟 输出

. 这些 clocks 是 缓冲 copies 的 这 66in 时钟

或者 fixed 在 66 mhz. 看

Table 1

.

1, 8, 14, 19, 32,

37, 46, 50

VDD – PWR

3.3v 电源 供应

.

4, 9, 15, 20, 27,

31, 36, 47

VSS – PWR

一般 地面

.