ad7440/ad7450a

rev. c | 页 9 的 28

管脚 配置 和函数 描述

03051-一个-005

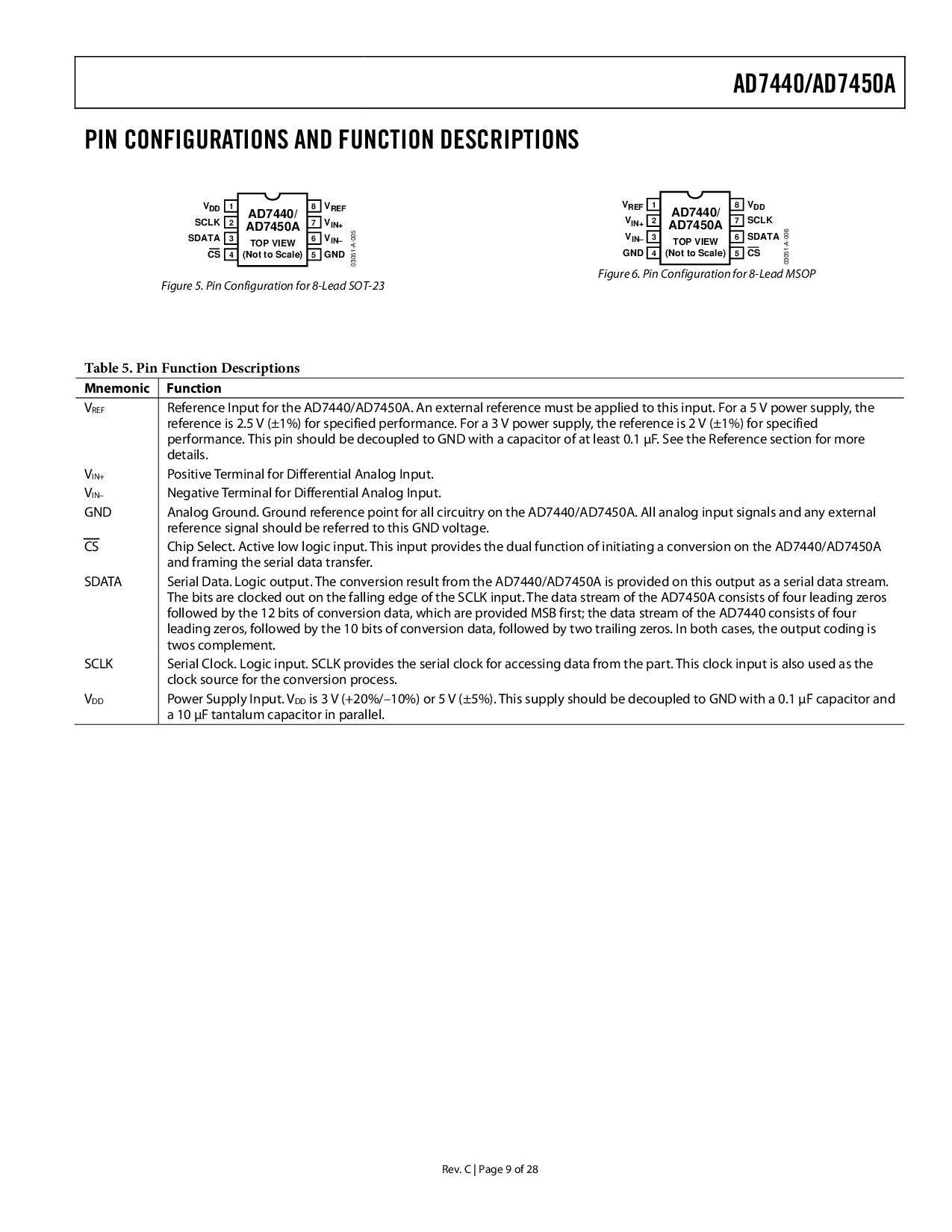

V

REF

V

IN+

V

IN–

地

8

7

6

5

V

DD

1

SCLK

2

SDATA

3

CS

4

ad7440/

AD7450A

顶 视图

(不 至 规模)

图示 5. 管脚 配置 为 8-含铅的 sot-23

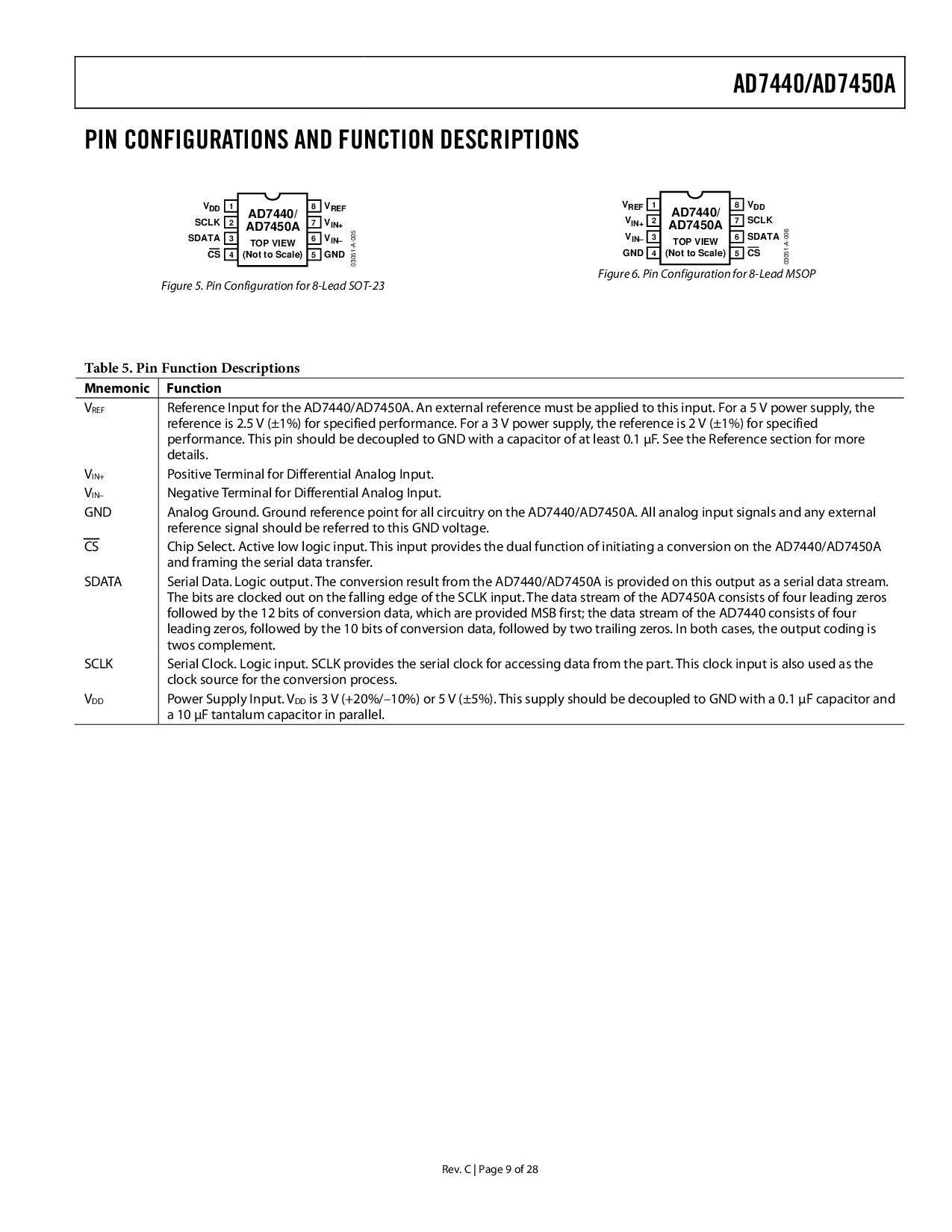

03051-一个-006

V

DD

SCLK

SDATA

CS

8

7

6

5

V

REF

1

V

IN+

2

V

IN–

3

地

4

ad7440/

AD7450A

顶 视图

(不 至 规模)

图示 6. 管脚 配置 为 8-含铅的 msop

表格 5. 管脚 函数 描述

Mnemonic 函数

V

REF

涉及 输入 为 这 ad7440/ad7450a. 一个 外部 涉及 必须 是 应用 至 这个 输入. 为 一个 5 v 电源 供应, 这

涉及 是 2.5 v (±1%) 为 指定 效能. 为 一个3 v 电源 供应, 这 涉及 是 2 v (±1%) 为 指定

效能. 这个 管脚 应当 是 decoupled 至 地 和 一个 电容 的 在 least 0.1 µf. 看 这 涉及 部分 为 更多

详细信息.

V

IN+

积极的 终端 为 差别的 相似物 输入.

V

IN–

负的 终端 为 differential 相似物 输入.

地

相似物 地面. 地面 涉及 要点 为 所有 电路系统 在 这 ad7440/ad7450a. 所有 相似物 输入 信号 和 任何 外部

涉及 信号 应当 是 涉及 至 这个 地 电压.

CS

碎片 选择. 起作用的 低 逻辑 输入. 这个 输入 提供 这双 函数 的 初始的 一个 转换 在 这 ad7440/ad7450a

和 framing 这 serial 数据 转移.

SDATA

串行 数据. 逻辑 输出. 这 转换 结果 从 这 ad7440/ad7450a 是 提供 在 这个 output 作 一个 串行 数据 stream.

这 位 是 clocked 输出 在 这 下落 边缘 的 这 sclk 输入.这 数据 stream 的 这 ad7450a 组成 的 四 leading zeros

followed 用 这 12 位 的 转换 数据, 这个 是 提供msb 第一; 这 数据 stream 的 这 ad7440 组成 的 四

leading zeros, followed 用 这 10 位 的 转换 数据, followed 用 二 trailing zeros. 在 两个都 具体情况, 这 输出 编码 是

twos complement.

SCLK

串行 时钟. 逻辑 输入. sclk 提供 这 串行 时钟 为 一个ccessing 数据 从 这 部分. 这个时钟 输入 是 也 使用 作 the

时钟 源 为 这 转换 处理.

V

DD

电源 供应 输入. v

DD

是 3 v (+20%/–10%) 或者 5 v (±5%). 这个 供应 应当是 decoupled 至 地 和 一个 0.1 µf 电容 和

一个 10 µf tantalum 电容 在 并行的.