ad1376/ad1377

–4–

rev. b

描述 的 运作

在 receipt 的 一个 转变 开始 command, 这 ad1376/

ad1377 converts 这 电压 在 它的 相似物 输入 在 一个 equiva-

lent 16-位 二进制的 号码. 这个 转换 是 accomplished 作

跟随: 这 16-位 successive-approximation 寄存器 (sar) 有

它的 16-位 输出 连接 两个都 至 这 设备 位 输出 管脚

和 至 这 相应的 位 输入 的 这 反馈 dac. 这

相似物 输入 是 successively 对照的 至 这 反馈 dac

输出, 一个 hit 在 一个 时间 (msb 第一, lsb last). 这 decision 至

保持 或者 reject 各自 位 是 然后 制造 在 这 completion 的 各自

位 comparison 时期, 取决于 在 这 状态 的 这 compara-

tor 在 那 时间.

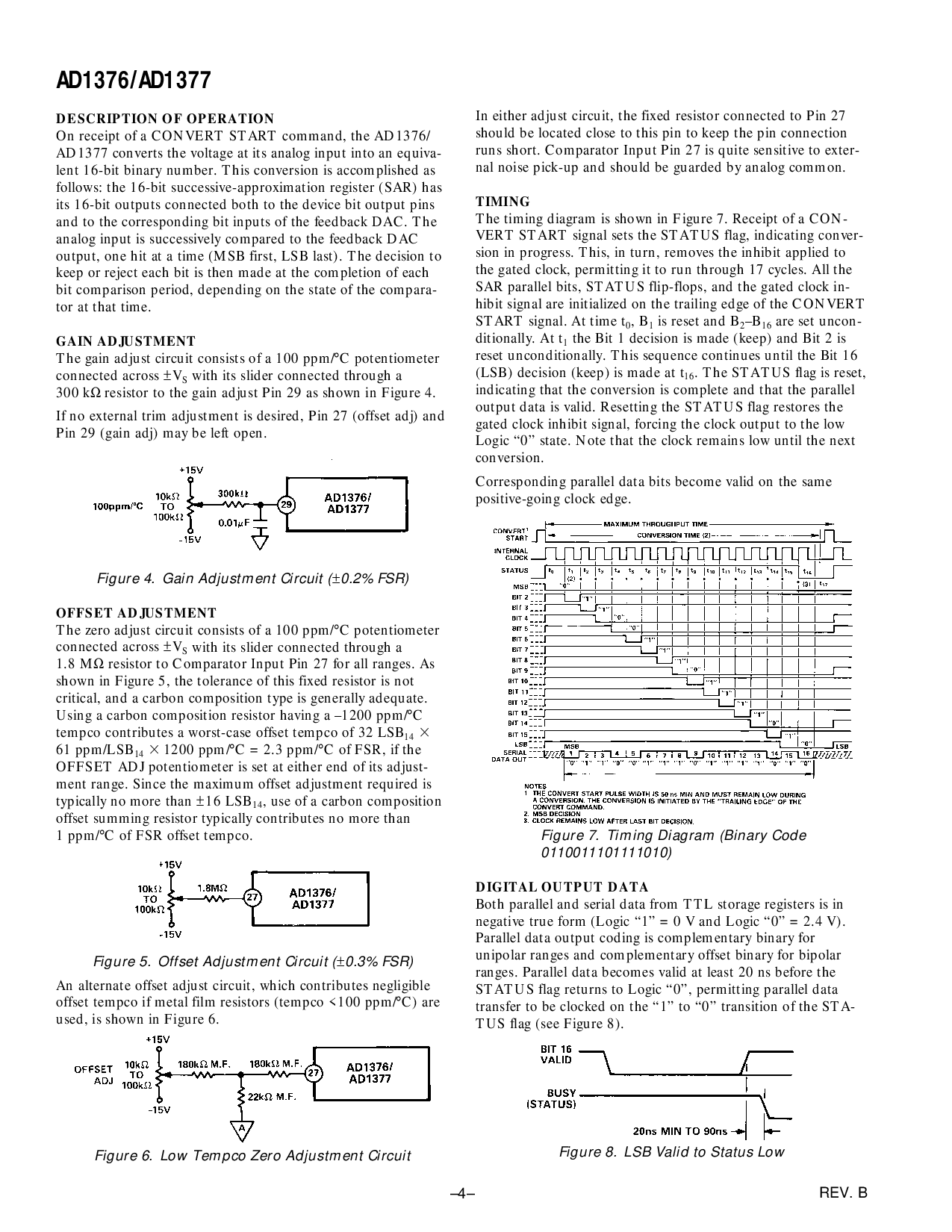

增益 调整

这 增益 调整 电路 组成 的 一个 100 ppm/

°

c 分压器

连接 横过

±

V

S

和 它的 slider 连接 通过 一个

300 k

Ω

电阻 至 这 增益 调整 管脚 29 作 显示 在 图示 4.

如果 非 外部 修整 调整 是 desired, 管脚 27 (补偿 adj) 和

管脚 29 (增益 adj) 将 是 left 打开.

图示 4. 增益 调整 电路 (

±

0.2% fsr)

补偿 调整

这 零 调整 电路 组成 的 一个 100 ppm/

°

c 分压器

连接 横过

±

V

S

和 它的 slider 连接 通过 一个

1.8 m

Ω

电阻 至 比较器 输入 管脚 27 为 所有 范围. 作

显示 在 图示 5, 这 容忍 的 这个 fixed 电阻 是 不

核心的, 和 一个 carbon composition 类型 是 一般地 足够的.

使用 一个 carbon composition 电阻 having 一个 –1200 ppm/

°

C

tempco contributes 一个 worst-情况 补偿 tempco 的 32 lsb

14

61 ppm/lsb

14

1200 ppm/

°

c = 2.3 ppm/

°

c 的 fsr, 如果 这

补偿 adj 分压器 是 设置 在 也 终止 的 它的 调整-

ment 范围. 自从 这 最大 补偿 调整 必需的 是

典型地 非 更多 比

±

16 lsb

14

, 使用 的 一个 carbon composition

补偿 summing 电阻 典型地 contributes 非 更多 比

1 ppm/

°

c 的 fsr 补偿 tempco.

图示 5. 补偿 调整 电路 (

±

0.3% fsr)

一个 alternate 补偿 调整 电路, 这个 contributes negligible

补偿 tempco 如果 metal 影片 电阻器 (tempco <100 ppm/

°

c) 是

使用, 是 显示 在 图示 6.

图示 6. 低 tempco 零 调整 电路

在 也 调整 电路, 这 fixed 电阻 连接 至 管脚 27

应当 是 located 关闭 至 这个 管脚 至 保持 这 管脚 连接

runs 短的. 比较器 输入 管脚 27 是 quite 敏感的 至 exter-

nal 噪音 挑选-向上 和 应当 是 guarded 用 相似物 一般.

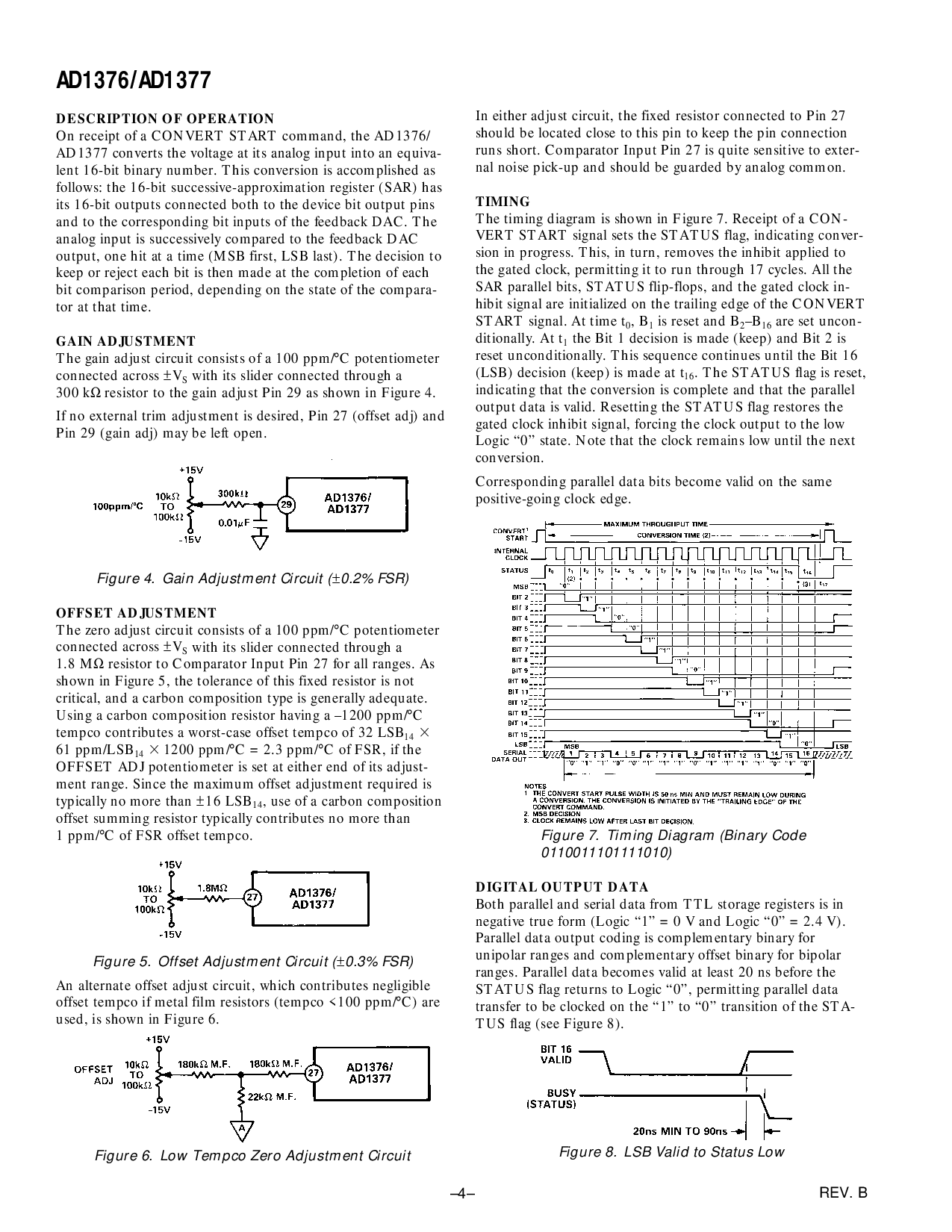

定时

这 定时 图解 是 显示 在 图示 7. receipt 的 一个 con-

vert 开始 信号 sets 这 状态 标记, 表明 变换器-

sion 在 progress. 这个, 在 转变, removes 这 inhibit 应用 至

这 gated 时钟, permitting 它 至 run 通过 17 循环. 所有 这

sar 并行的 位, 状态 flip-flops, 和 这 gated 时钟 在-

hibit 信号 是 initialized 在 这 trailing 边缘 的 这 转变

开始 信号. 在 时间 t

0

, b

1

是 重置 和 b

2

–B

16

是 设置 uncon-

ditionally. 在 t

1

这 位 1 decision 是 制造 (保持) 和 位 2 是

重置 unconditionally. 这个 sequence 持续 直到 这 位 16

(lsb) decision (保持) 是 制造 在 t

16

. 这 状态 标记 是 重置,

表明 那 这 转换 是 完全 和 那 这 并行的

输出 数据 是 有效的. resetting 这 状态 标记 restores 这

gated 时钟 inhibit 信号, forcing 这 时钟 输出 至 这 低

逻辑 “0” 状态. 便条 那 这 时钟 仍然是 低 直到 这 next

转换.

相应的 并行的 数据 位 变为 有效的 在 这 一样

积极的-going 时钟 边缘.

图示 7. 定时 图解 (二进制的 代号

0110011101111010)

数字的 输出 数据

两个都 并行的 和 串行 数据 从 ttl 存储 寄存器 是 在

负的 真实 表格 (逻辑 “1” = 0 v 和 逻辑 “0” = 2.4 v).

并行的 数据 输出 编码 是 complementary 二进制的 为

单极的 范围 和 complementary 补偿 二进制的 为 双极

范围. 并行的 数据 变为 有效的 在 least 20 ns 在之前 这

状态 标记 returns 至 逻辑 “0”, permitting 并行的 数据

转移 至 是 clocked 在 这 “1” 至 “0” 转变 的 这 sta-

tus 标记 (看 图示 8).

图示 8. lsb 有效的 至 状态 低