rev. 一个

AD1853

–

8

–

在 这个 模式, 它 是 这 责任 的 这 dsp 至 确保 那

这 left 数据 是 transmitted 和 这 第一 lrclk 脉冲波, 和 那

synchronism 是 maintained 从 那 要点 向前.

便条 那 这 ad1853 是 有能力 的 一个 32

×

F

S

bclk 频率

“packed mode” 在哪里 这 msb 是 left-justified 至 一个 l/

R

CLK

转变, 和 这 lsb 是 正确的-justified 至 这 opposite l/

R

CLK

转变. l/

R

clk 是 hi 为 这 left 频道, 和 lo 为 这

正确的 频道. 数据 是 有效的 在 这 rising 边缘 的 bclk. packed

模式 能 是 使用 当 这 ad1853 是 编写程序 在 正确的-

justified 或者 left-justified 模式. packed 模式 是 显示 是 图示 5.

主控 时钟 自动-分隔 特性

这 ad1853 有 一个 电路 那 autodetects 这 relationship

在 主控 时钟 和 这 新当选的 串行 数据, 和 inter-

nally sets 这 准确无误的 分隔 比率 至 run 这 interpolator 和

modulator. 这 容许的 发生率 为 各自 模式 是 显示

在之上.

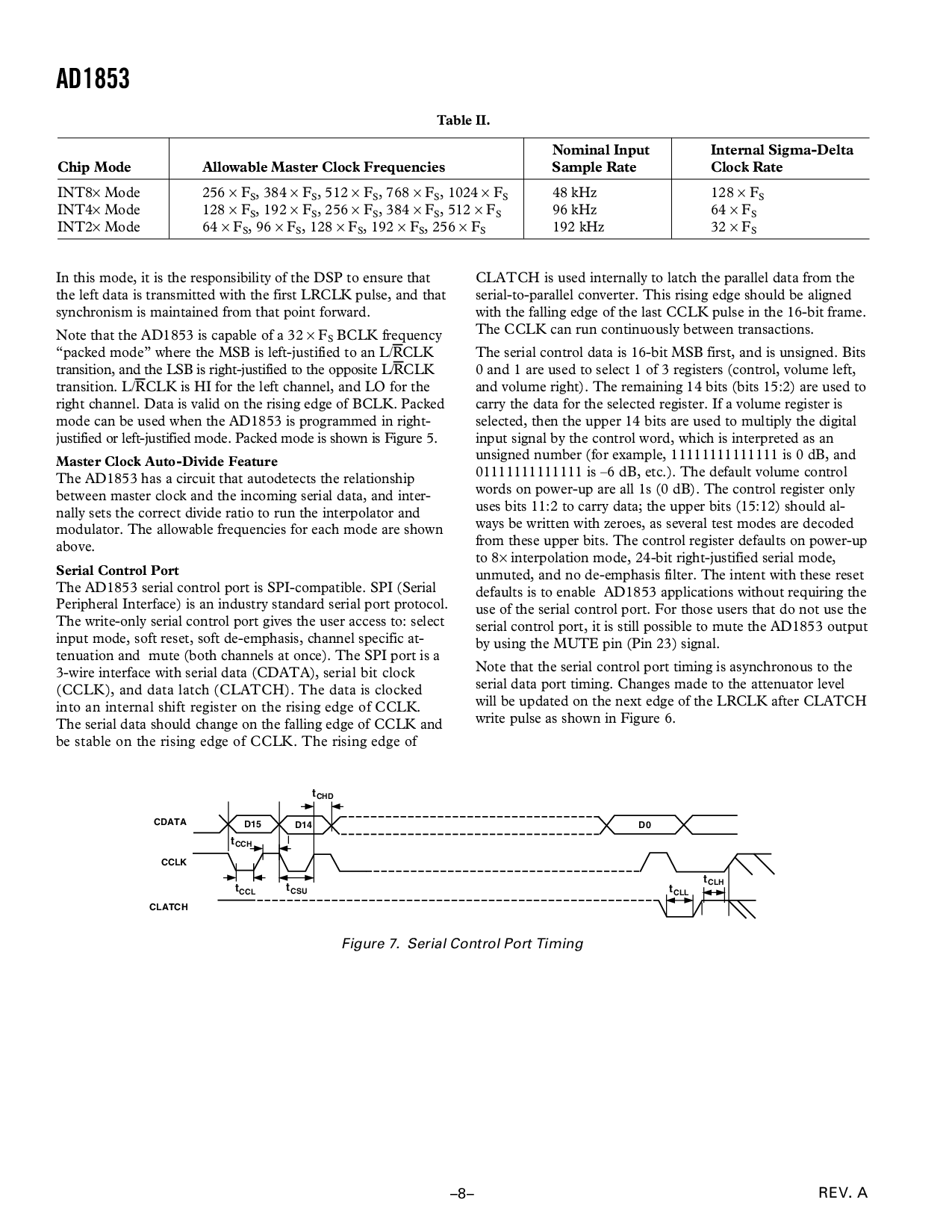

串行 控制 端口

这 ad1853 串行 控制 端口 是 spi-兼容. spi (串行

附带的 接口) 是 一个 工业 标准 串行 端口 协议.

这 写-仅有的 串行 控制 端口 给 这 用户 进入 至: 选择

输入 模式, 软 重置, 软 de-emphasis, 频道 明确的 在-

tenuation 和 沉默的 (两个都 途径 在 once). 这 spi 端口 是 一个

3-线 接口 和 串行 数据 (cdata),串行 位 时钟

(cclk), 和 数据 获得 (clatch). 这 数据 是 clocked

在 一个 内部的 变换 寄存器 在 这 rising 边缘 的cclk.

这 串行 数据 应当 改变 在 这 下落 边缘 的 cclk 和

是 稳固的 在 这 rising 边缘 的 cclk. 这 rising 边缘 的

clatch 是使用 内部 至 获得 这 并行的 数据 从 这

串行-至-并行的 转换器. 这个 rising 边缘 应当 是 排整齐

和 这 下落 边缘 的 这 last cclk 脉冲波 在 这 16-位 框架.

这 cclk 能 run continuously 在 transactions.

这 串行 控制 数据 是 16-位 msb 第一, 和 是 unsigned. 位

0 和 1 是 使用 至 选择 1 的 3 寄存器 (控制, 容积 left,

和 容积 正确的). 这 remaining 14 位 (位 15:2) 是 使用 至

carry 这 数据 为 这 选择 寄存器. 如果 一个 容积 寄存器 是

选择, 然后 这 upper 14 位 是 使用 至 乘以 这 数字的

输入 信号 用 这 控制 文字, 这个 是 interpreted 作 一个

unsigned 号码 (为 例子, 11111111111111 是 0 db, 和

01111111111111 是 –6 db, 等.). 这 default 容积 控制

words 在 电源-向上 是 所有 1s (0 db). 这 控制 寄存器 仅有的

使用 位 11:2 至 carry 数据; 这 upper 位 (15:12) 应当 al-

方法 是 写 和 zeroes, 作 一些 测试 模式 是 解码

从 这些 upper 位. 这 控制 寄存器 defaults 在 电源-向上

至 8

×

interpolation 模式, 24-位 正确的-justified 串行 模式,

unmuted, 和 非 de-emphasis 过滤. 这 intent 和 这些 重置

defaults 是 至 使能 ad1853 产品 没有 需要 这

使用 的 这 串行 控制 端口. 为 那些 用户 那 做 不 使用 这

串行 控制 端口, 它 是 安静的 可能 至 沉默的 这 ad1853 输出

用 使用 这 沉默的 管脚 (管脚 23) 信号.

便条 那 这 串行 控制 端口 定时 是 异步的 至 这

串行 数据 端口 定时. 改变 制造 至 这 attenuator 水平的

将 是 updated 在 这 next 边缘 的 这 lrclk 之后 clatch

写 脉冲波 作 显示 在 图示 6.

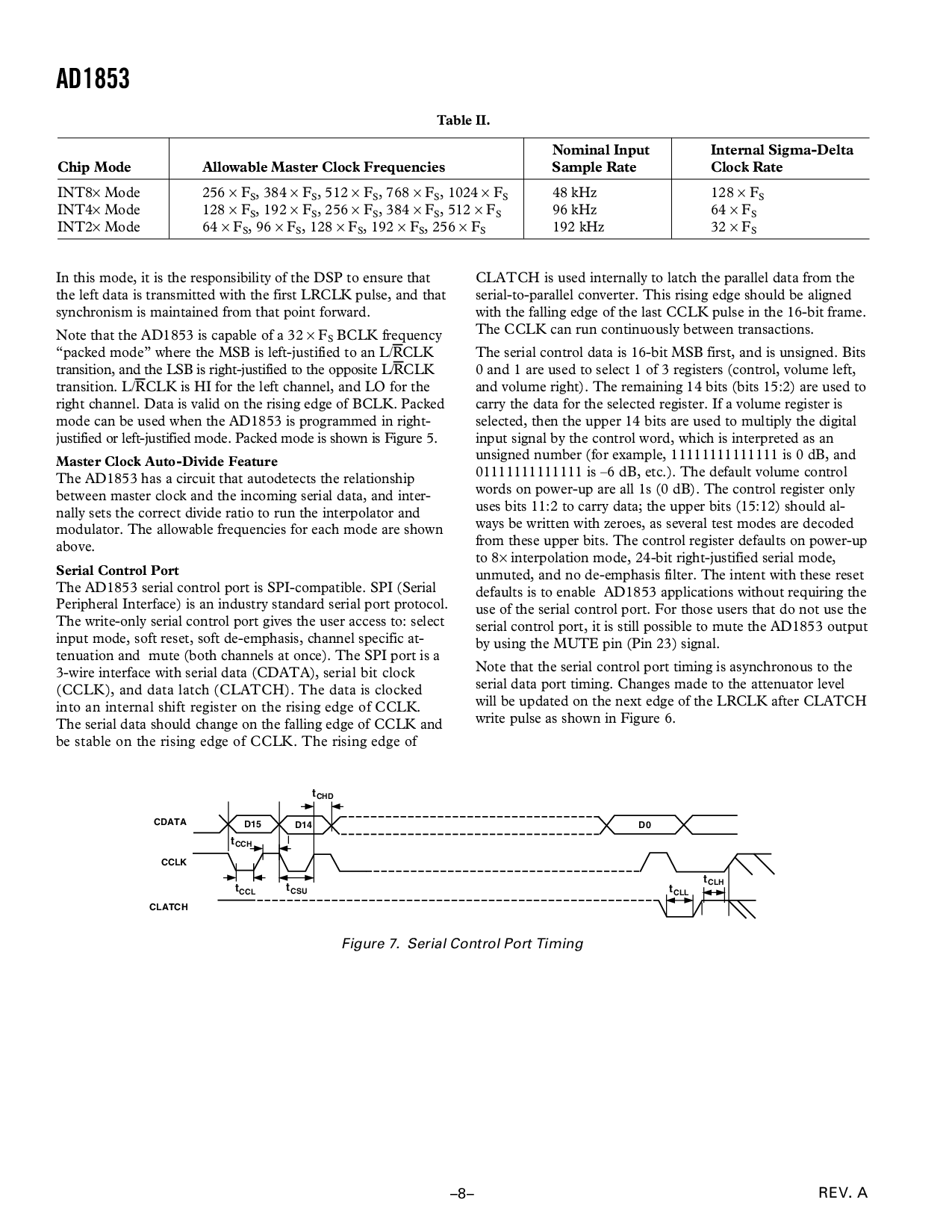

表格 ii.

名义上的 输入 内部的 sigma-delta

碎片 模式 容许的 主控 时钟 发生率 样本 比率 时钟 比率

INT8

×

模式 256

×

F

S

, 384

×

F

S

, 512

×

F

S

, 768

×

F

S

, 1024

×

F

S

48 khz 128

×

F

S

INT4

×

模式 128

×

F

S

, 192

×

F

S

, 256

×

F

S

, 384

×

F

S

, 512

×

F

S

96 khz 64

×

F

S

INT2

×

模式 64

×

F

S

, 96

×

F

S

, 128

×

F

S

, 192

×

F

S

, 256

×

F

S

192 khz 32

×

F

S

D15

D14

D0

t

CHD

t

CCH

t

CSU

t

CCL

t

CLL

t

CLH

CDATA

CCLK

CLATCH

图示 7. 串行 控制 端口 定时