6-10

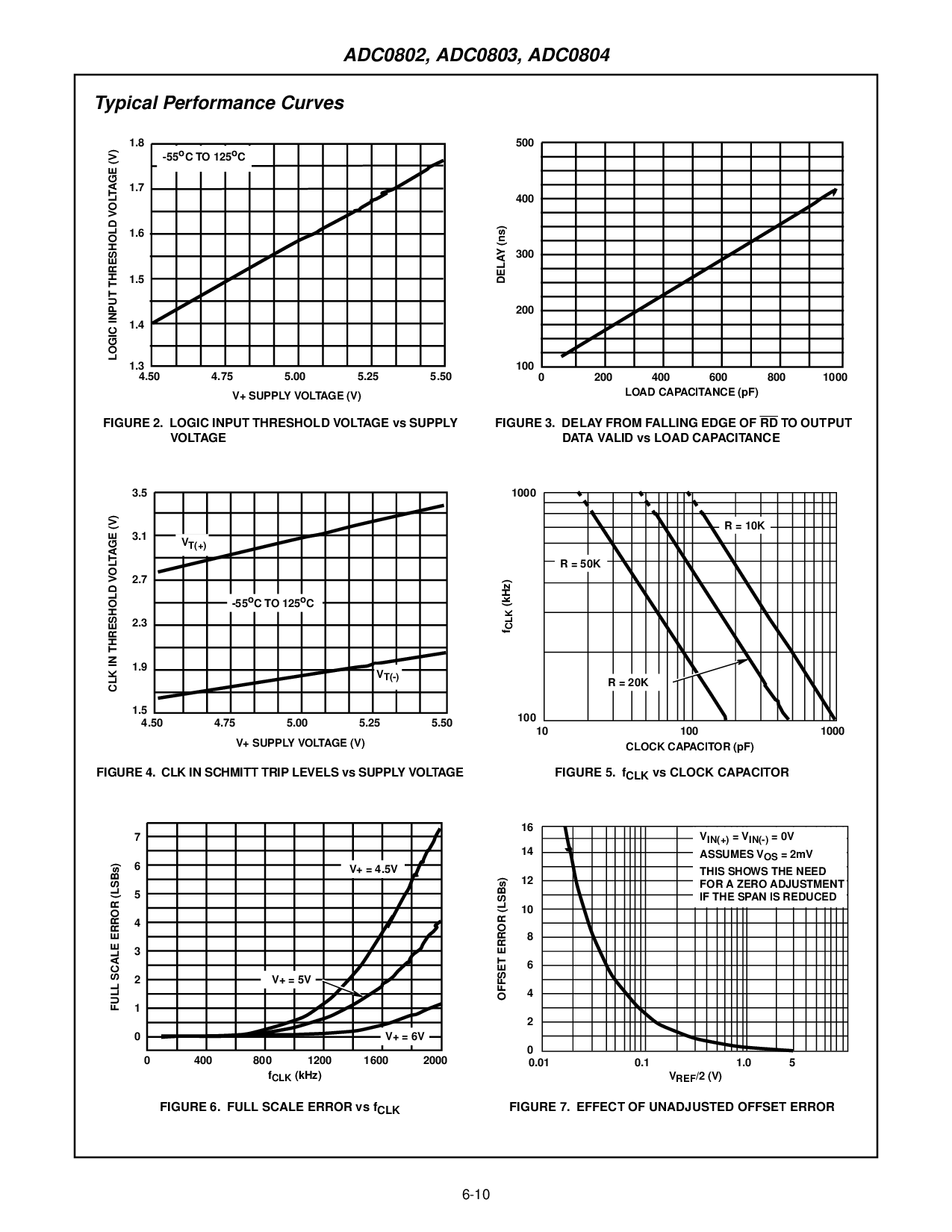

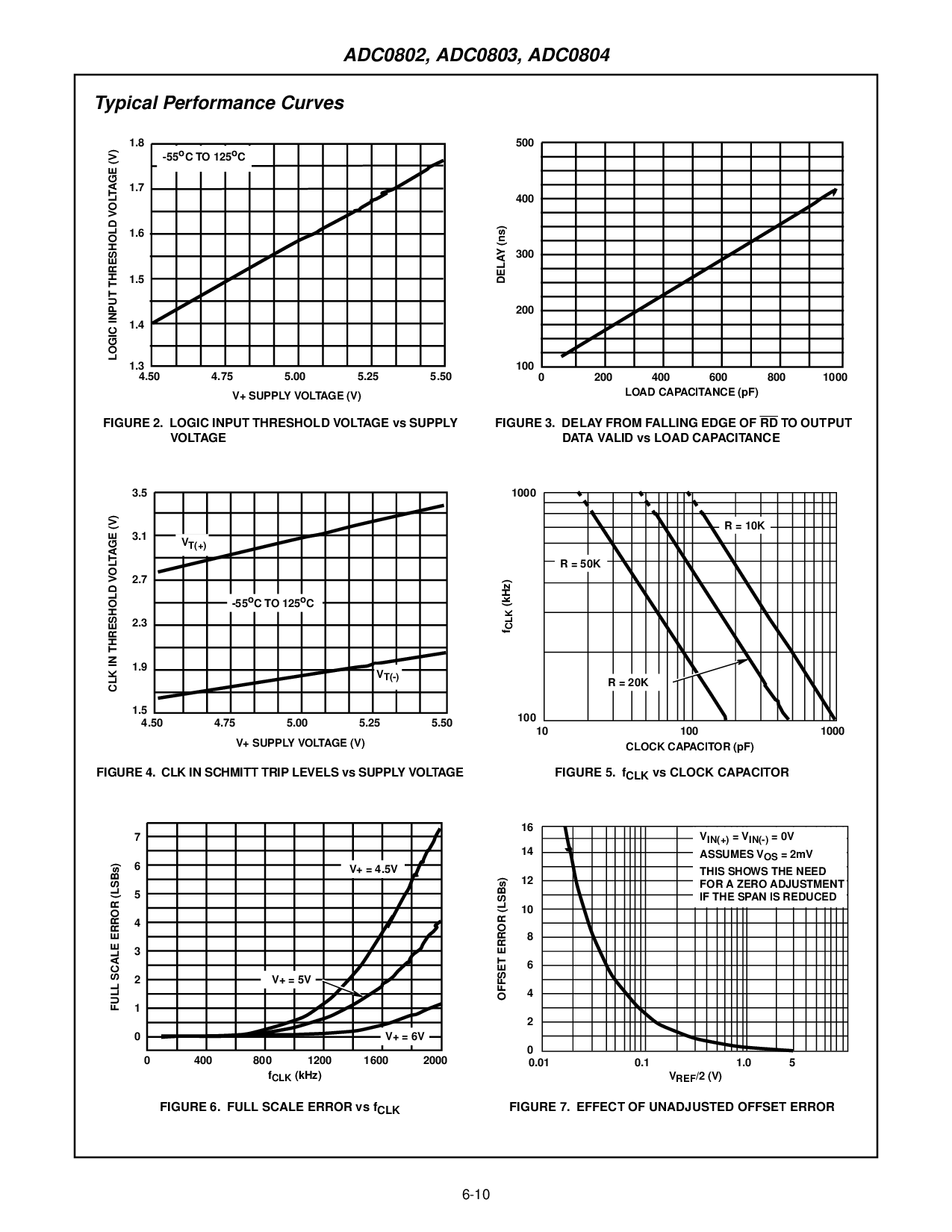

典型 效能 曲线

图示 2. 逻辑 输入 门槛 电压 vs 供应

电压

图示 3. 延迟 从 下落 边缘 的 rd 至 输出

数据 有效的 vs 加载 电容

图示 4. clk 在 施密特 trip 水平 vs 供应 电压 图示 5. f

CLK

vs 时钟 电容

图示 6. 全部 规模 错误 vs f

CLK

图示 7. 效应 的 unadjusted 补偿 错误

-55

o

c 至 125

o

C

1.8

1.7

1.6

1.5

1.4

1.3

4.754.50 5.00 5.25 5.50

v+ 供应 电压 (v)

逻辑 输入 门槛 电压 (v)

延迟 (ns)

500

400

300

200

100

0

加载 电容 (pf)

200 400 600 800 1000

clk 在 门槛 电压 (v)

3.5

3.1

2.7

2.3

1.9

1.5

4.50

v+ 供应 电压 (v)

-55

o

c 至 125

o

C

V

t(-)

V

t(+)

4.75 5.00 5.25 5.50

1000

时钟 电容 (pf)

f

CLK

(khz)

100

10010 1000

r = 10k

r = 50k

r = 20k

全部 规模 错误 (lsbs)

7

6

5

4

3

2

1

0

f

CLK

(khz)

0 400 800 1200 1600 2000

v+ = 4.5v

v+ = 5v

v+ = 6v

V

在(+)

= v

在(-)

= 0v

假设 v

OS

= 2mv

这个 显示 这 需要

为 一个 零 调整

如果 这 span 是 减少

补偿 错误 (lsbs)

16

14

12

10

8

6

4

2

V

REF

/2 (v)

0

0.01 0.1 1.0 5

adc0802, adc0803, adc0804