adf4360-6

rev. 0 | 页 10 的 24

muxout 和 锁 发现

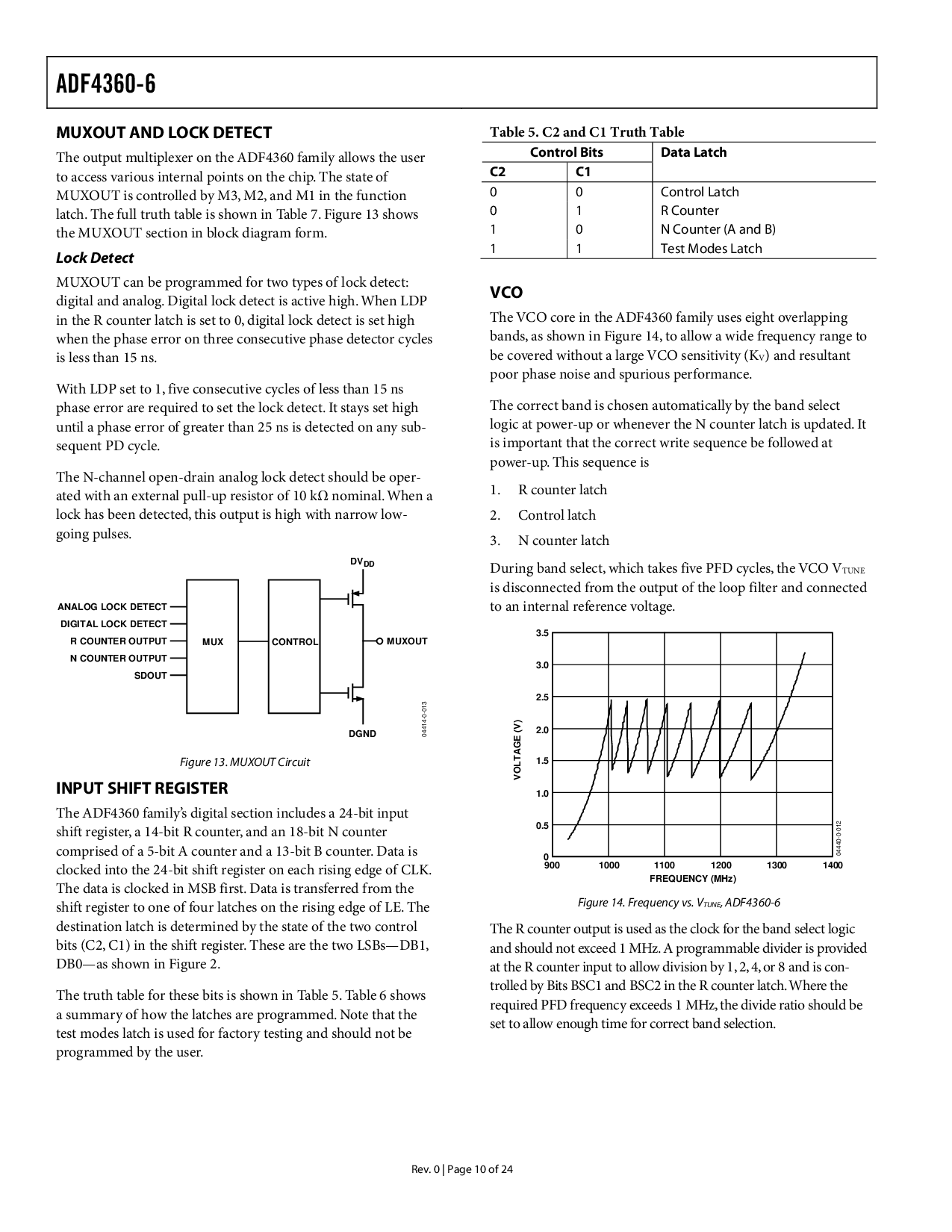

这 输出 多路调制器 在 这 adf4360 家族 准许 这 用户

至 进入 各种各样的 内部的 点 在 这 碎片. 这 状态 的

muxout 是 控制 用 m3, m2, 和 m1 在 这 函数

获得. 这 全部 真实 表格 是 显示 在 表格 7. 图示 13 显示

这 muxout 部分 在 块 图解 表格.

锁 发现

muxout 能 是 编写程序 为 二 类型 的 锁 发现:

数字的 和 相似物. 数字的 锁 发现 是 起作用的 高. 当 ldp

在 这 r 计数器 获得 是 设置 至 0, 数字的 锁 发现 是 设置 高

当 这 阶段 错误 在 三 consecutive 阶段 探测器 循环

是 较少 比 15 ns.

和 ldp 设置 至 1, five consecutive 循环 的 较少 比 15 ns

阶段 错误 是 必需的 至 设置 这 锁 发现. 它 stays 设置 高

直到 一个 阶段 错误 的 更好 比 25 ns 是 发现 在 任何 sub-

sequent pd 循环.

这 n-频道 打开-流 相似物 锁 发现 应当 是 oper-

ated 和 一个 外部 拉-向上 电阻 的 10 kΩ 名义上的. 当 一个

锁 有 被 发现, 这个 输出 是 高 和 narrow 低-

going 脉冲.

r 计数器 输出

n 计数器 输出

数字的 锁 发现

DGND

CONTROLMUX

MUXOUT

DV

DD

相似物 锁 发现

SDOUT

04414-0-013

图示 13. muxout 电路

输入 变换 寄存器

这 adf4360 家族’s 数字的 部分 包含 一个 24-位 输入

变换 寄存器, 一个 14-位 r 计数器, 和 一个 18-位 n 计数器

包括 的 一个 5-位 一个 计数器 和 一个 13-位 b 计数器. 数据 是

clocked 在 这 24-位 变换 寄存器 在 各自 rising 边缘 的 clk.

这 数据 是 clocked 在 msb 第一. 数据 是 transferred 从 这

变换 寄存器 至 一个 的 四 latches 在 这 rising 边缘 的 le. 这

destination 获得 是 决定 用 这 状态 的 这 二 控制

位 (c2, c1) 在 这 变换 寄存器. 这些 是 这 二 lsbs—db1,

db0—as 显示 在 图示 2.

这 真实 表格 为 这些 位 是 显示 在 表格 5. 表格 6 显示

一个 summary 的 如何 这 latches 是 编写程序. 便条 那 这

测试 模式 获得 是 使用 为 工厂 测试 和 应当 不 是

编写程序 用 这 用户.

表格 5. c2 和 c1 真实 表格

控制 位

C2 C1

数据 获得

0 0 控制 获得

0 1 r 计数器

1 0 n 计数器 (一个 和 b)

1 1 测试 模式 获得

VCO

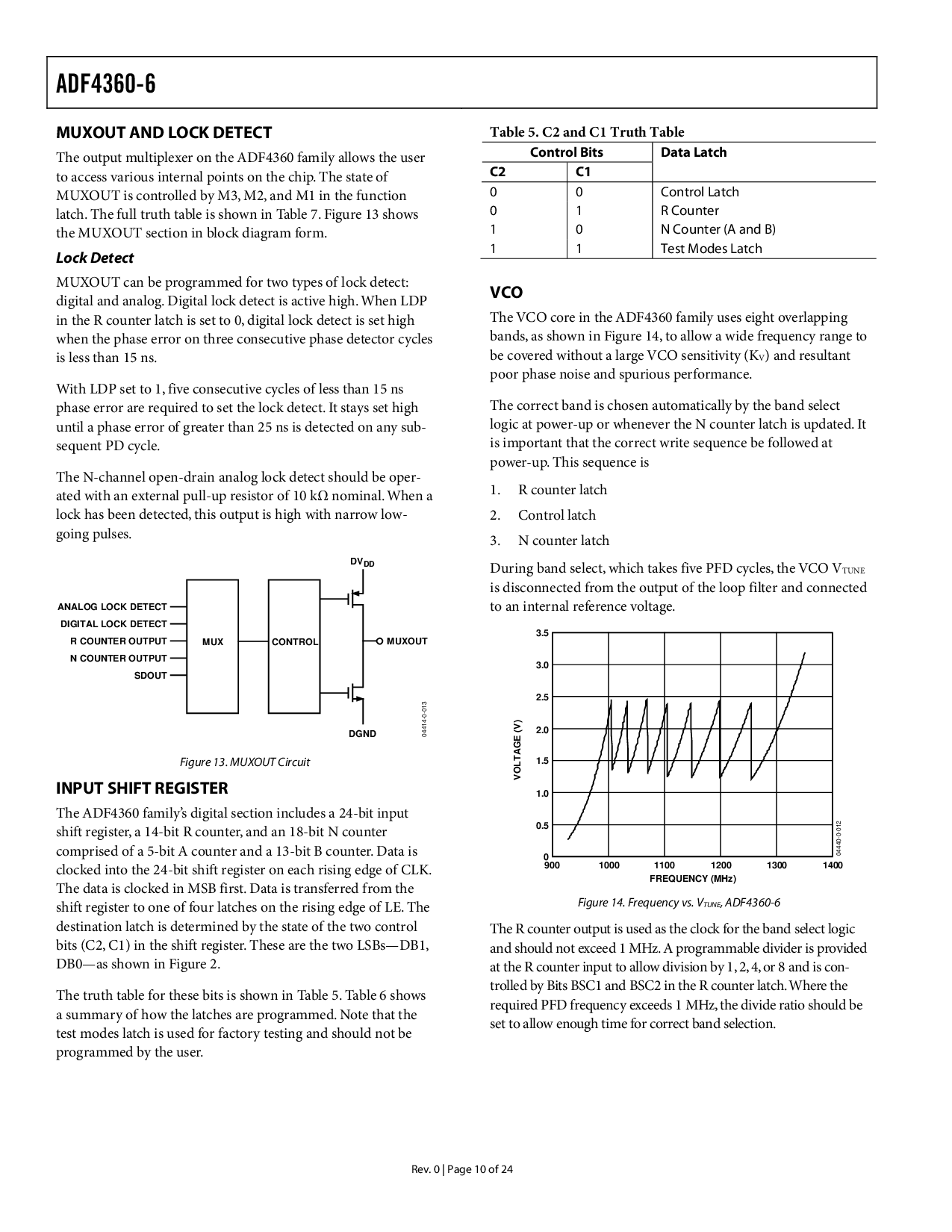

这 vco 核心 在 这 adf4360 家族 使用 第八 overlapping

bands, 作 显示 在 图示 14, 至 准许 一个 宽 频率 范围 至

是 covered 没有 一个 大 vco 敏锐的 (k

V

) 和 resultant

poor 阶段 噪音 和 spurious 效能.

这 准确无误的 带宽 是 选择 automatically 用 这 带宽 选择

逻辑 在 电源-向上 或者 whenever 这 n 计数器 获得 是 updated. 它

是 重要的 那 这 准确无误的 写 sequence 是 followed 在

电源-向上. 这个 sequence 是

1.

r 计数器 获得

2.

控制 获得

3.

n 计数器 获得

Duringb和select, whicht一个kesfive pfd cycles, theVCOV

TUNE

是 disconnected 从 这 输出 的 这 循环 过滤 和 连接

至 一个 内部的 涉及 电压.

04440-0-012

0

2.5

2.0

3.0

1.5

1.0

0.5

3.5

1000900 1400130012001100

频率 (mhz)

电压 (v)

图示 14. 频率 vs. v

TUNE

, adf4360-6

这 r 计数器 输出 是 使用 作 这 时钟 为 这 带宽 选择 逻辑

和 应当 不 超过 1 mhz. 一个 可编程序的 分隔物 是 提供

在 这 r 计数器 输入 至 准许 分隔 用 1, 2, 4, 或者 8 和 是 con-

trolled 用 位 bsc1 和 bsc2 在 这 r 计数器 获得. 在哪里 这

必需的 pfd 频率 超过 1 mhz, 这 分隔 比率 应当 是

设置 至 准许 足够的 时间 为 准确无误的 带宽 选择.