rev. 0

ADuC831

–9–

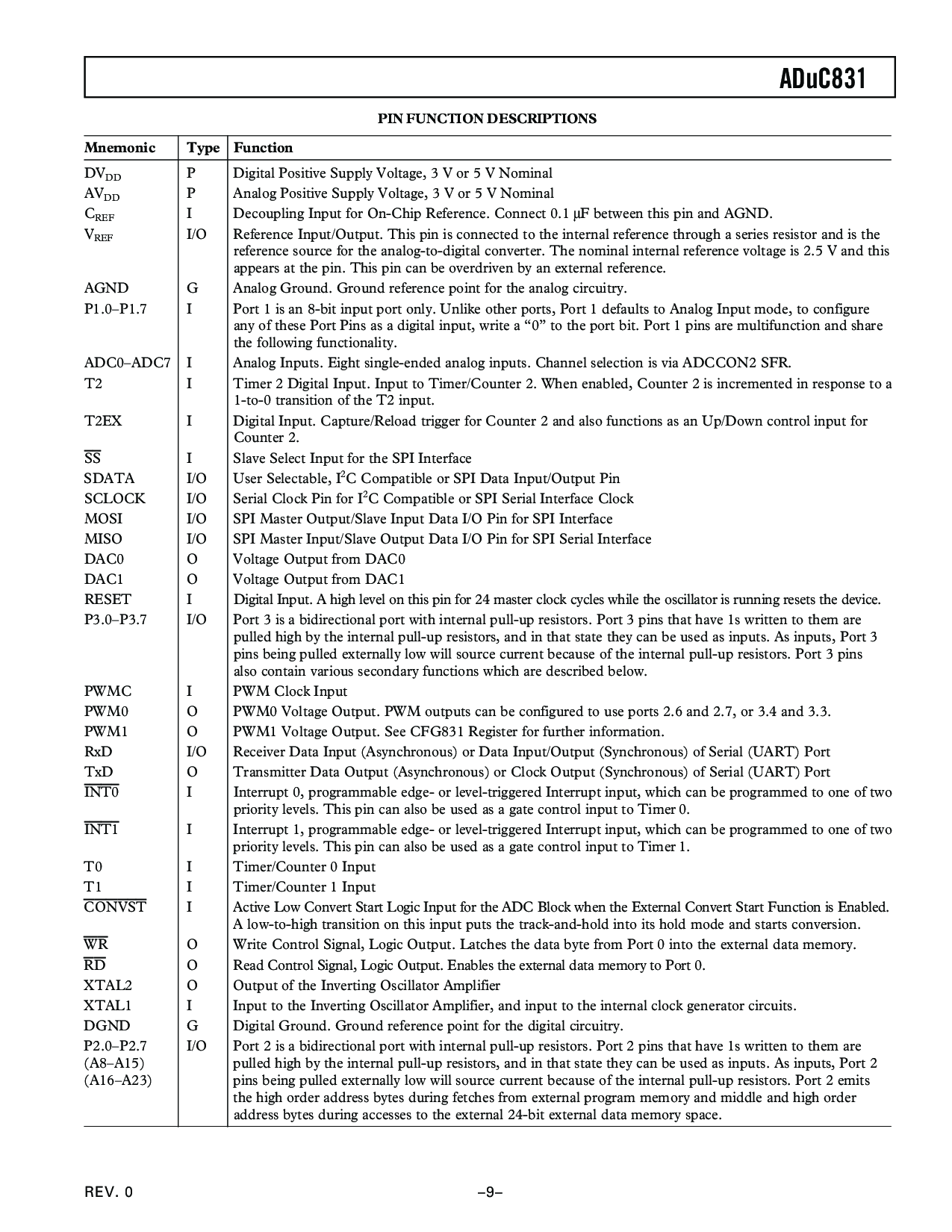

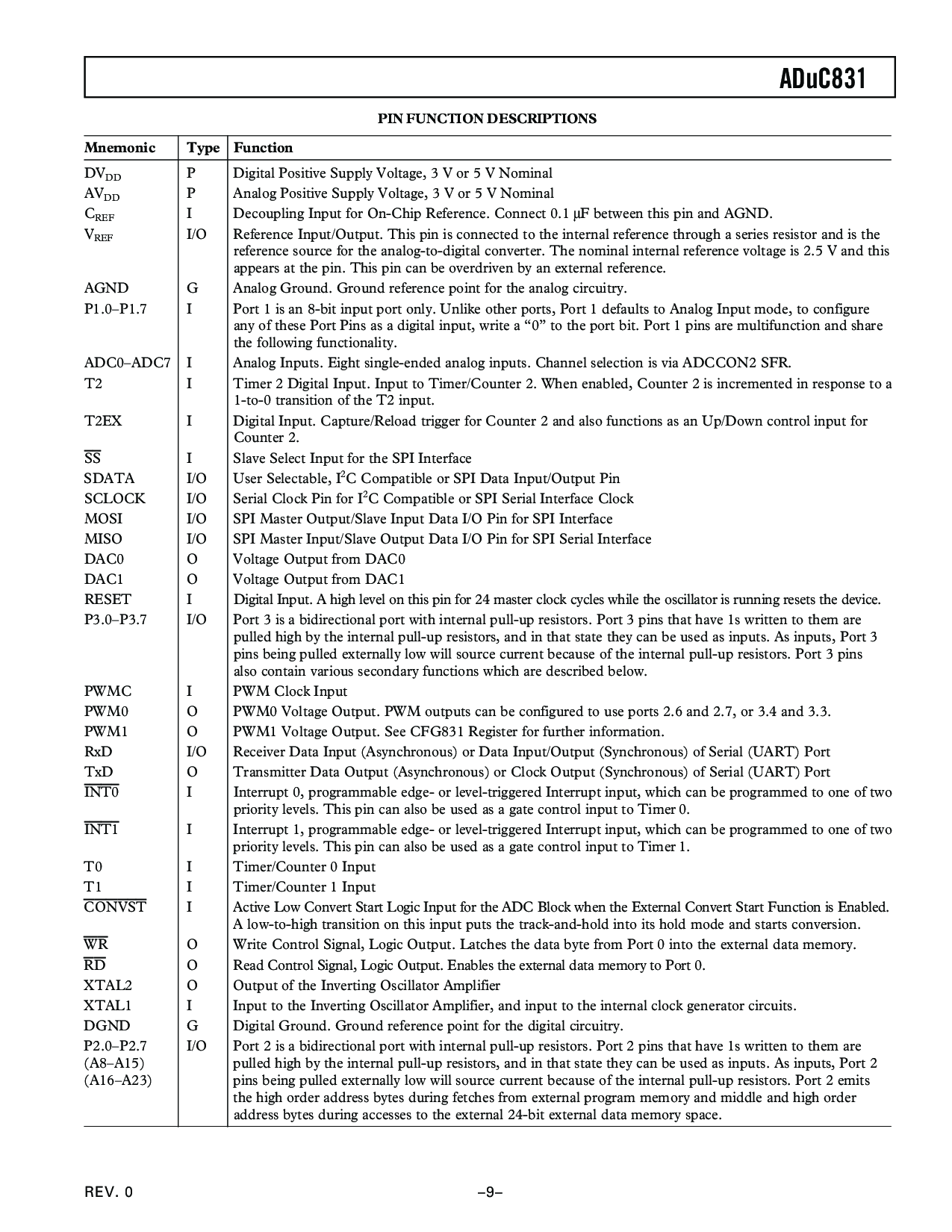

管脚 函数 描述

Mnemonic 类型 函数

DV

DD

PDigital 积极的 供应 电压, 3 v 或者 5 v 名义上的

AV

DD

PAnalog 积极的 供应 电压, 3 v 或者 5 v 名义上的

C

REF

IDecoupling 输入 为 在-碎片 涉及. 连接 0.1

µ

f 在 这个 管脚 和 agnd.

V

REF

i/o 涉及 输入/输出. 这个 管脚 是 连接 至 这 内部的 涉及 通过 一个 序列 电阻 和 是 这

涉及 源 为 这 相似物-至-数字的 转换器. 这 名义上的 内部的 涉及 电压 是 2.5 v 和 这个

呈现 在 这 管脚. 这个 管脚 能 是 过载 用 一个 外部 涉及.

AGND G 相似物 地面. 地面 涉及 要点 为 这 相似物 电路系统.

p1.0–p1.7 I 端口 1 是 一个 8-位 输入 端口 仅有的. 不像 其它 端口, 端口 1 defaults 至 相似物 输入 模式, 至 配置

任何 的 这些 端口 管脚 作 一个 数字的 输入, 写 一个 “0” 至 这 端口 位. 端口 1 管脚 是 multifunction 和 share

这 下列的 符合实际.

ADC0–ADC7 I 相似物 输入. 第八 单独的-结束 相似物 输入. 频道 选择 是 通过 adccon2 sfr.

T2 I 计时器 2 数字的 输入. 输入 至 计时器/计数器 2. 当 使能, 计数器 2 是 incremented 在 回馈 至 一个

1-至-0 转变 的 这 t2 输入.

T2EX I 数字的 输入. 俘获/再装填 触发 为 计数器 2 和 也 功能 作 一个 向上/向下 控制 输入 为

计数器 2.

SS

I 从动装置 选择 输入 为 这 spi 接口

SDATA i/o 用户 可选择的, i

2

c 兼容 或者 spi 数据 输入/输出 管脚

SCLOCK i/o 串行 时钟 管脚 为 i

2

c 兼容 或者 spi 串行 接口 时钟

MOSI i/o spi 主控 输出/从动装置 输入 数据 i/o 管脚 为 spi 接口

MISO i/o spi 主控 输入/从动装置 输出 数据 i/o 管脚 为 spi 串行 接口

DAC0 O 电压 输出 从 dac0

DAC1 O 电压 输出 从 dac1

重置 I 数字的 输入. 一个 高 水平的 在 这个 管脚 为 24 主控 时钟 循环 当 这 振荡器 是 运动 resets 这 设备.

p3.0–p3.7 i/o 端口 3 是 一个 双向的 端口 和 内部的 拉-向上 电阻器. 端口 3 管脚 那 有 1s 写 至 它们 是

牵引的 高 用 这 内部的 拉-向上 电阻器, 和 在 那 状态 它们 能 是 使用 作 输入. 作 输入, 端口 3

管脚 正在 牵引的 externally 低 将 源 电流 因为 的 这 内部的 拉-向上 电阻器. 端口 3 管脚

也 包含 各种各样的 secondary 功能 这个 是 描述 在下.

PWMC I pwm 时钟 输入

PWM0 O pwm0 电压 输出. pwm 输出 能 是 配置 至 使用 端口 2.6 和 2.7, 或者 3.4 和 3.3.

PWM1 O pwm1 电压 输出. 看 cfg831 寄存器 为 更远 信息.

RxD i/o 接受者 数据 输入 (异步的) 或者 数据 输入/输出 (同步的) 的 串行 (uart) 端口

TxD O 传输者 数据 输出 (异步的) 或者 时钟 输出 (同步的) 的 串行 (uart) 端口

INT0

I 中断 0, 可编程序的 边缘- 或者 水平的-triggered 中断 输入, 这个 能 是 编写程序 至 一个 的 二

priority 水平. 这个 管脚 能 也 是 使用 作 一个 门 控制 输入 至 计时器 0.

INT1

I 中断 1, 可编程序的 边缘- 或者 水平的-triggered 中断 输入, 这个 能 是 编写程序 至 一个 的 二

priority 水平. 这个 管脚 能 也 是 使用 作 一个 门 控制 输入 至 计时器 1.

T0 I 计时器/计数器 0 输入

T1 I 计时器/计数器 1 输入

CONVST

I 起作用的 低 转变 开始 逻辑 输入 为 这 模数转换器 块 当 这 外部 转变 开始 函数 是 使能.

一个 低-至-高 转变 在 这个 输入 puts 这 追踪-和-支撑 在 它的 支撑 模式 和 开始 转换.

WR

OWrite 控制 信号, 逻辑 输出. latches 这 数据 字节 从 端口 0 在 这 外部 数据 记忆.

RD

或者ead 控制 信号, 逻辑 输出. 使能 这 外部 数据 记忆 至 端口 0.

XTAL2 O 输出 的 这 反相的 振荡器 放大器

XTAL1 I 输入 至 这 反相的 振荡器 放大器, 和 输入 至 这 内部的 时钟 发生器 电路.

DGND G 数字的 地面. 地面 涉及 要点 为 这 数字的 电路系统.

p2.0–p2.7 i/o 端口 2 是 一个 双向的 端口 和 内部的 拉-向上 电阻器. 端口 2 管脚 那 有 1s 写 至 它们 是

(a8–a15) 牵引的 高 用 这 内部的 拉-向上 电阻器, 和 在 那 状态 它们 能 是 使用 作 输入. 作 输入, 端口 2

(a16–a23) 管脚 正在 牵引的 externally 低 将 源 电流 因为 的 这 内部的 拉-向上 电阻器. 端口 2 emits

这 高 顺序 地址 字节 在 fetches 从 外部 程序 记忆 和 middle 和 高 顺序

地址 字节 在 accesses 至 这 外部 24-位 外部 数据 记忆 空间.