一般 descripTION

这CS5330a 一个nd cs5331a 是18-bit,2-ch一个n-

nel 一个一个log-至-digitalConverters designed 为

digital一个udio 一个pplications. 各自deviceuses 二

one-bit delta-sig毫安modul一个tors whichsimultane-

ously samplethe一个一个log 在put signals一个t 128

timestheout放 sample r一个te(fs). 这 resul德州仪器ng

seri一个lbitstre一个ms一个redig它一个llyfiltered,yielding

p一个irs of18-b它v一个lues. th是 technique yields

nearlyide一个lconversionperform一个nceindependent

ofin放 frequency一个ndamplitude. the converters

做 not requiredifficult-至-design 或者 expensive

一个n德州仪器-一个li一个sfilters 一个nd 做 不 require externalsam-

ple-一个nd-hold一个mplifiersor 一个voltage reference.

TheCS5330一个和 cs5331一个 differ onlyin the

output 串行 数据 form在. these formats 是 dis-

cussed 在 the following sec德州仪器ons 一个nd shownin

Figures 2一个nd3.

一个on-chipvoltage referenceprovides 为 一个 sin-

gle-endedinputsign一个lr一个nge of4.0Vpp.Output

d一个tais一个v一个ilablein seri一个l 表格, coded一个s 2’s

complement18-bitnumbers.Typical power con-

sumpti在is150 mw which c一个n 是 further

reduced 至 0.5 mWusing 这Po我们r-down

模式.

F或者 更多 information 在 delta-sigmamodul一个-

ti在, 看 the references 在 这 终止 的 th是 dat一个

薄板.

SYSTEMDESIGN

Very fewextern一个l竞赛onents 是 requiredto

supp或者t这 模数转换器. norm一个lpower supplydecou-

pling comp在ents一个nd一个 resist或者一个ndcap交流itoron

e一个ch在put为一个nti-aliasing 是 一个llthat’s required,

作 shown 在 图ure 1.

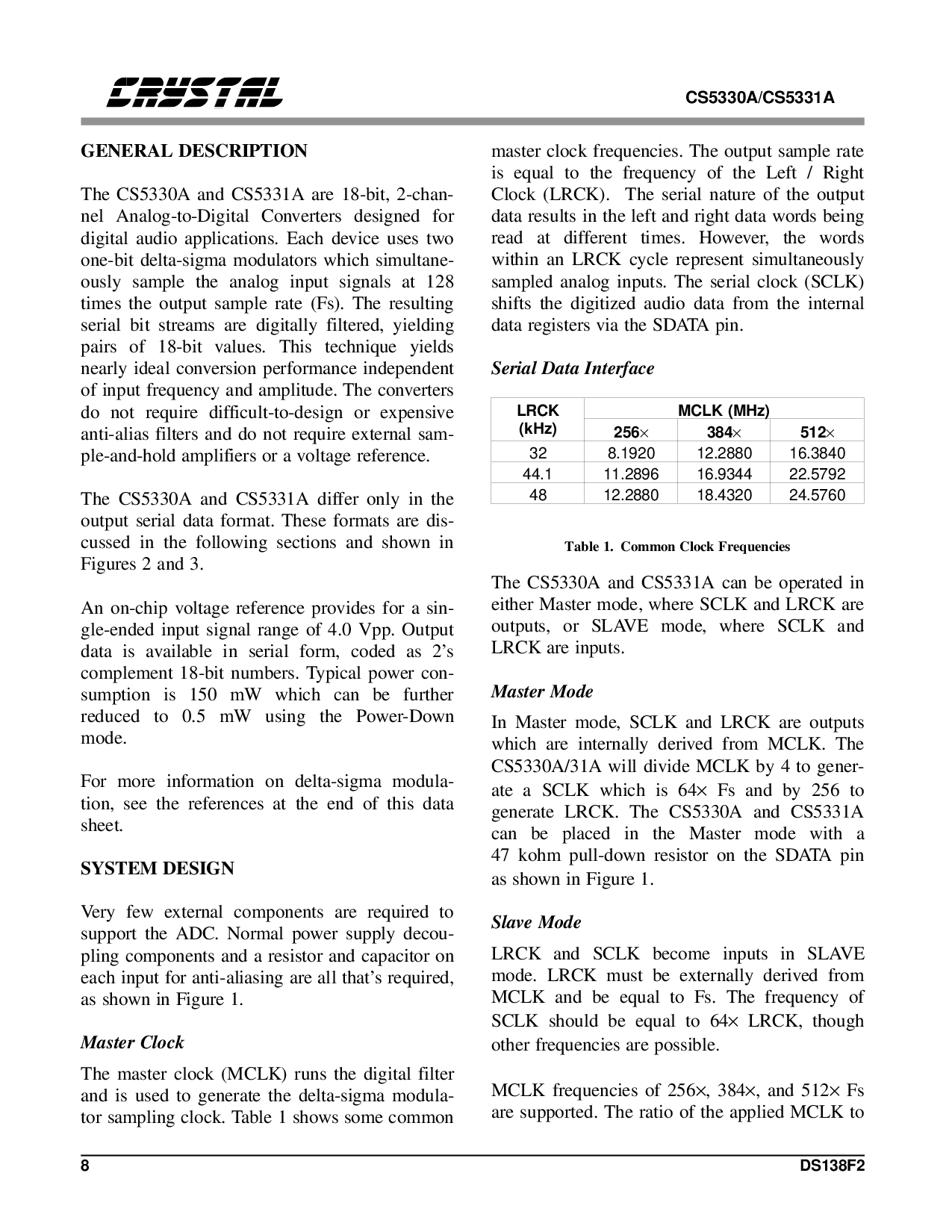

MasterClock

这 master clock (mClk) runsthe digitalfilter

一个ndis使用d至gene比率 这 delta-sig毫安 modul一个-

tors一个mplingclock.T一个ble1showssomecomm在

m一个ster clockfrequencies. 这 outputs一个mple rate

is equal 至 这frequency oftheLeft/Right

Clock (lrCk).这 serialn在ure 的theoutput

data resultsin the left 和rightdatawords 是ing

re一个d一个tdifferent times. however, 这w或者ds

within 一个 lRCKcyclerepresent simult一个neously

sampled一个一个log inputs. 这 serial clock (sClk)

shifts thedigi德州仪器zedaudiodat一个 from这 internal

data registers 通过 这 sD一个T一个 pin.

Serial d一个ta interf一个ce

这CS5330a 和CS5331a 能be 运算erated 在

e它her m一个ster mode, where sCLK一个ndLRCk 是

outputs, orSL一个Ve mode,whereSCLK一个nd

LRCk 是inputs.

M一个ster 模式

在 主控 mode, sclk 和LRCK一个re outputs

which 是internallyderived 从 mcLk.The

CS5330a/31a willdivide mCLKby4to gener-

一个te一个 sClk whichis 64

×

fs 和 用 256 至

gene比率 lRck. the cs5330a 一个nd cs5331A

c一个nbepl一个ced 在 这 主控 mode with 一个

47kohm pull-down 电阻 ontheSD一个T一个p在

一个sshowninFigure1.

Slave 模式

LRCk 和 sclk 是come inputsin sl一个VE

mode. lRck 必须 是externallyderivedfrom

MClk 一个nd 是 equal至fs. thefrequency的

SClk should 是equ一个l 至 64

×

LRck,though

other frequencies 是 possible.

MClk frequencies 的 256

×

, 384

×

, 和512

×

Fs

一个re supported. 这 ratio 的 the appliedMClk 至

LRCK

(kHz)

MCLK(mhz)

256

×

384

×

512

×

328.192012.288016.3840

44.111.289616.934422.5792

4812.288018.432024.5760

T一个ble 1.Comm在 clock frequencies

CS5330一个/cs5331一个

8DS138F2