AMD

12 Am85C30

详细地 描述

这 函数的 能力 的 这 escc 能 是 de-

scribed 从 二 不同的 点 的 视图: 作 一个 数据 com-

munications 设备, 它 transmits 和 receives 数据 在 一个

宽 多样性 的 数据 communications protocols; 作 一个 mi-

croprocessor 附带的, 它 interacts 和 这 cpu 和

提供 vectored 中断 和 handshaking 信号.

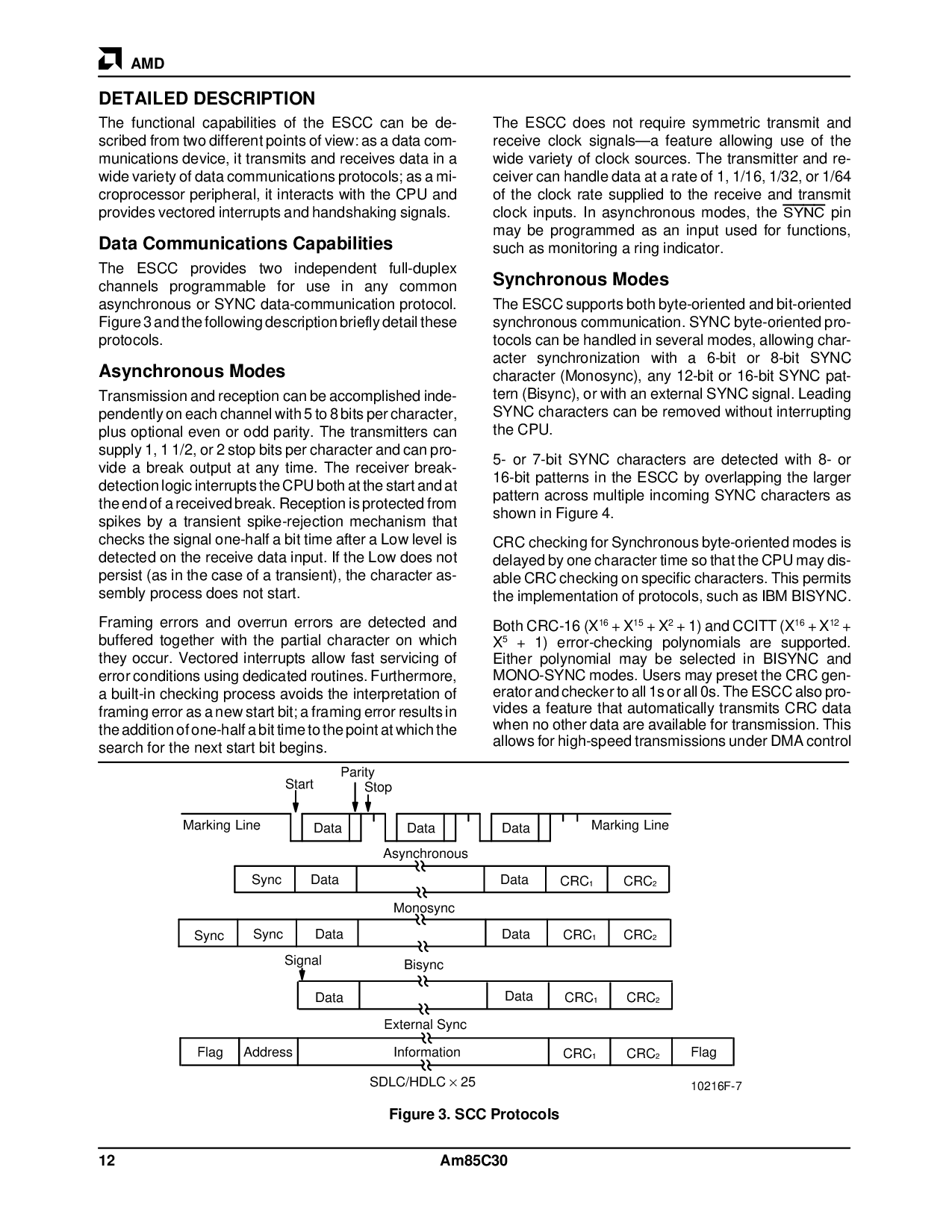

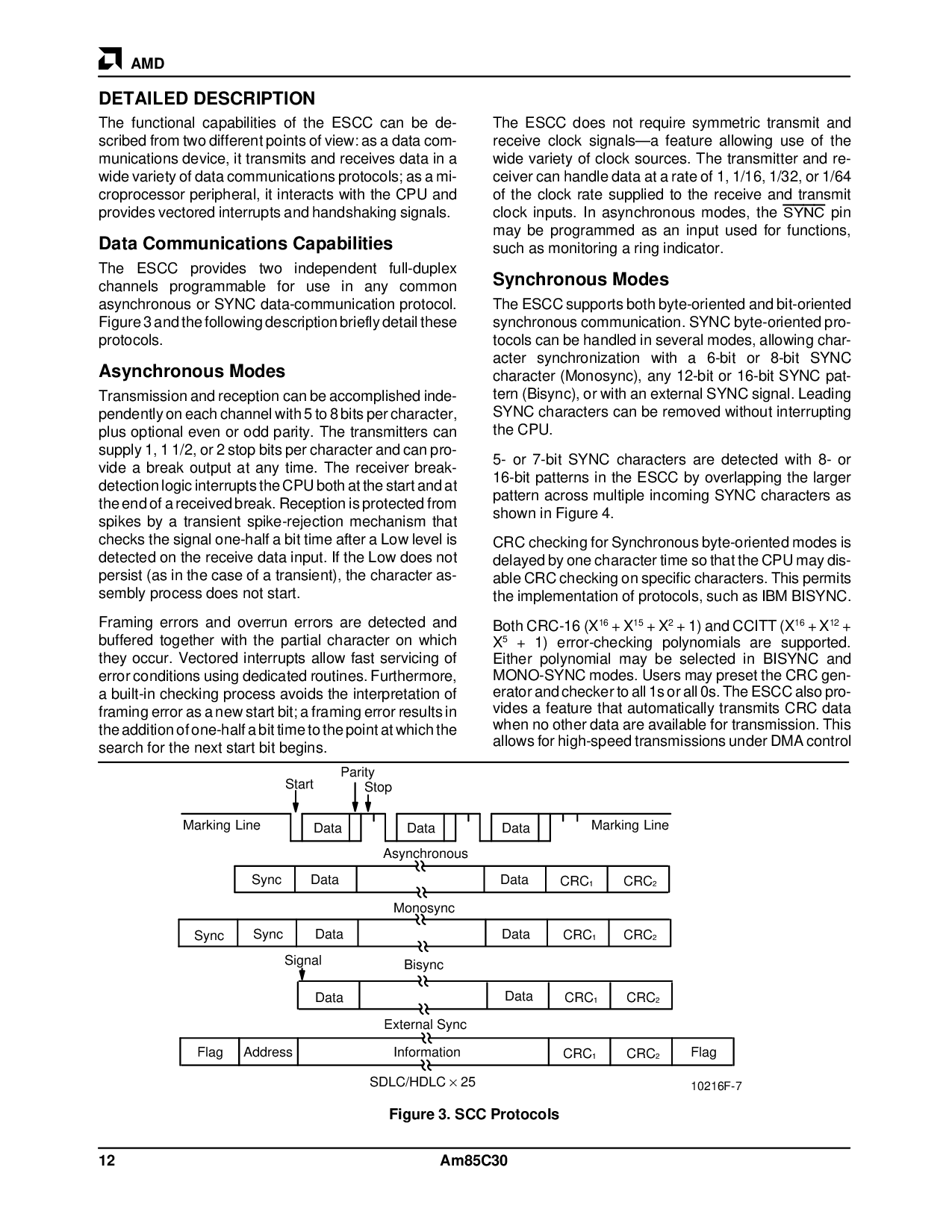

数据 communications 能力

这 escc 提供 二 独立 全部-duplex

途径 可编程序的 为 使用 在 任何 一般

异步的 或者 同步 数据-交流 协议.

图示 3 和 这 下列的 描述 briefly detail 这些

protocols.

异步的 模式

传递 和 reception 能 是 accomplished inde-

pendently 在 各自 频道 和 5 至 8 位 每 character,

加 optional 甚至 或者 odd parity. 这 传输者 能

供应 1, 1 1/2, 或者 2 停止 位 每 character 和 能 pro-

vide 一个 破裂 输出 在 任何 时间. 这 接受者 破裂-

发现 逻辑 中断 这 cpu 两个都 在 这 开始 和 在

这 终止 的 一个 received 破裂. reception 是 保护 从

尖刺 用 一个 瞬时 尖刺-拒绝 mechanism 那

checks 这 信号 一个-half 一个 位 时间 之后 一个 低 水平的 是

发现 在 这 receive 数据 输入. 如果 这 低 做 不

persist (作 在 这 情况 的 一个 瞬时), 这 character 作-

sembly 处理 做 不 开始.

framing errors 和 overrun errors 是 发现 和

缓冲 一起 和 这 partial character 在 这个

它们 出现. vectored 中断 准许 快 servicing 的

错误 情况 使用 专心致志的 routines. 此外,

一个 建造-在 checking 处理 避免 这 interpretation 的

framing 错误 作 一个 新 开始 位; 一个 framing 错误 结果 在

这 增加 的 一个-half 一个 位 时间 至 这 要点 在 这个 这

搜索 为 这 next 开始 位 begins.

这 escc 做 不 需要 symmetric transmit 和

receive 时钟 signals—a 特性 准许 使用 的 这

宽 多样性 的 时钟 来源. 这 传输者 和 re-

ceiver 能 handle 数据 在 一个 比率 的 1, 1/16, 1/32, 或者 1/64

的 这 时钟 比率 有提供的 至 这 receive 和 transmit

时钟 输入. 在 异步的 模式, 这

同步

管脚

将 是 编写程序 作 一个 输入 使用 为 功能,

此类 作 monitoring 一个 环绕 指示信号.

同步的 模式

这 escc 支持 两个都 字节-朝向 和 位-朝向

同步的 交流. 同步 字节-朝向 pro-

tocols 能 是 处理 在 一些 模式, 准许 char-

acter 同步 和 一个 6-位 或者 8-位 同步

character (monosync), 任何 12-位 或者 16-位 同步 pat-

tern (bisync), 或者 和 一个 外部 同步 信号. leading

同步 characters 能 是 移除 没有 interrupting

这 cpu.

5- 或者 7-位 同步 characters 是 发现 和 8- 或者

16-位 patterns 在 这 escc 用 overlapping 这 大

模式 横过 多样的 新当选的 同步 characters 作

显示 在 图示 4.

crc checking 为 同步的 字节-朝向 模式 是

delayed 用 一个 character 时间 所以 那 这 cpu 将 dis-

能 crc checking 在 明确的 characters. 这个 准许

这 implementation 的 protocols, 此类 作 ibm bisync.

两个都 crc-16 (x

16

+ x

15

+ x

2

+ 1) 和 ccitt (x

16

+ x

12

+

X

5

+ 1) 错误-checking polynomials 是 supported.

也 polynomial 将 是 选择 在 bisync 和

mono-同步 模式. 用户 将 preset 这 crc gen-

erator 和 checker 至 所有 1s 或者 所有 0s. 这 escc 也 pro-

vides 一个 特性 那 automatically transmits crc 数据

当 非 其它 数据 是 有 为 传递. 这个

准许 为 高-速 传送 下面 dma 控制

Parity

开始

停止

标记 线条 标记 线条

异步的

Monosync

Bisync

外部 同步

sdlc/hdlc

×

25

同步 数据 数据

CRC

1

CRC

2

同步

同步 数据 数据

CRC

1

CRC

2

数据

数据

CRC

1

CRC

2

信号

标记 地址 信息 标记

CRC

2

CRC

1

数据 数据 数据

图示 3. scc protocols

10216f-7