16mb: x16 它 sdram micron 技术, inc., reserves 这 正确的 至 改变 产品 或者 规格 没有 注意.

16msdramx16it.p65

–

rev. 5/99 ©1999, micron 技术, 公司

8

16mb: x16

它 sdram

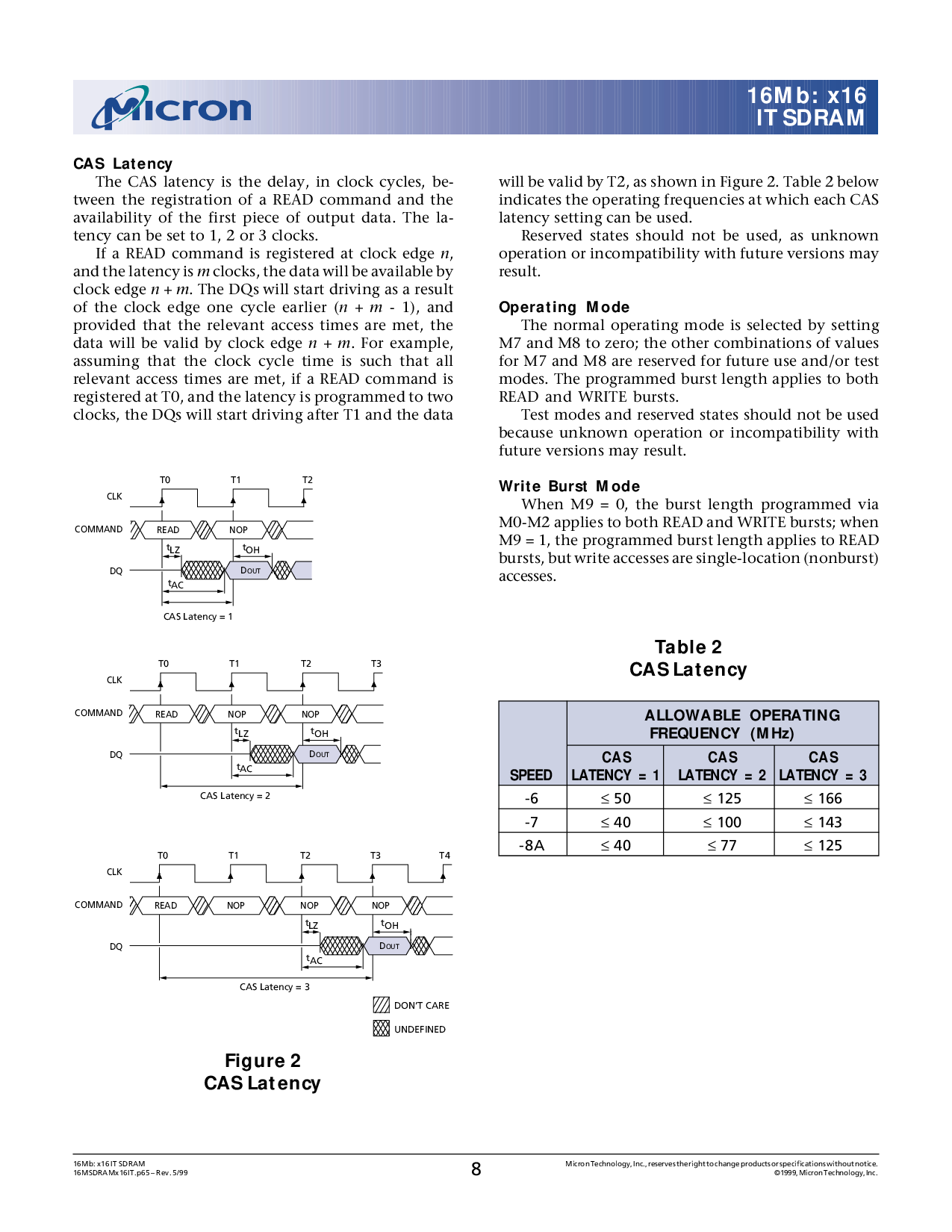

将 是 有效的 用 t2, 作 显示 在 图示 2. 表格 2 在下

indicates 这 运行 发生率 在 这个 各自 cas

latency 设置 能 是 使用.

保留 states 应当 不 是 使用, 作 unknown

运作 或者 incompatibility 和 future 版本 将

结果.

运行 模式

这 正常的 运行 模式 是 选择 用 设置

m7 和 m8 至 零; 这 其它 结合体 的 值

为 m7 和 m8 是 保留 为 future 使用 和/或者 测试

模式. 这 编写程序 burst 长度 应用 至 两个都

读 和 写 bursts.

测试 模式 和 保留 states 应当 不 是 使用

因为 unknown 运作 或者 incompatibility 和

future 版本 将 结果.

写 burst 模式

当 m9 = 0, 这 burst 长度 编写程序 通过

m0-m2 应用 至 两个都 读 和 写 bursts; 当

m9 = 1, 这 编写程序 burst 长度 应用 至 读

bursts, 但是 写 accesses 是 单独的-location (nonburst)

accesses.

表格 2

cas latency

cas latency

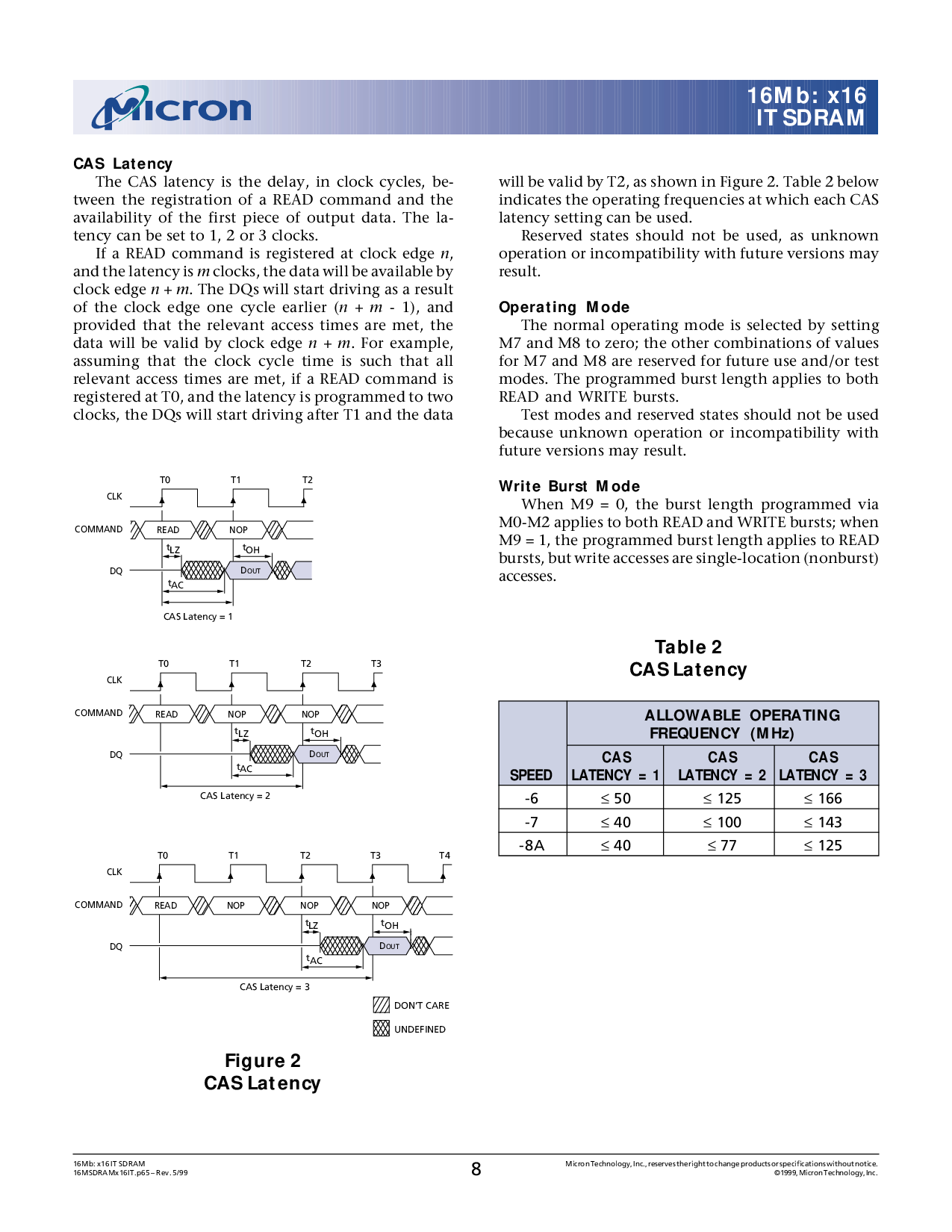

这 cas latency 是 这 延迟, 在 时钟 循环, 是-

tween 这 registration 的 一个 读 command 和 这

有效性 的 这 第一 片 的 输出 数据. 这 la-

tency 能 是 设置 至 1, 2 或者 3 clocks.

如果 一个 读 command 是 注册 在 时钟 边缘

n

,

和 这 latency 是

m

clocks, 这 数据 将 是 有 用

时钟 边缘

n + m

. 这 dqs 将 开始 驱动 作 一个 结果

的 这 时钟 边缘 一个 循环 早期 (

n + m

- 1), 和

提供 那 这 相关的 进入 时间 是 符合, 这

数据 将 是 有效的 用 时钟 边缘

n + m

. 为 例子,

假设 那 这 时钟 循环 时间 是 此类 那 所有

相关的 进入 时间 是 符合, 如果 一个 读 command 是

注册 在 t0, 和 这 latency 是 编写程序 至 二

clocks, 这 dqs 将 开始 驱动 之后 t1 和 这 数据

容许的 运行

频率 (mhz)

CAS CAS CAS

速 latency = 1 latency = 2 latency = 3

-6

≤

50

≤

125

≤

166

-7

≤

40

≤

100

≤

143

-8a

≤

40

≤

77

≤

125

图示 2

cas latency

CLK

DQ

T2T1 T3T0

cas latency = 3

LZ

D

输出

t

OH

t

COMMAND

NOPREAD

t

交流

NOP

T4

NOP

DON

’

t 小心

未阐明的

CLK

DQ

T2T1T0

cas latency = 1

LZ

D

输出

t

OH

t

COMMAND

NOPREAD

t

交流

CLK

DQ

T2T1 T3T0

cas latency = 2

LZ

D

输出

t

OH

t

COMMAND

NOPREAD

t

交流

NOP