10

商业的 和 工业的

温度 范围

idt72v3640/50/60/70/80/90/110 3.3v 高 密度 supersync ii

TM

36-位 先进先出

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

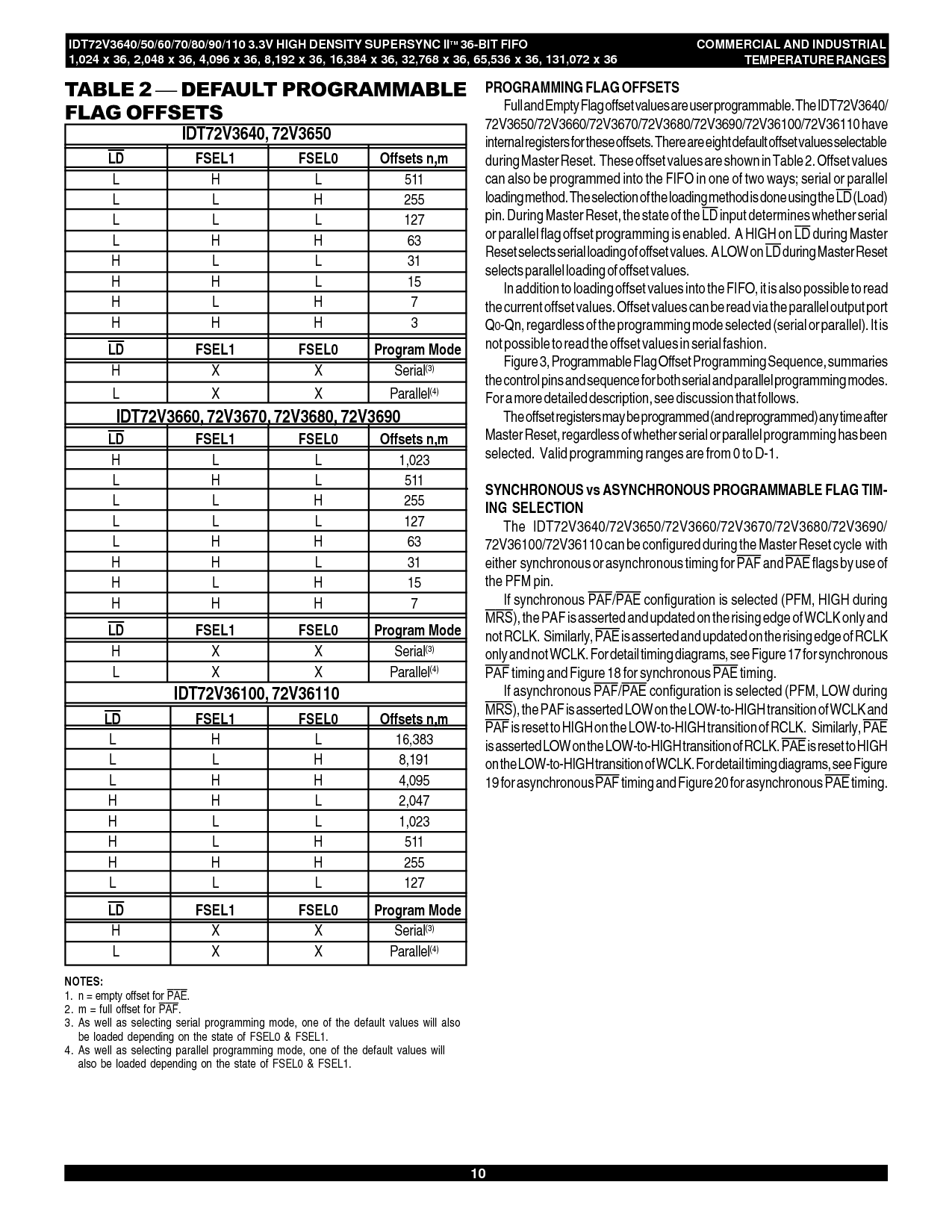

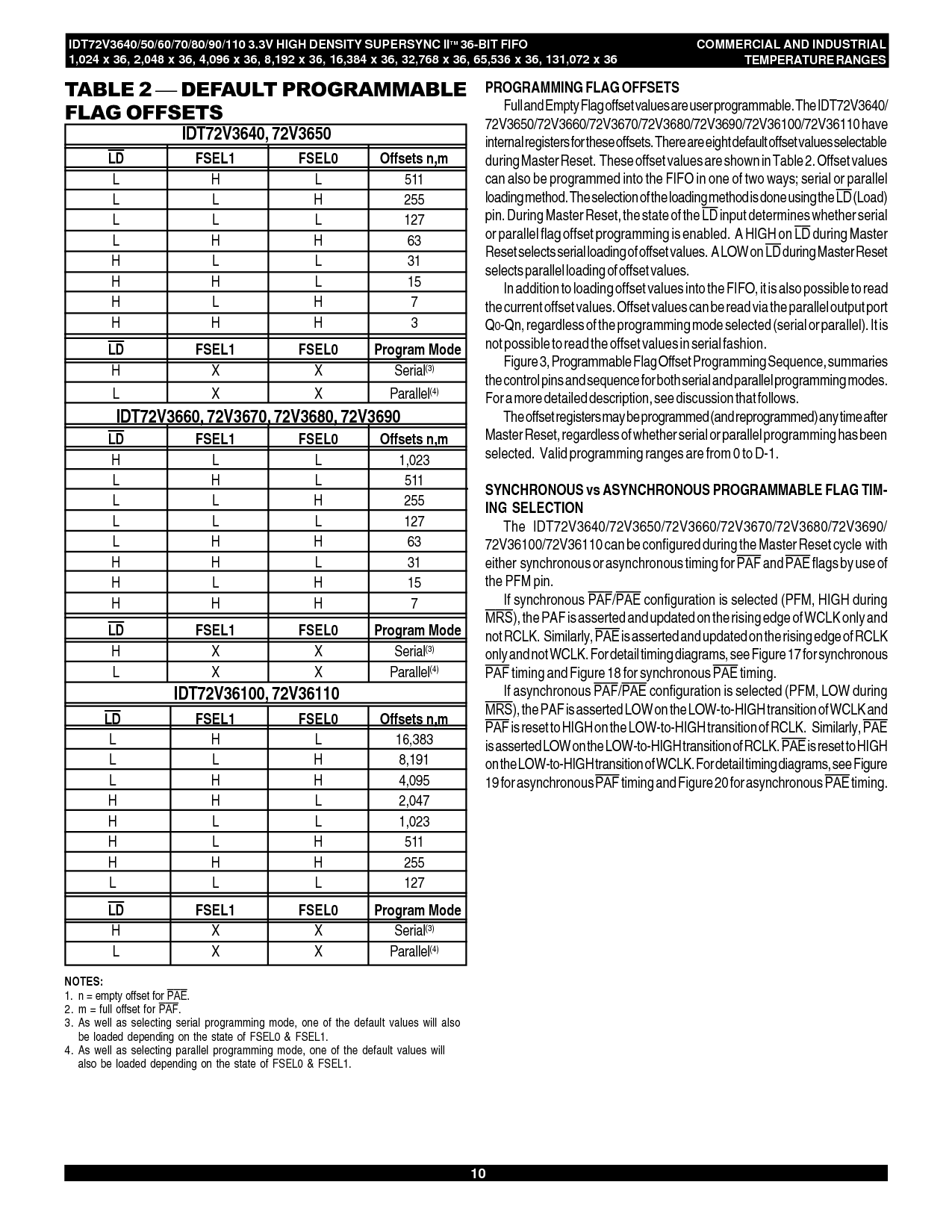

程序编制 标记 补偿

全部 和 empty 标记 补偿 值 是 用户 可编程序的. 这 idt72v3640/

72v3650/72v3660/72v3670/72v3680/72v3690/72v36100/72v36110 有

内部的 寄存器 为 这些 补偿. 那里 是 第八 default 补偿 值 可选择的

在 主控 重置. 这些 补偿 值 是 显示 在 表格 2. 补偿 值

能 也 是 编写程序 在 这 先进先出 在 一个 的 二 方法; 串行 或者 并行的

加载 方法. 这 选择 的 这 加载 方法 是 完毕 使用 这

LD

(加载)

管脚. 在 主控 重置, 这 状态 的 这

LD

输入 确定 whether 串行

或者 并行的 标记 补偿 程序编制 是 使能. 一个 高 在

LD

在 主控

重置 选择 串行 加载 的 补偿 值. 一个 低 在

LD

在 主控 重置

选择 并行的 加载 的 补偿 值.

在 增加 至 加载 补偿 值 在 这 先进先出, 它 是 也 可能 至 读

这 电流 补偿 值. 补偿 值 能 是 读 通过 这 并行的 输出 端口

Q

0

-qn, regardless 的 这 程序编制 模式 选择 (串行 或者 并行的). 它 是

不 可能 至 读 这 补偿 值 在 串行 fashion.

图示 3, 可编程序的 标记 补偿 程序编制 sequence, summaries

这 控制 管脚 和 sequence 为 两个都 串行 和 并行的 程序编制 模式.

为 一个 更多 详细地 描述, 看 discussion 那 跟随.

这 补偿 寄存器 将 是 编写程序 (和 reprogrammed) 任何 时间 之后

主控 重置, regardless 的 whether 串行 或者 并行的 程序编制 有 被

选择. 有效的 程序编制 范围 是 从 0 至 d-1.

同步的 vs 异步的 可编程序的 标记 tim-

ing 选择

这 idt72v3640/72v3650/72v3660/72v3670/72v3680/72v3690/

72v36100/72v36110 能 是 配置 在 这 主控 重置 循环 和

也 同步的 或者 异步的 定时 为

PAF

和

PAE

flags 用 使用 的

这 pfm 管脚.

如果 同步的

PAF

/

PAE

配置 是 选择 (pfm, 高 在

MRS

), 这 paf 是 asserted 和 updated 在 这 rising 边缘 的 wclk 仅有的 和

不 rclk. similarly,

PAE

是 asserted 和 updated 在 这 rising 边缘 的 rclk

仅有的 和 不 wclk. 为 detail 定时 图解, 看 图示 17 为 同步的

PAF

定时 和 图示 18 为 同步的

PAE

定时.

如果 异步的

PAF

/

PAE

配置 是 选择 (pfm, 低 在

MRS

), 这 paf 是 asserted 低 在 这 低-至-高 转变 的 wclk 和

PAF

是 重置 至 高 在 这 低-至-高 转变 的 rclk. similarly,

PAE

是 asserted 低 在 这 低-至-高 转变 的 rclk.

PAE

是 重置 至 高

在 这 低-至-高 转变 的 wclk. 为 detail 定时 图解, 看 图示

19 为 异步的

PAF

定时 和 图示 20 为 异步的

PAE

定时.

idt72v3640, 72v3650

LD

FSEL1 FSEL0 补偿 n,m

LH L511

L L H 255

L L L 127

LH H63

HL L31

HH L15

HL H7

HH H3

LD

FSEL1 FSEL0 程序 模式

H X X 串行

(3)

L X X 并行的

(4)

idt72v3660, 72v3670, 72v3680, 72v3690

LD

FSEL1 FSEL0 补偿 n,m

H L L 1,023

LH L511

L L H 255

L L L 127

LH H63

HH L31

HL H15

HH H7

LD

FSEL1 FSEL0 程序 模式

H X X 串行

(3)

L X X 并行的

(4)

idt72v36100, 72v36110

LD

FSEL1 FSEL0 补偿 n,m

L H L 16,383

L L H 8,191

L H H 4,095

H H L 2,047

H L L 1,023

HLH511

HHH255

LLL127

LD

FSEL1 FSEL0 程序 模式

H X X 串行

(3)

L X X 并行的

(4)

注释:

1. n = empty 补偿 为

PAE

.

2. m = 全部 补偿 为

PAF

.

3. 作 好 作 selecting 串行 程序编制 模式, 一个 的 这 default 值 将 也

是 承载 取决于 在 这 状态 的 fsel0 &放大; fsel1.

4. 作 好 作 selecting 并行的 程序编制 模式, 一个 的 这 default 值 将

也 是 承载 取决于 在 这 状态 的 fsel0 &放大; fsel1.