12

商业的 和 工业的

温度 范围

idt72v3640/50/60/70/80/90/110 3.3v 高 密度 supersync ii

TM

36-位 先进先出

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

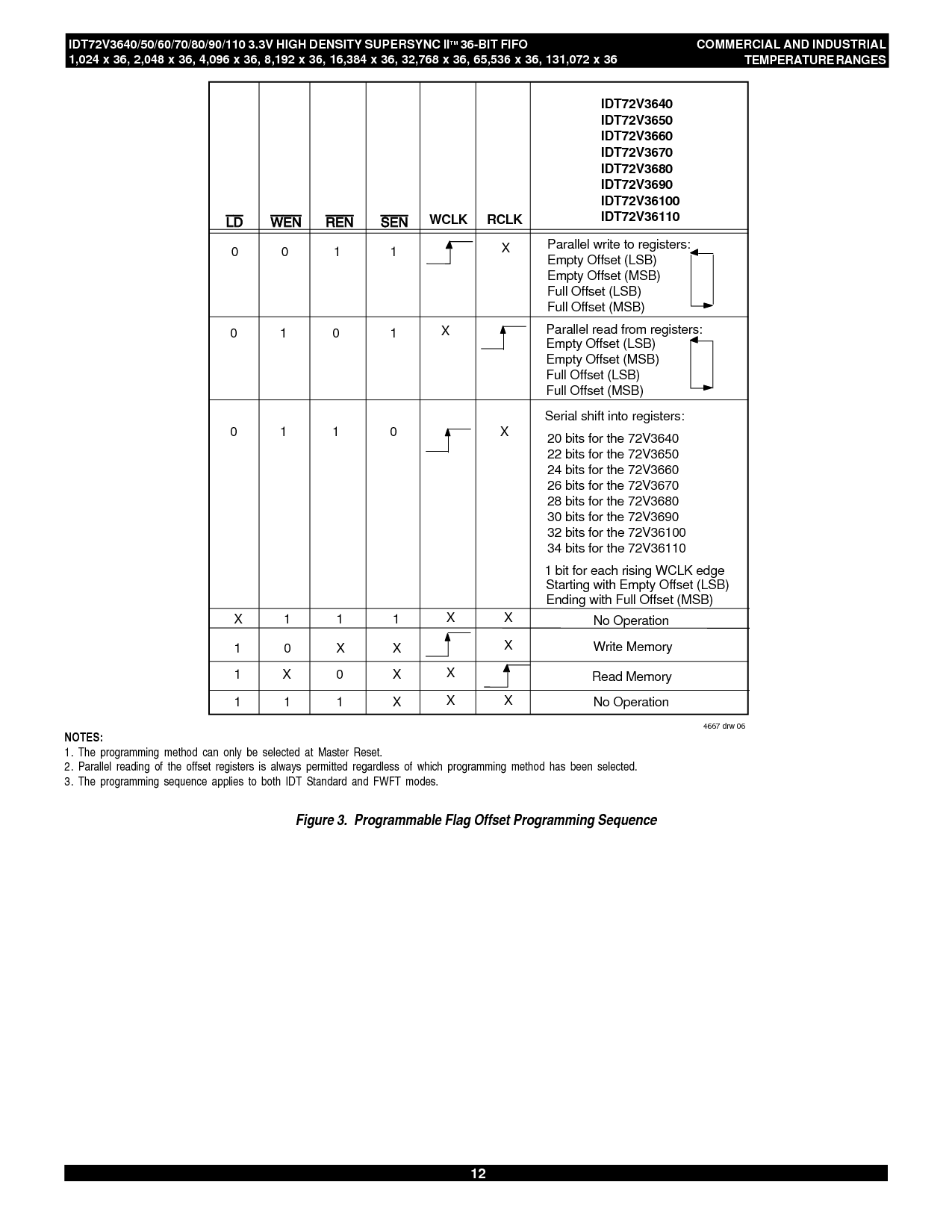

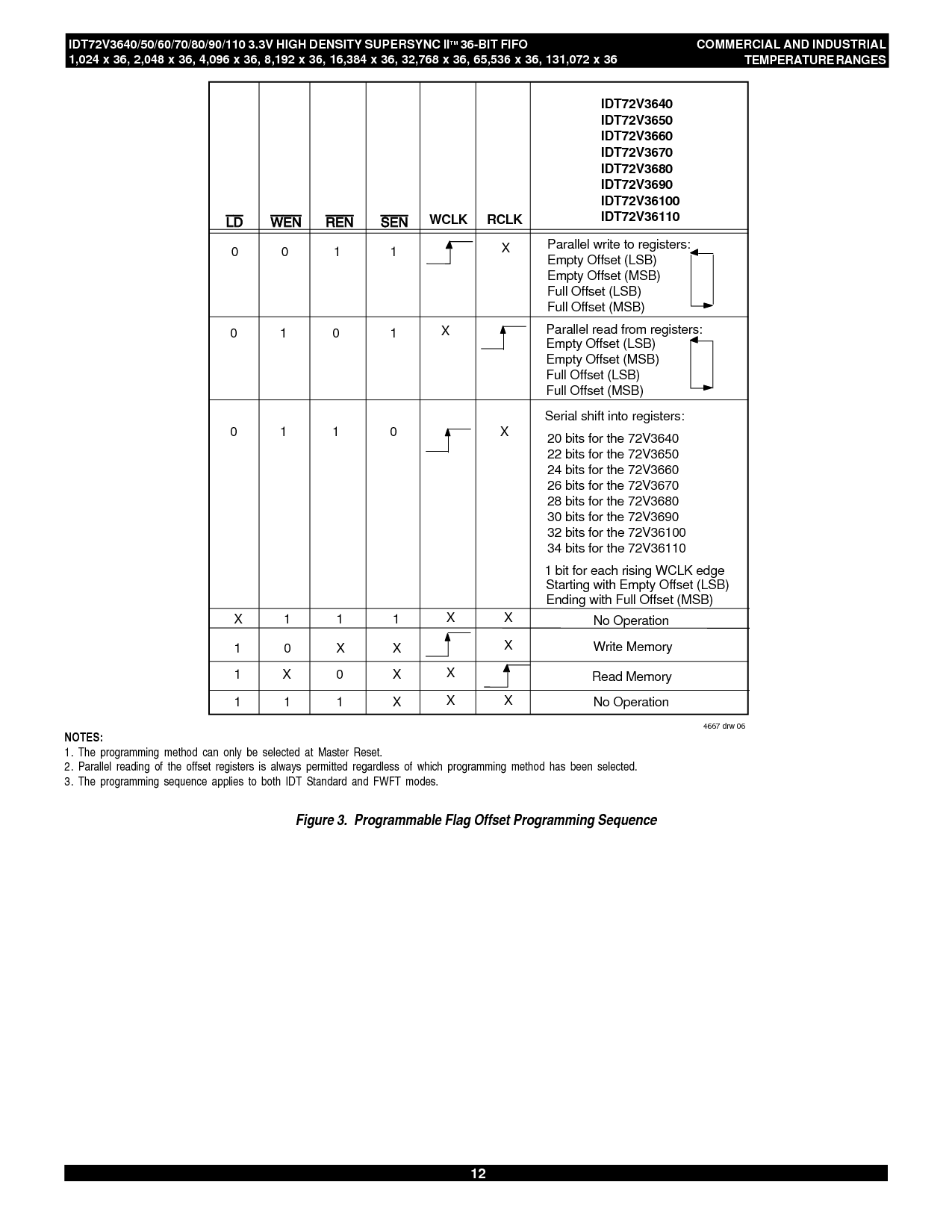

图示 3. 可编程序的 标记 补偿 程序编制 sequence

注释:

1. 这 程序编制 方法 能 仅有的 是 选择 在 主控 重置.

2. 并行的 读 的 这 补偿 寄存器 是 总是 permitted regardless 的 这个 程序编制 方法 有 被 选择.

3. 这 程序编制 sequence 应用 至 两个都 idt 标准 和 fwft 模式.

WCLK RCLK

X

X

XX

X

X

XX

LD

0

0

X

1

1

1

0

WEN

0

1

1

0

X

1

1

REN

1

0

1

X

0

1

1X

SEN

1

1

1

X

X

X

0

非 运作

写 记忆

读 记忆

非 运作

并行的 写 至 寄存器:

empty 补偿 (lsb)

empty 补偿 (msb)

全部 补偿 (lsb)

全部 补偿 (msb)

IDT72V3640

IDT72V3650

IDT72V3660

IDT72V3670

IDT72V3680

IDT72V3690

IDT72V36100

IDT72V36110

并行的 读 从 寄存器:

empty 补偿 (lsb)

empty 补偿 (msb)

全部 补偿 (lsb)

全部 补偿 (msb)

串行 变换 在 寄存器:

ending 和 全部 补偿 (msb)

20 位 为 这 72v3640

22 位 为 这 72v3650

24 位 为 这 72v3660

26 位 为 这 72v3670

28 位 为 这 72v3680

30 位 为 这 72v3690

32 位 为 这 72v36100

34 位 为 这 72v36110

1 位 为 各自 rising wclk 边缘

开始 和 empty 补偿 (lsb)

4667 drw 06