3-149

accesses; 一个, 如果 这 文字 operand 是 在 一个 甚至 字节

boundary 和 二, 如果 它 是 在 一个 odd 字节 boundary. 除了

为 这 效能 penalty

,

这个 翻倍 进入 是 transpar-

ent 至 这 软件. 这 效能 penalty 做 不 出现

为 操作指南 fetches; 仅有的 文字 operands.

physically, 这 记忆 是 有组织的 作 一个 高 bank (d15-

d8) 和 一个 低 bank (d7-d0) 的 512k 字节 addressed 在 par-

allel 用 这 处理器’s 地址 线条.

字节 数据 和 甚至 地址 是 transferred 在 这 d7-d0

总线 线条, 当 odd addressed 字节 数据 (a0 高) 是 trans-

ferred 在 这 d15-d8 总线 线条. 这 处理器 提供 二

使能 信号, bhe 和 一个

0

, 至 selectively 准许 读

从 或者 writing 在 也 一个 odd 字节 location, 甚至 字节

location, 或者 两个都. 这 操作指南 stream 是 fetched 从

记忆 作 words 和 是 addressed 内部 用 这 proces-

sor 在 这 字节 水平的 作 需要.

在 referencing 文字 数据, 这 blu 需要 一个 或者 二 记忆

循环 取决于 在 whether 这 开始 字节 的 这 文字 是

在 一个 甚至 或者 odd 地址, 各自. consequently, 在 ref-

erencing 文字 operands 效能 能 是 优化 用

locating 数据 在 甚至 地址 boundaries. 这个 是 一个 espe-

cially 有用的 技巧 为 使用 这 堆栈, 自从 odd 地址

references 至 这 堆栈 将 反而 影响 这 context

切换 时间 为 中断 处理 或者 task multiplexing.

确实 locations 在 记忆 是 保留 为 specific cpu

行动 (看 图示 2). locations 从 地址 ffff0h

通过 fffffh 是 保留 为 行动 包含 一个 jump

至 这 最初的 程序 加载 routine. 下列的 重置, 这

cpu 将 总是 begin 执行 在 location ffff0h 在哪里

这 jump 必须 是 located. locations 00000h 通过 003ffh

是 保留 为 中断 行动. 各自 的 这 256 可能

中断 维护 routines 是 accessed thru 它的 自己的 一双 的 16-

位 pointers (段 地址 pointer 和 补偿 地址

pointer). 这 first pointer, 使用 作 这 补偿 地址, 是

承载 在 这 lp 和 这 第二 pointer, 这个 designates

这 根基 地址 是 承载 在 这 cs. 在 这个 要点 程序

控制 是 transferred 至 这 中断 routine. 这 pointer ele-

ments 是 assumed 至 有 被 贮存 在 这 各自的

places 在 保留 记忆 较早的 至 occurrence 的 中断.

最小 和 最大 运作 模式

这 (所需的)东西 为 支承的 最小 和 最大

80c86 系统 是 sufficiently 不同的 那 它们 不能 是

符合 efficiently 使用 40 uniquely defined 管脚. consequently,

这 80c86 是 配备 和 一个 strap 管脚 (mn/

mx) 这个

defines 这 系统 configuration. 这 definition 的 一个 确实

subset 的 这 管脚 改变, 依赖 在 这 情况 的 这

strap 管脚. 当 这 mn/

mx 管脚 是 strapped 至 地, 这

80c86 defines 管脚 24 通过 31 和 34 在 最大 模式.

当 这 mn/

mx 管脚 是 strapped 至 v

CC

, 这 80c86 gener-

ates 总线 控制 信号 它自己 在 管脚 24 通过 31 和 34.

这 最小 模式 80c86 能 是 使用 和 也 一个 multi-

plexed 或者 demultiplexed 总线. 这个 architecture 提供 这

80c86 处理 电源 在 一个 高级地 整体的 表格.

这 demultiplexed 模式 需要 二 82c82 latches (为 64k

addressability) 或者 三 82c82 latches (为 一个 全部 megabyte 的

寻址). 一个 82c86 或者 82c87 transceiver 能 也 是

使用 如果 数据 总线 buffering 是 必需的. (看 图示 6a.) 这

80c86 提供

den 和 dt/r 至 控制 这 transceiver, 和

ale 至 获得 这 地址. 这个 configuration 的 这 最小

模式 提供 这 标准 demultiplexed 总线 结构 和

重的 总线 buffering 和 relaxed 总线 定时 (所需的)东西.

这 最大 模式 雇用 这 82c88 总线 控制 (看

图示 6b). 这 82c88 decodes 状态 线条

s0, s1 和 s2,

和 提供 这 系统 和 所有 总线 控制 信号.

移动的 这 总线 控制 至 这 82c88 提供 更好的 源

和 下沉 电流 能力 至 这 控制 线条, 和 frees 这

80c86 管脚 为 扩展 大 系统 特性. 硬件

锁, queue 状态, 和 二 要求/grant 接口 是 pro-

vided 用 这 80c86 在 最大 模式. 这些 特性 准许

coprocessors 在 local 总线 和 偏远的 总线 configurations.

总线 运作

这 80c86 有 一个 联合的 地址 和 数据 总线 com-

monly 涉及 至 作 一个 时间 多路复用 总线. 这个 技巧

提供 这 大多数 efficient 使用 的 管脚 在 这 处理器

当 permitting 这 使用 的 一个 标准 40 含铅的 包装. 这个

“local bus” 能 是 缓冲 直接地 和 使用 全部地 这

系统 和 地址 闭锁 提供 在 记忆 和 i/o

modules. 在 增加, 这 总线 能 也 是 demultiplexed 在

这 处理器 和 一个 单独的 设置 的 82c82 地址 latches 如果 一个

标准 非-多路复用 总线 是 desired 为 这 系统.

各自 处理器 总线 循环 组成 的 在 least 四 clk

循环. 这些 是 涉及 至 作 t1, t2, t3 和 t4 (看 图-

ure 3). 这 地址 是 emitted 从 这 处理器 在 t1

和 数据 转移 occurs 在 这 总线 在 t3 和 t4. t2 是

使用 primarily 为 changing 这 方向 的 这 总线 在

读 行动. 在 这 事件 那 一个 “not ready” indication

是 给 用 这 addressed 设备, “wait” states (tw) 是

inserted 在 t3 和 t4. 各自 inserted wait 状态 是 这

一样 持续时间 作 一个 clk 循环. 时期 能 出现 在

80c86 驱动 总线 循环. 这些 是 涉及 至 作 idle”

states (t

I

) 或者 inactive clk 循环. 这 处理器 使用 这些

循环 为 内部的 housekeeping 和 处理.

在 t1 的 任何 总线 循环, 这 ale (地址 获得 使能)

信号 是 emitted (用 也 这 处理器 或者 这 82c88 总线

控制, 取决于 在 这 mn/

mx strap). 在 这 trailing

边缘 的 这个 脉冲波, 一个 有效的 地址 和 确实 状态 infor-

mation 为 这 循环 将 是 latched.

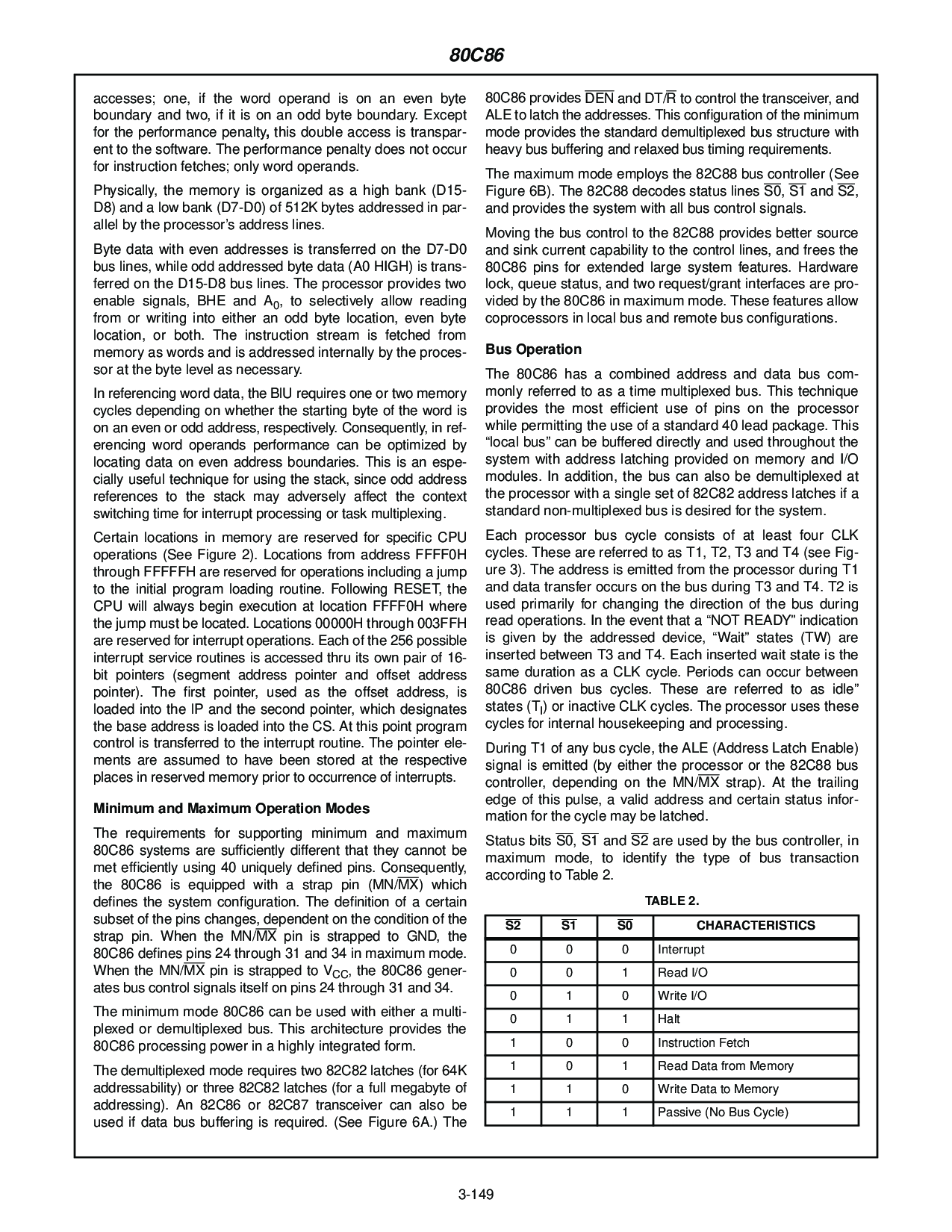

状态 位

s0, s1 和 s2 是 使用 用 这 总线 控制, 在

最大 模式, 至 identify 这 类型 的 总线 transaction

符合 至 表格 2.

表格 2.

S2 S1 S0 特性

0 0 0 中断

0 0 1 读 i/o

0 1 0 写 i/o

0 1 1 Halt

1 0 0 操作指南 fetch

1 0 1 读 数据 从 记忆

1 1 0 写 数据 至 记忆

1 1 1 被动的 (非 总线 循环)

80C86