5-53

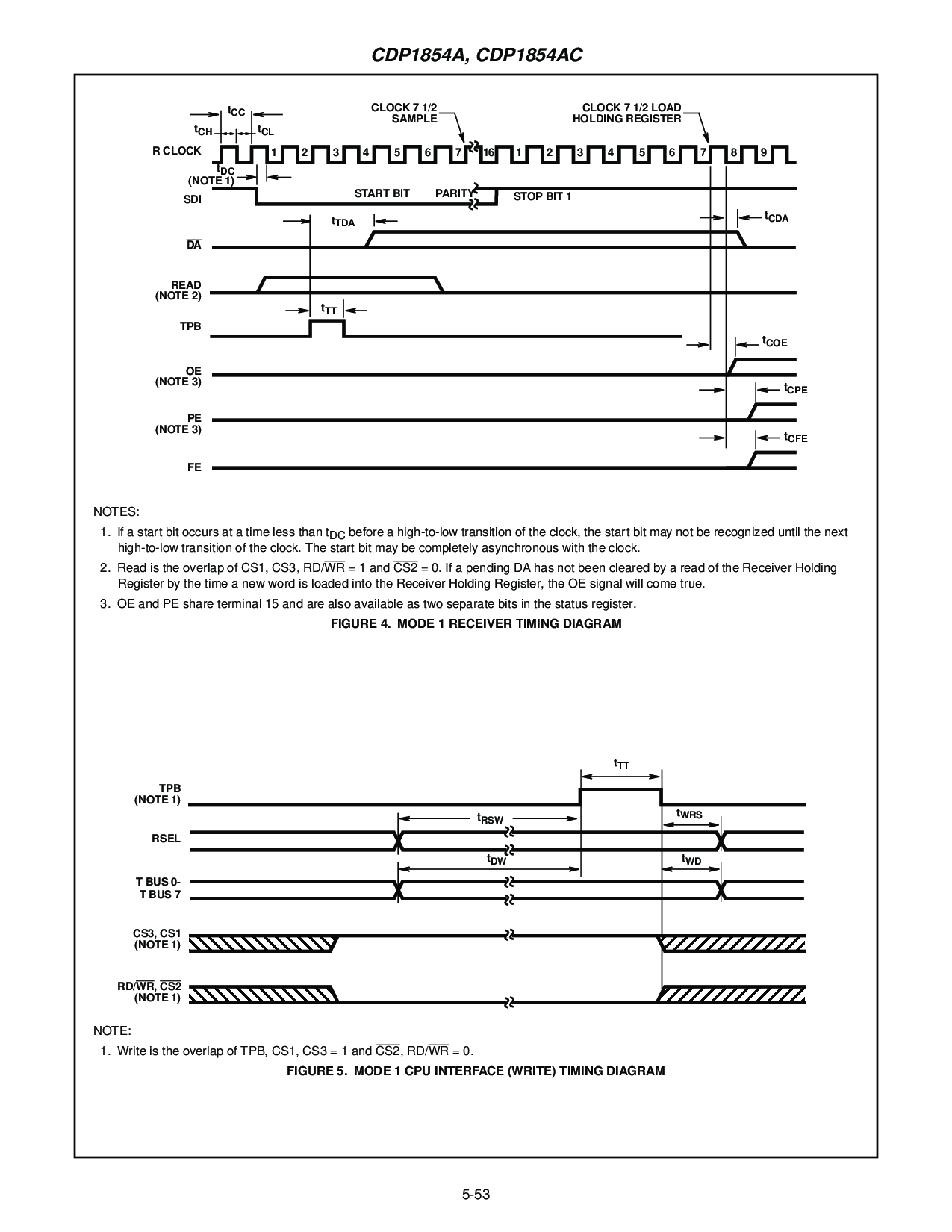

注释:

1. 如果 一个 开始 位 occurs 在 一个 时间 较少 比 t

直流

在之前 一个 高-至-低 转变 的 这 时钟, 这 开始 位 将 不 是 公认的 直到 这 next

高-至-低 转变 的 这 时钟. 这 开始 位 将 是 完全地 异步的 和 这 时钟.

2. 读 是 这 overlap 的 cs1, cs3, rd/wr = 1 和 cs2 = 0. 如果 一个 pending da 有 不 被 cleared 用 一个 读 的 这 接受者 支持

寄存器 用 这 时间 一个 新 文字 是 承载 在 这 接受者 支持 寄存器, 这 oe 信号 将 来到 真实.

3. oe 和 pe share 终端 15 和 是 也 有 作 二 独立的 位 在 这 状态 寄存器.

图示 4. 模式 1 接受者 定时 图解

r 时钟

读

t

CC

t

CL

t

CH

t

直流

12

开始 位

t

TDA

时钟 7 1/2

样本

3456716

(便条 1)

SDI

123456789

停止 位 1

时钟 7 1/2 加载

支持 寄存器

t

CDA

t

TT

t

COE

t

CPE

t

CFE

OE

PE

(便条 3)

FE

PARITY

DA

(便条 2)

TPB

(便条 3)

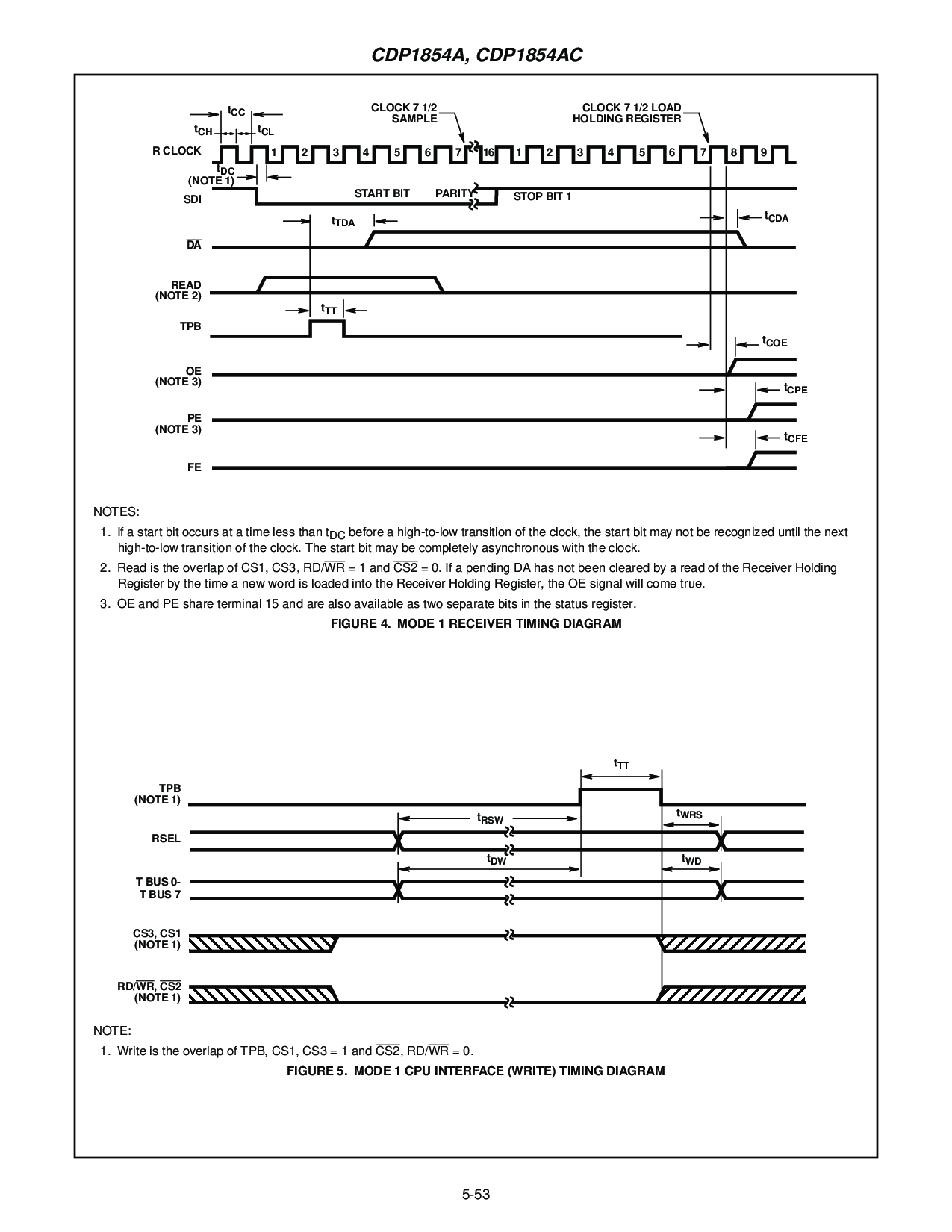

便条:

1. 写 是 这 overlap 的 tpb, cs1, cs3 = 1 和 cs2, rd/wr = 0.

图示 5. 模式 1 cpu 接口 (写) 定时 图解

t

RSW

t

WRS

t

TT

t

WD

t

DW

TPB

(便条 1)

t 总线 0-

t 总线 7

rd/

wr, CS2

(便条 1)

cs3, cs1

(便条 1)

RSEL

cdp1854a, cdp1854ac