5-49

描述 的 模式 1 运作

cdp1800-序列 微处理器

兼容 (模式 输入 = v

DD

)

initialization 和 控制

在 这 cdp1800-序列 微处理器 兼容 模式,

这 cdp1854a 是 configured 至 receive commands 和 send

状态 通过 这 微处理器 数据 总线. 这 寄存器

连接 至 这 传输者 总线 或者 这 接受者 总线 是

决定 用 这 rd/

wr 和 rsel 输入 作 跟随:

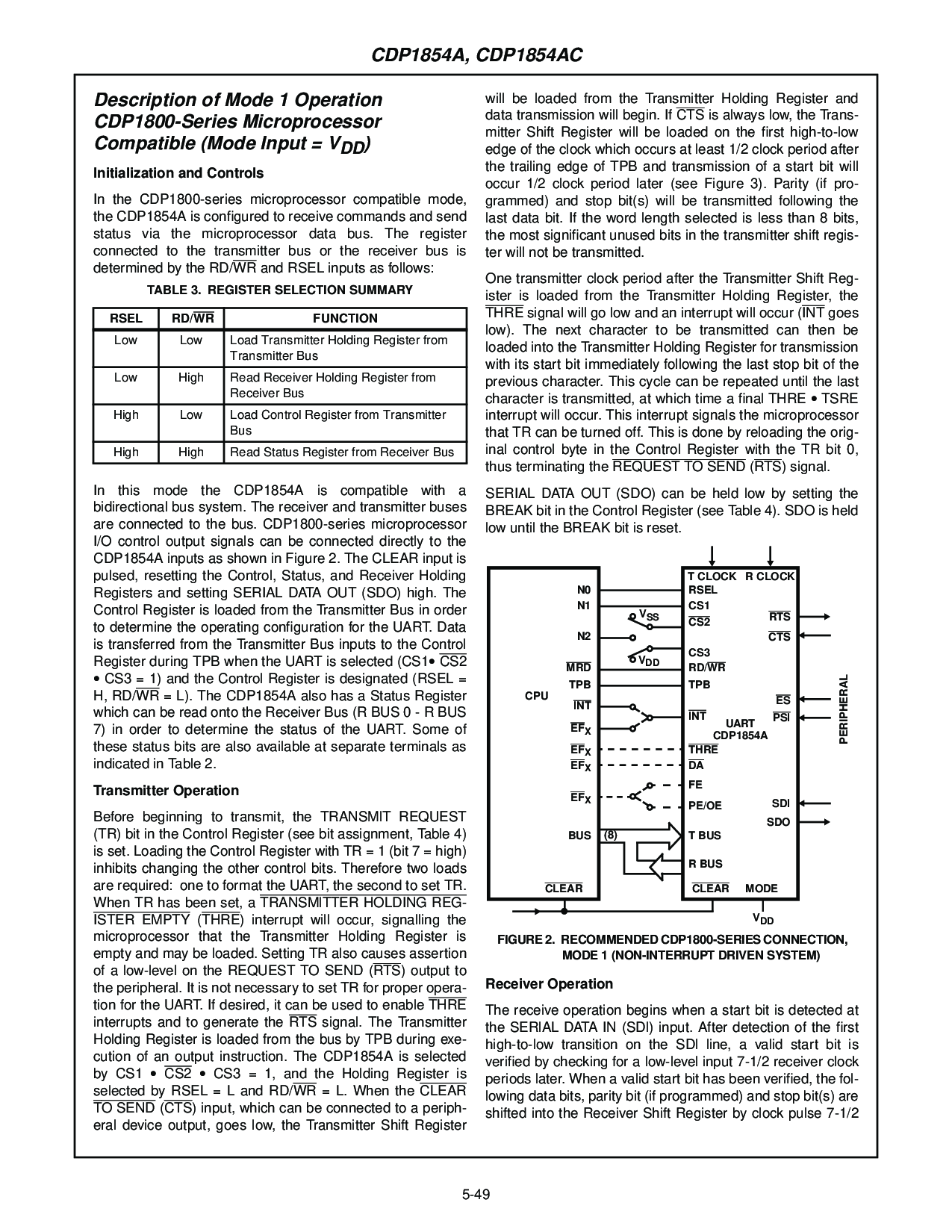

在 这个 模式 这 cdp1854a 是 兼容 和 一个

双向的 总线 系统. 这 接受者 和 传输者 buses

是 连接 至 这 总线. cdp1800-序列 微处理器

i/o 控制 输出 信号 能 是 连接 直接地 至 这

cdp1854a 输入 作 显示 在 图示 2. 这 clear 输入 是

搏动, resetting 这 控制, 状态, 和 接受者 支持

寄存器 和 设置 串行 数据 输出 (sdo) 高. 这

控制 寄存器 是 承载 从 这 传输者 总线 在 顺序

至 决定 这 运行 configuration 为 这 uart. 数据

是 transferred 从 这 传输者 总线 输入 至 这 控制

寄存器 在 tpb 当 这 uart 是 选择 (cs1

•

CS2

•

cs3 = 1) 和 这 控制 寄存器 是 designated (rsel =

h, rd/

wr = l). 这 cdp1854a 也 有 一个 状态 寄存器

这个 能 是 读 面向 这 接受者 总线 (r 总线 0 - r 总线

7) 在 顺序 至 决定 这 状态 的 这 uart. 一些 的

这些 状态 位 是 也 有 在 独立的 terminals 作

表明 在 表格 2.

传输者 运作

在之前 beginning 至 transmit, 这 transmlt 要求

(tr) 位 在 这 控制 寄存器 (看 位 分派, 表格 4)

是 设置. 加载 这 控制 寄存器 和 tr = 1 (位 7 = 高)

inhibits changing 这 其它 控制 位. 因此 二 负载

是 必需的: 一个 至 format 这 uart, 这 第二 至 设置 tr.

当 tr 有 被 设置, 一个

transmltter 支持 reg-

ister empty (thre) 中断 将 出现, signalling 这

微处理器 那 这 传输者 支持 寄存器 是

empty 和 将 是 承载. 设置 tr 也 导致 assertion

的 一个 低-水平的 在 这 要求 至 send (

Rts) 输出 至

这 附带的. 它 是 不 需要 至 设置 tr 为 恰当的 opera-

tion 为 这 uart. 如果 desired, 它 能 是 使用 至 使能

THRE

中断 和 至 发生 这

Rts 信号. 这 传输者

支持 寄存器 是 承载 从 这 总线 用 tpb 在 exe-

cution 的 一个 输出 操作指南. 这 cdp1854a 是 选择

用 cs1

•

CS2

•

cs3 = 1, 和 这 支持 寄存器 是

选择 用 rsel = l 和 rd/

wr = l. 当 这 CLEAR

To send (cts) 输入, 这个 能 是 连接 至 一个 periph-

eral 设备 输出, 变得 低, 这 传输者 变换 寄存器

将 是 承载 从 这 传输者 支持 寄存器 和

数据 传递 将 begin. 如果

cts 是 总是 低, 这 trans-

mitter 变换 寄存器 将 是 承载 在 这 first 高-至-低

边缘 的 这 时钟 这个 occurs 在 least 1/2 时钟 时期 之后

这 trailing 边缘 的 tpb 和 传递 的 一个 开始 位 将

出现 1/2 时钟 时期 后来的 (看 图示 3). parity (如果 pro-

grammed) 和 停止 位(s) 将 是 transmitted 下列的 这

last 数据 位. 如果 这 文字 长度 选择 是 较少 比 8 位,

这 大多数 significant unused 位 在 这 传输者 变换 regis-

ter 将 不 是 transmitted.

一个 传输者 时钟 时期 之后 这 传输者 变换 reg-

ister 是 承载 从 这 传输者 支持 寄存器, 这

thre 信号 将 go 低 和 一个 中断 将 出现 (int 变得

低). 这 next character 至 是 transmitted 能 然后 是

承载 在 这 传输者 支持 寄存器 为 传递

和 它的 开始 位 立即 下列的 这 last 停止 位 的 这

previous character. 这个 循环 能 是 重复的 直到 这 last

character 是 transmitted, 在 这个 时间 一个 final thre

•

TSRE

中断 将 出现. 这个 中断 信号 这 微处理器

那 tr 能 是 转变 止. 这个 是 完毕 用 reloading 这 orig-

inal 控制 字节 在 这 控制 寄存器 和 这 tr 位 0,

因此 terminating 这

要求 至 send (rts) 信号.

串行 数据 输出 (sdo) 能 是 使保持 低 用 设置 这

破裂 位 在 这 控制 寄存器 (看 表格 4). sdo 是 使保持

低 直到 这 破裂 位 是 重置.

接受者 运作

这 receive 运作 begins 当 一个 开始 位 是 发现 在

这 serlal 数据 在 (sdl) 输入. 之后 发现 的 这 first

高-至-低 转变 在 这 sdl 线条, 一个 有效的 开始 位 是

verified 用 checking 为 一个 低-水平的 输入 7-1/2 接受者 时钟

时期 后来的. 当 一个 有效的 开始 位 有 被 verified, 这 fol-

lowing 数据 位, parity 位 (如果 编写程序) 和 停止 位(s) 是

shifted 在 这 接受者 变换 寄存器 用 时钟 脉冲波 7-1/2

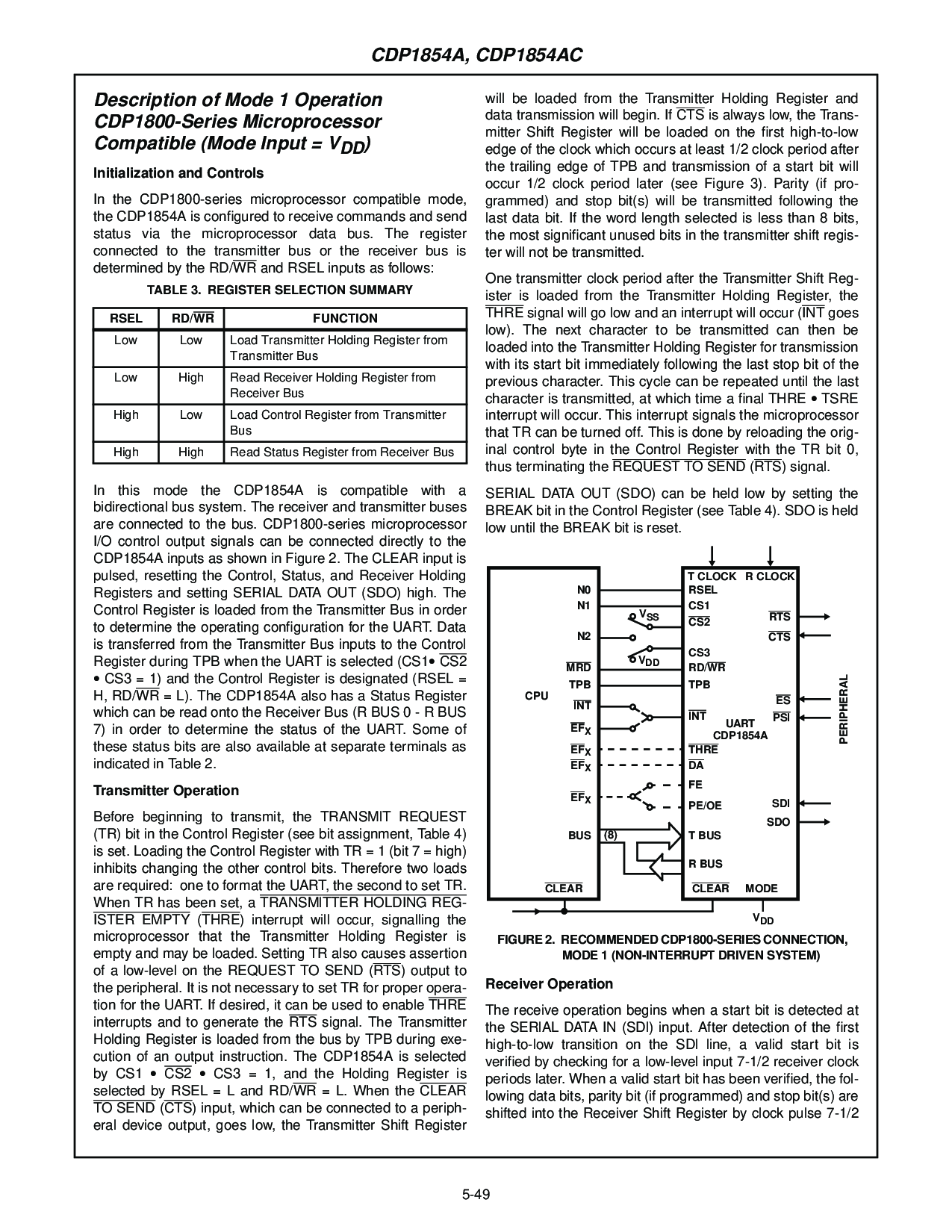

表格 3. 寄存器 选择 summary

RSEL rd/wr 函数

低 低 加载 传输者 支持 寄存器 从

传输者 总线

低 高 读 接受者 支持 寄存器 从

接受者 总线

高 低 加载 控制 寄存器 从 传输者

总线

高 高 读 状态 寄存器 从 接受者 总线

图示 2. 推荐 cdp1800-序列 连接,

模式 1 (非-中断 驱动 系统)

N0

N1

N2

MRD

TPB

INT

EF

X

EF

X

EF

X

EF

X

总线

CLEAR

(8)

CPU

RSEL

CS1

CS2

rd/

WR

TPB

INT

THRE

DA

t 总线

CS3

t 时钟 r 时钟

RTS

CTS

ES

PSI

SDO

SDI

模式

CLEAR

V

DD

FE

pe/oe

r 总线

附带的

V

SS

V

DD

UART

CDP1854A

cdp1854a, cdp1854ac