30 电路 运作

(持续)

这 CGS410 准许 这 用户 至 选择 这 quantity 的 承担

打气 电流 和 它的 direction Specifying 这 方向 的

承担 流动 是 有用的 在 situations 在哪里 一个 外部 过滤

andor VCO 是 incorporated 看 这 产品 部分

为 一个 example 在 situations 在哪里 外部 网络 lack

这 承担 sensitivity 这 数量 的 承担 能 是 在-

creased 在 这 user’s discretion

34 可编程序的 分隔物 运作

这 CGS410 有 四 内部的 dividers (r N P 和 l)

这个 是 编写程序 serially 通过 这 内部的 控制 regis-

ter

这 R (涉及) 分隔物 提供 一个 涉及 频率

从 也 一个 结晶 或者 一个 externally 发生 时钟

source 这 divisor 范围 是 相接的 和 varies 从 1 至

1023 这 modulus 选择 是 这 直接 二进制的 相等的

承载 在 这 串行 控制 寄存器 在 位 locations 24–33

这 内部的 N 分隔物 提供 一个 意思 的 locking 这 VCO

和 一个 常量 tuning 决议 那 是 独立 的 这

pixel system 它的 相接的 modulus 范围 是 2 至 16383

这 P (postscaling) 分隔物 提供 一个 意思 的 generating

一个 输出 在 一个 宽 频率 范围 从 一个 VCO 这个

有 一个 flxed 频率 range 这 modulus selections 的 这

P 分隔物 范围 从 1–16 inclusive 这 modulus 的 这个

分隔物 是 编写程序 和 串行 控制 寄存器 位

16–19 这 PCLK 输出 是 正方形的 当 这 P modulus

是 1 2 4 6 8 10 12 14 或者 16 如果 这 P modulus 是 3 5 7 9

11 13 或者 15 这 PCLK 输出 是 低 一个 较少 计数 比

它 是 high 为 example dividing 用 modulus 5 将 结果 在

三 counts 高 和 二 counts low

这 L (加载) 分隔物 提供 一个 意思 的 generating 一个 加载

时钟 用 dividing 这 PCLK 用 一个 modulus ranging 从 1–16

inclusive 这 modulus 的 这 加载 分隔物 是 编写程序

和 串行 控制 寄存器 位 20–23 这 L 时钟 输出 是

获得 从 这 输出 的 这 内部的 MUX 所以 whichever

输出 是 选择 用 这 mux 将 是 分隔 用 L 这 L

时钟 能 是 asynchronously disabledenabled 用 一个 串行

bit 这 LCLK 输出 是 正方形的 当 这 L modulus 是 1

2 4 6 8 10 12 14 或者 16 如果 这 L modulus 是 3 5 7 9 11

13 或者 15 这 LCLK 是 高 一个 较少 计数 比 它 是 low 为

example dividing 用 modulus 5 将 结果 在 三 counts

低 和 二 counts high

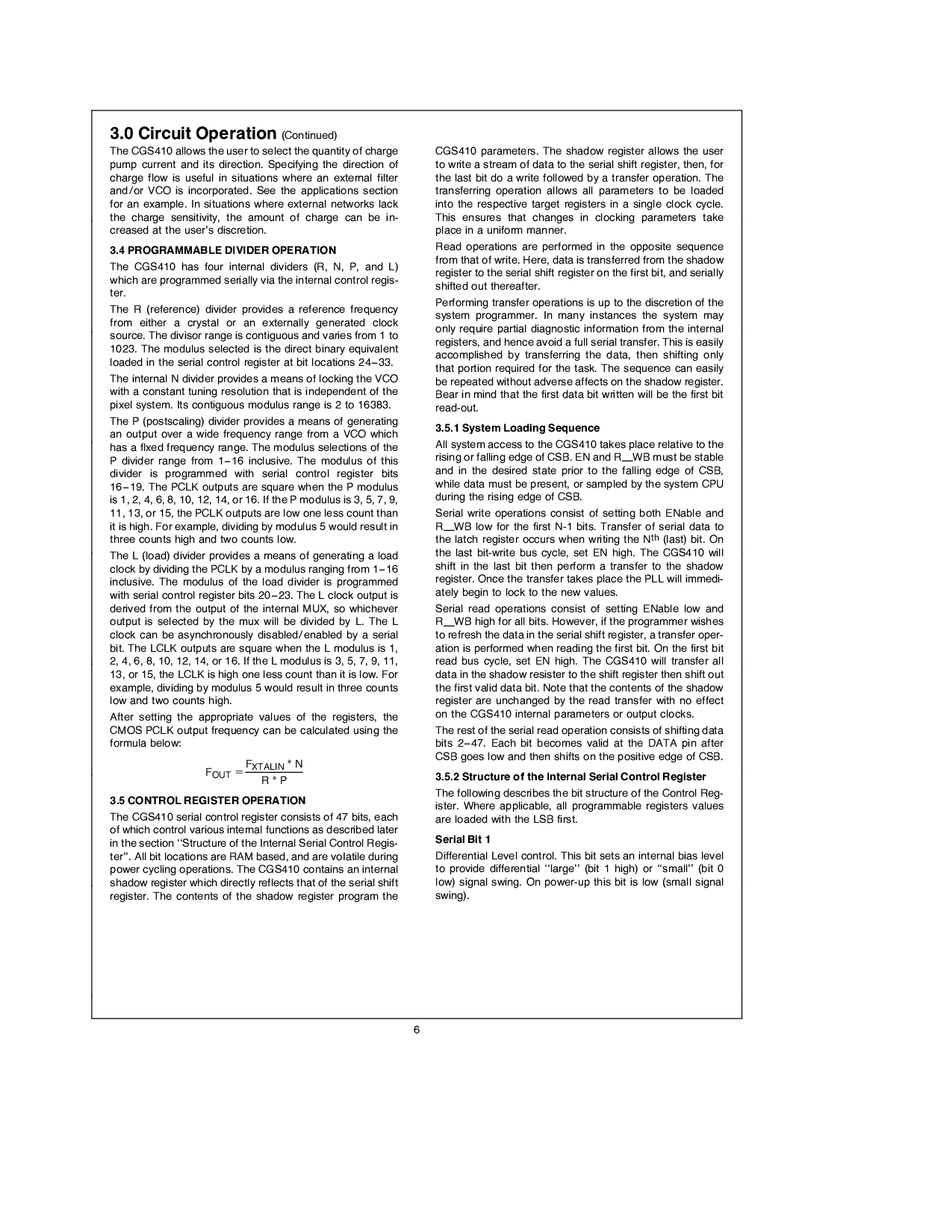

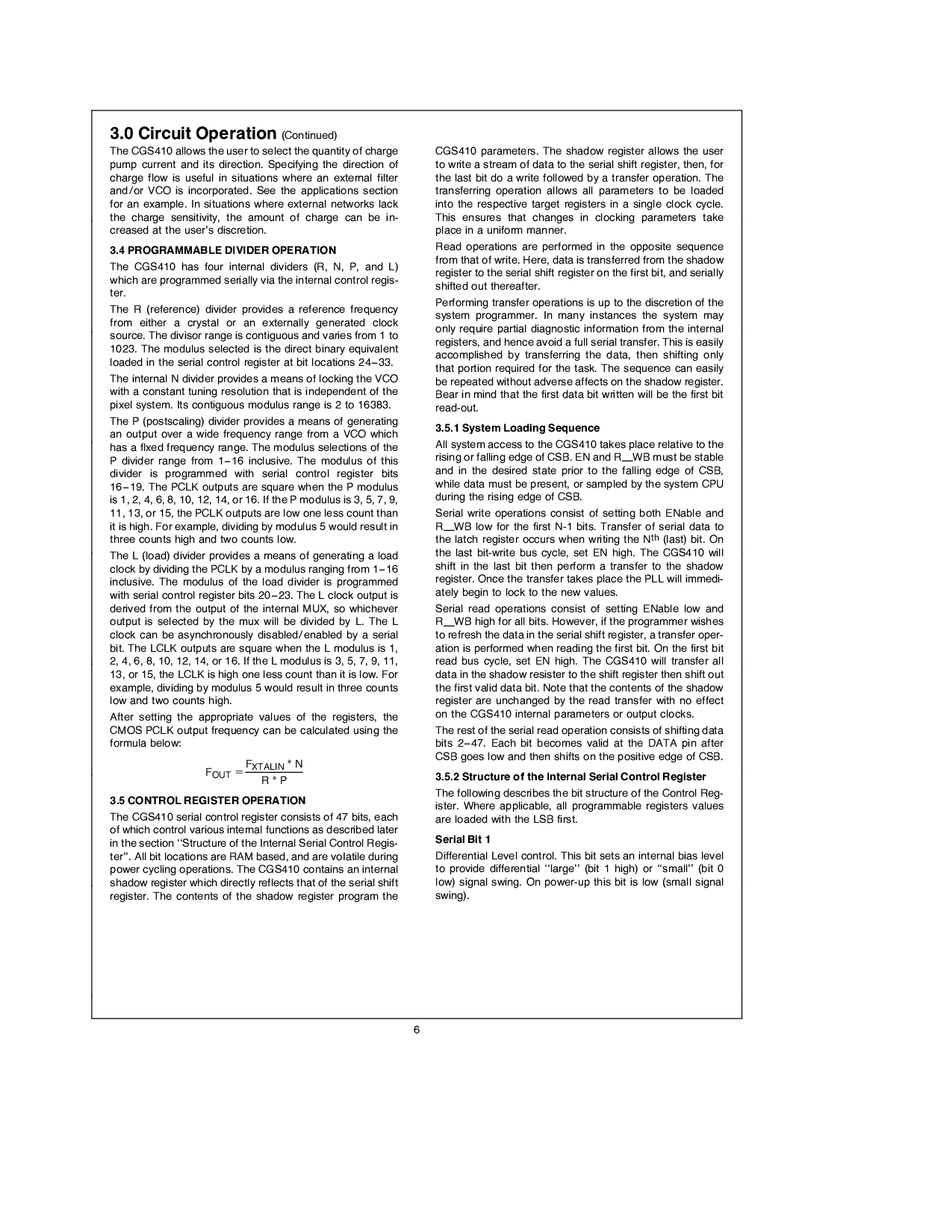

之后 设置 这 适合的 值 的 这 registers 这

CMOS PCLK 输出 频率 能 是 计算 使用 这

formula below

F

输出

e

F

XTALIN

N

R

P

35 控制 寄存器 运作

这 CGS410 串行 控制 寄存器 组成 的 47 bits 各自

的 这个 控制 各种各样的 内部的 功能 作 描述 后来的

在 这 部分 ‘‘Structure 的 这 内部的 串行 控制 regis-

ter’’ 所有 位 locations 是 内存 based 和 是 voIatile 在

电源 cycling operations 这 CGS410 包含 一个 内部的

shadow 寄存器 这个 直接地 reflects 那 的 这 串行 变换

register 这 内容 的 这 shadow 寄存器 程序 这

CGS410 parameters 这 shadow 寄存器 准许 这 用户

至 写 一个 stream 的 数据 至 这 串行 变换 register then 为

这 last 位 做 一个 写 followed 用 一个 转移 operation 这

transferring 运作 准许 所有 参数 至 是 承载

在 这 各自的 目标 寄存器 在 一个 单独的 时钟 cycle

这个 确保 那 改变 在 clocking 参数 引领

放置 在 一个 uniform manner

读 行动 是 执行 在 这 opposite sequence

从 那 的 write Here 数据 是 transferred 从 这 shadow

寄存器 至 这 串行 变换 寄存器 在 这 第一 bit 和 serially

shifted 输出 thereafter

Performing 转移 行动 是 向上 至 这 discretion 的 这

系统 programmer 在 许多 instances 这 系统 将

仅有的 需要 partial diagnostic 信息 从 这 内部的

registers 和 hence 避免 一个 全部 串行 transfer 这个 是 容易地

accomplished 用 transferring 这 data 然后 shifting 仅有的

那 portion 必需的 为 这 task 这 sequence 能 容易地

是 重复的 没有 adverse affects 在 这 shadow register

Bear 在 mind 那 这 第一 数据 位 写 将 是 这 第一 位

读-out

351 系统 加载 Sequence

所有 系统 进入 至 这 CGS410 takes 放置 相关的 至 这

rising 或者 下落 边缘 的 CSB EN 和 R

WB 必须 是 稳固的

和 在 这 desired 状态 较早的 至 这 下落 边缘 的 CSB

当 数据 必须 是 present 或者 抽样 用 这 系统 CPU

在 这 rising 边缘 的 CSB

串行 写 行动 组成 的 设置 两个都 使能 和

R

WB 低 为 这 第一 n-1 bits 转移 的 串行 数据 至

这 获得 寄存器 occurs 当 writing 这 N

th

(last) bit 在

这 last 位-写 总线 cycle 设置 EN high 这 CGS410 将

变换 在 这 last 位 然后 执行 一个 转移 至 这 shadow

register Once 这 转移 takes 放置 这 PLL 将 immedi-

ately begin 至 锁 至 这 新 values

串行 读 行动 组成 的 设置 使能 低 和

R

WB 高 为 所有 bits However 如果 这 programmer wishes

至 refresh 这 数据 在 这 串行 变换 register 一个 转移 oper-

ation 是 执行 当 读 这 第一 bit 在 这 第一 位

读 总线 cycle 设置 EN high 这 CGS410 将 转移 所有

数据 在 这 shadow resister 至 这 变换 寄存器 然后 变换 输出

这 第一 有效的 数据 bit 便条 那 这 内容 的 这 shadow

寄存器 是 不变 用 这 读 转移 和 非 效应

在 这 CGS410 内部的 参数 或者 输出 clocks

这 rest 的 这 串行 读 运作 组成 的 shifting 数据

位 2–47 各自 位 变为 有效的 在 这 数据 管脚 之后

CSB 变得 低 和 然后 shifts 在 这 积极的 边缘 的 CSB

352 结构 的 这 内部的 串行 控制 寄存器

这 下列的 describes 这 位 结构 的 这 控制 reg-

ister 在哪里 applicable 所有 可编程序的 寄存器 值

是 承载 和 这 LSB first

串行 位 1

差别的 水平的 control 这个 位 sets 一个 内部的 偏差 水平的

至 提供 差别的 ‘‘large’’ (位 1 高) 或者 ‘‘small’’ (位 0

低) 信号 swing 在 电源-向上 这个 位 是 低 (小 信号

摆动)

6