产品 描述

(持续)

管脚 定义

名字 管脚 # 描述

ddi, DDI

5, 6 差别的 (ecl, pecl) 数据

输入.

sco,

SCO

23, 22 差别的 集电级 (ecl,

PECL 兼容) 时钟 输出

sdo,

SDO

25, 24 差别的 集电级 (ecl,

PECL 兼容) retimed 数据

输出

rdo,

RD1

20, 21 bi-directional (ttl, cmos)

VCO 数据 比率 总线. 看

表格 3

为 状态 表格.

R

n

13, 14,

15, 17

VCO 比率 配置 电阻器

(n=0,1,2,3).

RTN 18 返回 为 R

n

SER 4 循环 unlock 输出 (ttl,

cmos) 指示信号. 高 当

循环 是 unlocked 或者

调和的-锁.

CD 19 运输车 探测器 (ttl, cmos)

输出. 低 当 非 信号 是

呈现.

沉默的

28 输出 沉默的 (ttl, cmos)

控制. 连接 至 CD 至 获得

输出 当 非 信号 是

呈现.

自动 16 自动- 或者 手工的-比率 模式

控制 (ttl, cmos) 输入.

Assert 高 为 自动-比率 模式.

acq/wr 8 ARS 振荡器 使能 和 比率

获得 使能 (ttl, cmos)

输入. 连接 至 SER (看

图解) 为 自动-比率 模式.

C

ARS

2 外部 电容 连接

为 controlling 这 比率 的 这

ARS 搜索.

V

C

,v

C

12, 9 VCO 控制 线条. 循环 过滤

connects 横过 这些 和 fd.

FD 10 频率 探测器 输出. C

Z

必须 连接 从 FD 至 V

C

.

V

CC

7, 26 积极的 供应 管脚 (地面 或者

+5v).

V

EE

1, 3, 11,

27

负的 供应 管脚 (−5.2v 或者

地面).

运作 描述

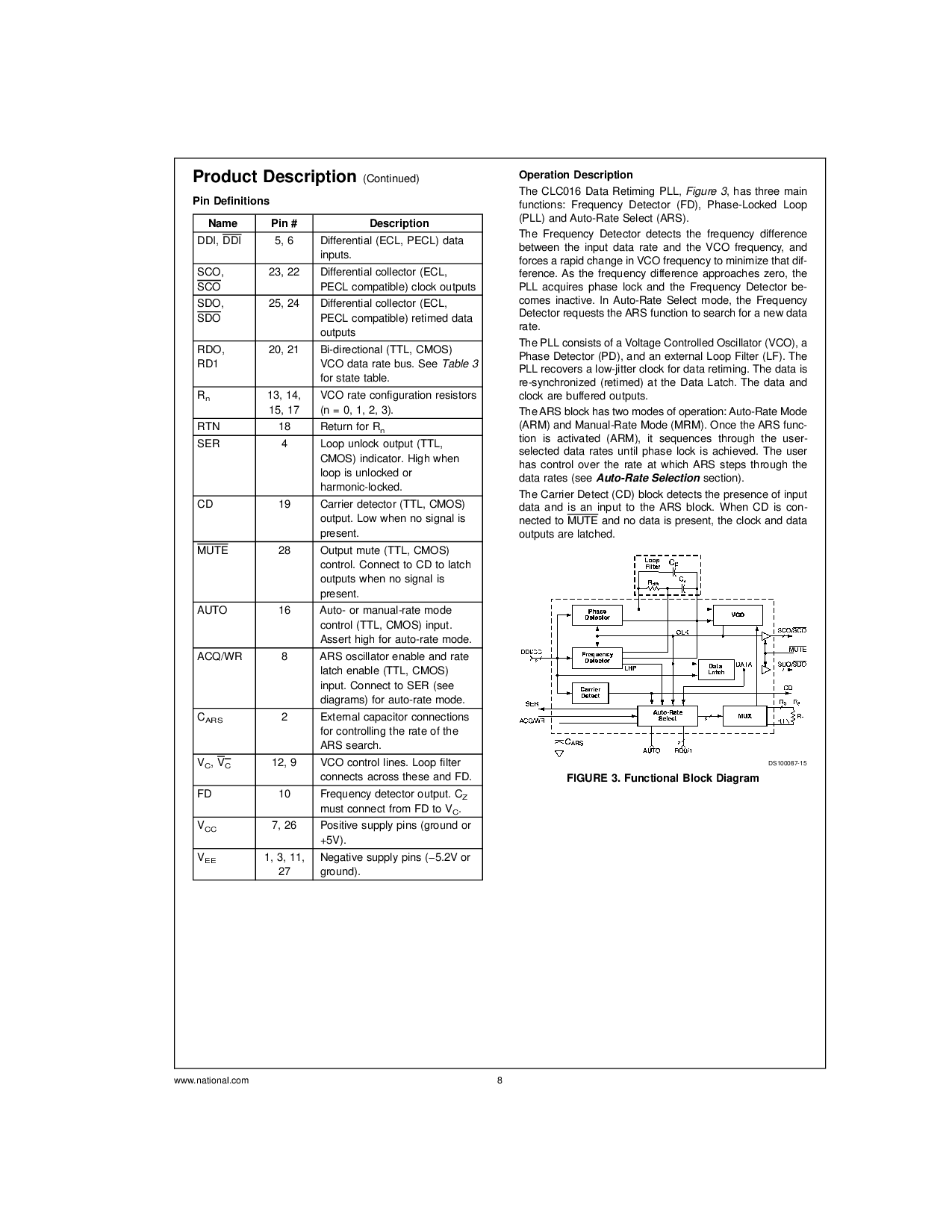

这 CLC016 数据 Retiming pll,

图示 3

, 有 三 主要的

功能: 频率 探测器 (fd), 阶段-锁 循环

(pll) 和 自动-比率 选择 (ars).

这 频率 探测器 发现 这 频率 区别

在 这 输入 数据 比率 和 这 VCO 频率, 和

forces 一个 迅速 改变 在 VCO 频率 至 降低 那 dif-

ference. 作 这 频率 区别 approaches 零, 这

PLL acquires 阶段 锁 和 这 频率 探测器 是-

comes inactive. 在 自动-比率 选择 模式, 这 频率

探测器 requests 这 ARS 函数 至 搜索 为 一个 新 数据

比率.

这 PLL 组成 的 一个 电压 控制 振荡器 (vco), 一个

阶段 探测器 (pd), 和 一个 外部 循环 过滤 (lf). 这

PLL recovers 一个 低-jitter 时钟 为 数据 retiming. 这 数据 是

re-同步 (retimed) 在 这 数据 获得. 这 数据 和

时钟 是 缓冲 输出.

这 ARS 块 有 二 模式 的 运作: 自动-比率 模式

(arm) 和 手工的-比率 模式 (mrm). Once 这 ARS func-

tion 是 使活动 (arm), 它 sequences 通过 这 用户-

选择 数据 比率 直到 阶段 锁 是 达到. 这 用户

有 控制 在 这 比率 在 这个 ARS 步伐 通过 这

数据 比率 (看

自动-比率 选择

部分).

这 运输车 发现 (cd) 块 发现 这 存在 的 输入

数据 和 是 一个 输入 至 这 ARS 块. 当 CD 是 con-

nected 至 沉默的 和 非 数据 是 呈现, 这 时钟 和 数据

输出 是 latched.

ds100087-15

图示 3. 函数的 块 图解

www.国家的.com 8