5 www.国家的.com

CLC5903

便条 1:

数据手册 最小值/最大值 规格 限制 是 有保证的 用 设计, 测试, 或者 statistical 分析.

便条 2:

所有 输出 管脚 提供 16ma 输出 驱动 除了 tdo (管脚 116) 这个 提供 4ma 输出 驱动.

便条 3:

t

SFSV

谈及 至 这 rising 边缘 的

SCK

当 sck_pol=0 和 这 下落 边缘 当 sck_pol=1.

便条 4:

t

OV

谈及 至 这 rising 边缘 的

SCK

当 sck_pol=0 和 这 下落 边缘 当 sck_pol=1.

便条 5:

t

RDYV

谈及 至 这 rising 边缘 的

RDY

当 rdy_pol=0 和 这 下落 边缘 当 rdy_pol=1.

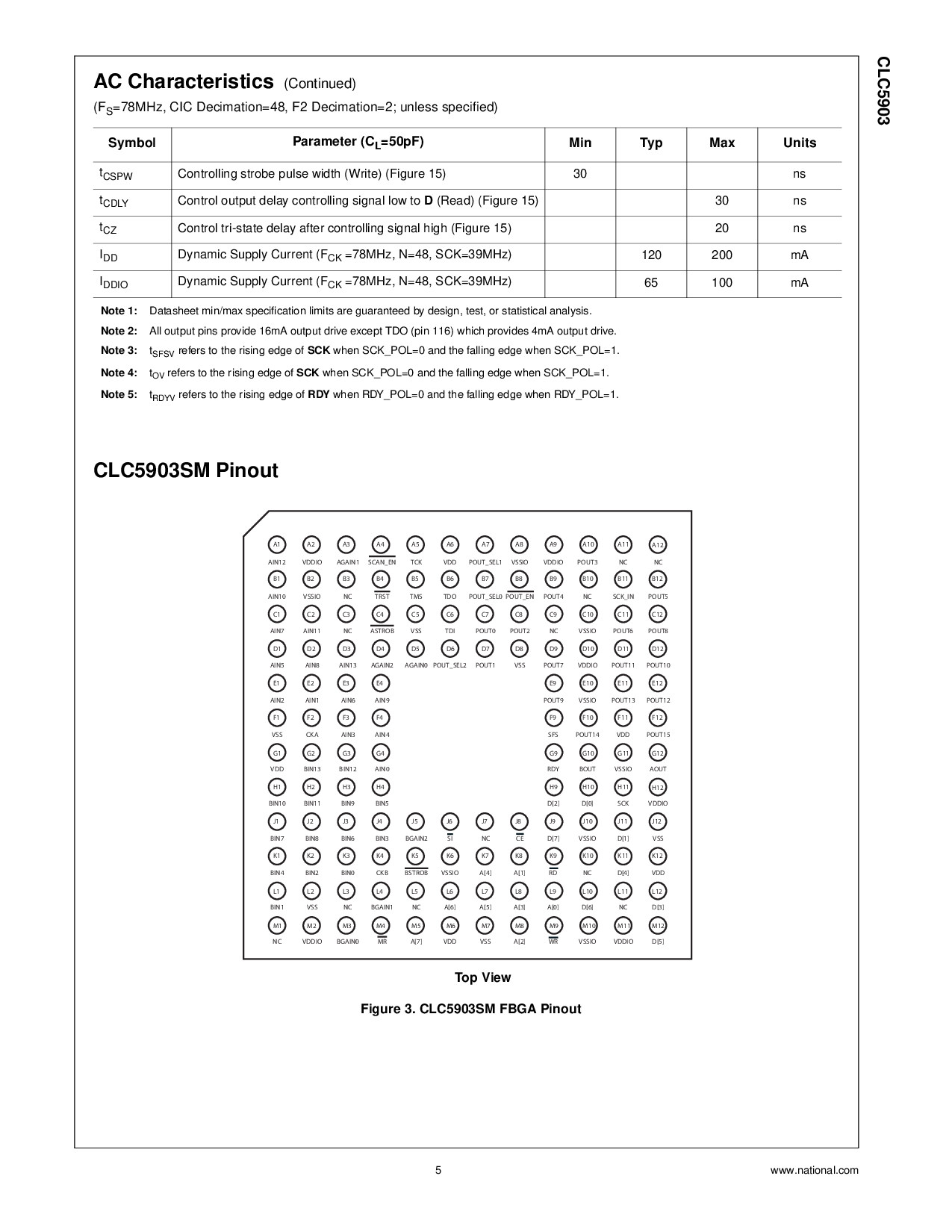

clc5903sm 引脚

t

CSPW

controlling strobe 脉冲波 宽度 (写) (图示 15) 30 ns

t

CDLY

控制 输出 延迟 controlling 信号 低 至

D

(读) (图示 15) 30 ns

t

CZ

控制 触发-状态 延迟 之后 controlling 信号 高 (图示 15) 20 ns

I

DD

动态 供应 电流 (f

CK

=78mhz, n=48, sck=39mhz)

120 200 毫安

I

DDIO

动态 供应 电流 (f

CK

=78mhz, n=48, sck=39mhz)

65 100 毫安

交流 特性

(持续)

(f

S

=78mhz, cic decimation=48, f2 decimation=2; 除非 指定)

标识

参数 (c

L

=50pf)

最小值 典型值 最大值 单位

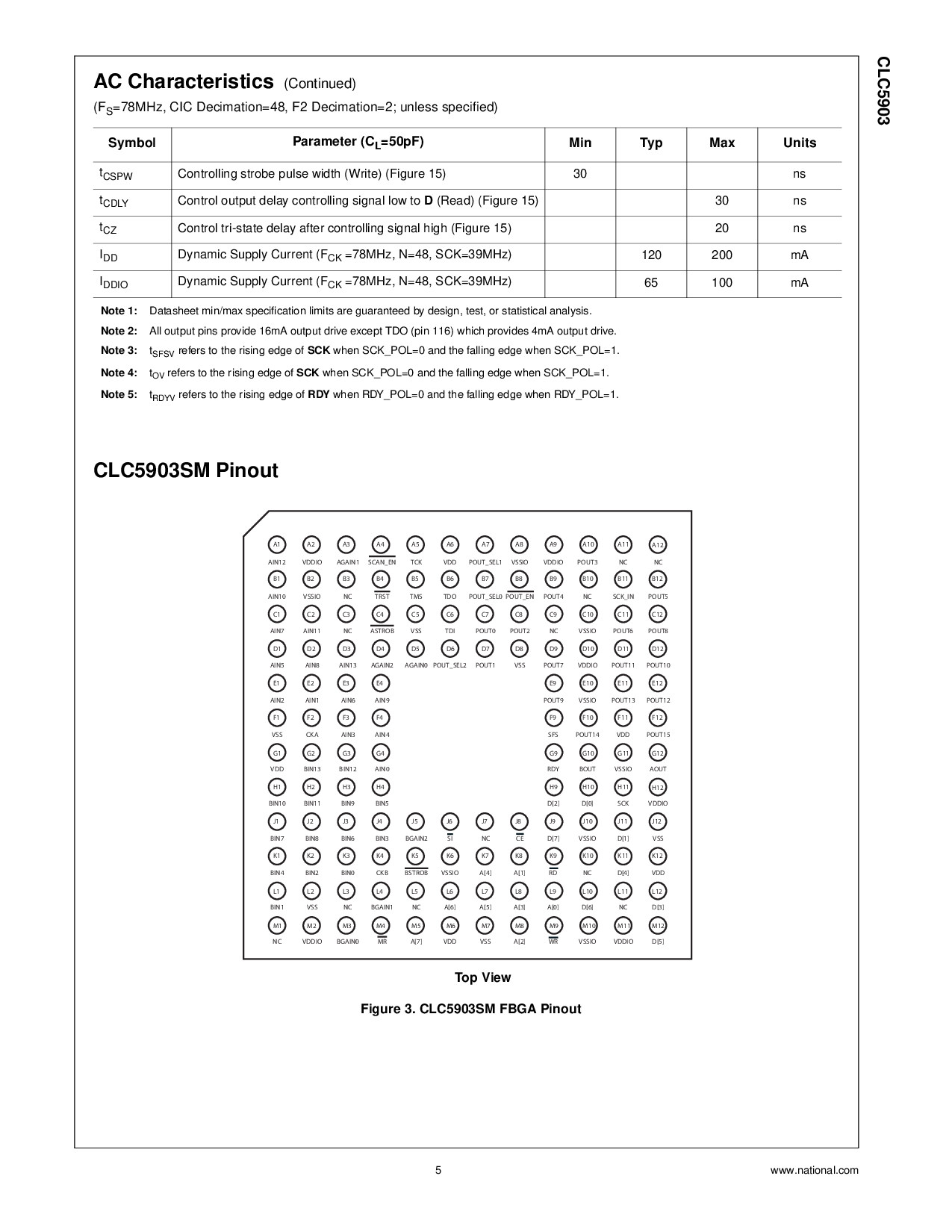

图示 3. clc5903sm fbga 引脚

A12

A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11

B12

B1 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11

C12

C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11

D12

D1 D2 D3 D4 D5 D6 D7 D8 D9 D10 D11

E12

E1 E2 E3 E4 E9 E10 E11

F12

F1 F2 F3 F4 F9 F10 F11

G12

G1 G2 G3 G4 G9 G10 G11

H12

H1 H2 H3 H4 H9 H10 H11

J12

J1 J2 J3 J4 J5 J6 J7 J8 J9 J10 J11

K12

K1 K2 K3 K4 K5 K6 K7 K8 K9 K10 K11

L12

L1 L2 L3 L4 L5 L6 L7 L8 L9 L10 L11

M12

M1 M2 M3 M4 M5 M6 M7 M8 M9 M10 M11

AIN12

AIN10

AIN7

AIN5

AIN2

VSS

VDD

BIN10

BIN7

BIN4

BIN1

NC

VDDIO

VSSIO

AIN11

AIN8

AIN1

CKA

BIN13

BIN11

BIN8

BIN2

VSS

VDDIO

AGAIN1

NC

NC

AIN13

AIN6

AIN3

BIN12

BIN9

BIN6

BIN0

NC

BGAIN0

scan_en

TRST

ASTROB

AGAIN2

AIN9

AIN4

AIN0

BIN5

BIN3

CKB

BGAIN1

MR

TCK

TMS

VSS

AGAIN0

BGAIN2

BSTROB

NC

A[7]

VDD

TDO

TDI

pout_sel2

SI

VSSIO

A[6]

VDD

pout_sel1

pout_sel0

POUT0

POUT1

NC

A[4]

A[5]

VSS

VSSIO

pout_en

POUT2

VSS

CE

A[1]

A[3]

A[2]

VDDIO

POUT4

NC

POUT7

POUT9

SFS

RDY

D[2]

D[7]

RD

A[0]

WR

POUT3

NC

VSSIO

VDDIO

VSSIO

POUT14

BOUT

D[0]

VSSIO

NC

D[6]

VSSIO

NC

sck_在

POUT6

POUT11

POUT13

VDD

VSSIO

SCK

D[1]

D[4]

NC

VDDIO

NC

POUT5

POUT8

POUT10

POUT12

POUT15

AOUT

VDDIO

VSS

VDD

D[3]

D[5]

至pView