AD9865

rev. 一个 | 页 4 的 48

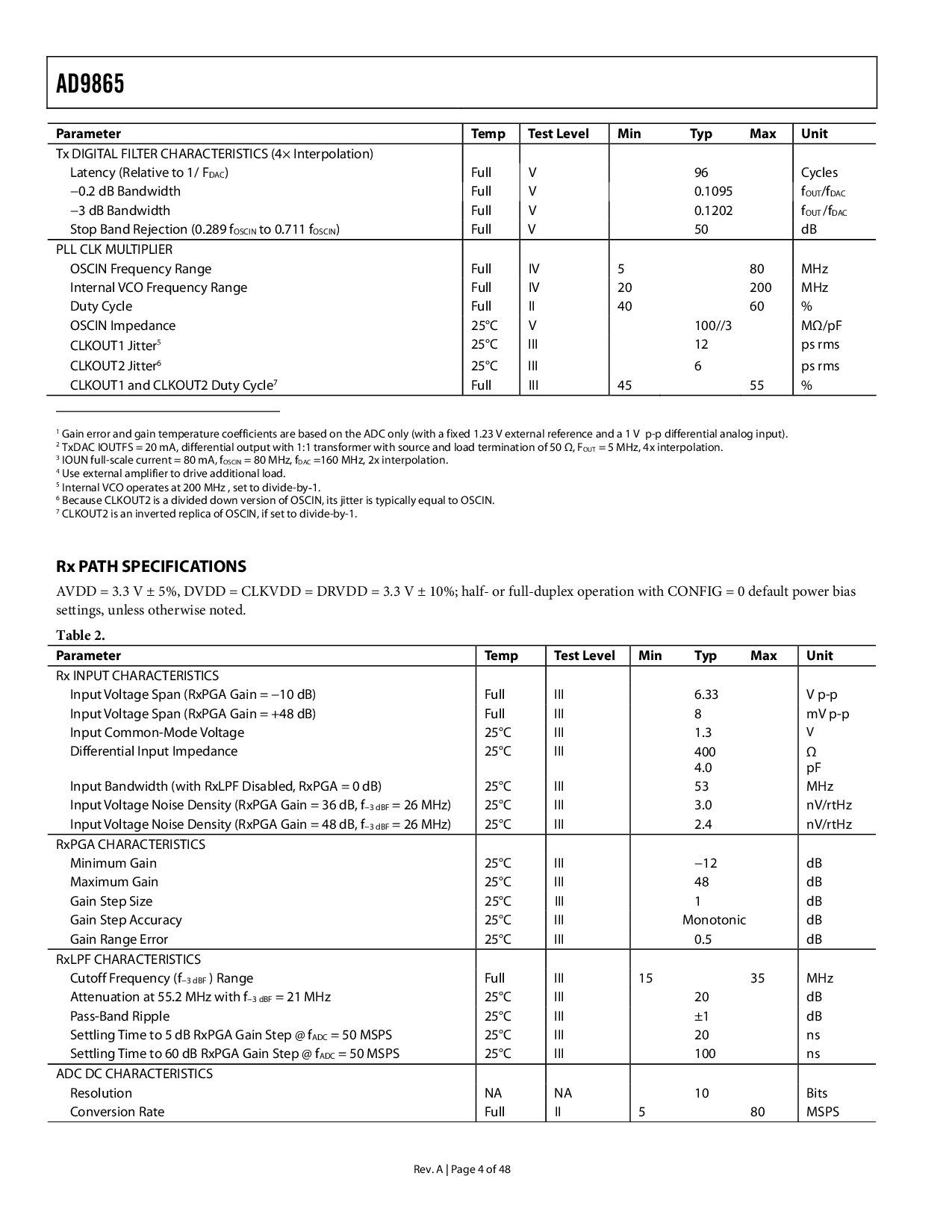

参数 温度 测试 水平的 最小值 典型值 最大值 单位

tx 数字的 过滤 特性 (4× interpolation)

latency (相关的 至 1/ f

DAC

) 全部 v 96 循环

−0.2 db 带宽 全部 V 0.1095 f

输出

/f

DAC

−3 db 带宽 全部 V 0.1202 f

输出

/f

DAC

停止 带宽 拒绝 (0.289 f

OSCIN

至 0.711 f

OSCIN

) 全部 v 50 db

pll clk 乘法器

oscin 频率 范围 全部 IV 5 80 MHz

内部的 vco 频率 范围 全部 IV 20 200 MHz

职责 循环 全部 II 40 60 %

oscin 阻抗 25°C V 100//3 ΜΩ/pf

clkout1 jitter

5

25°c iii 12 ps rms

clkout2 jitter

6

25°c iii 6 ps rms

clkout1 和 clkout2 职责 循环

7

全部 iii 45 55 %

1

增益 错误 和 增益 温度 coefficients 是 为基础 在 这 模数转换器 仅有的 (和 一个 fixed 1.23 v 外部 涉及 和 一个 1 v p-p差别的 相似物 输入).

2

txdac ioutfs = 20 毫安, 差别的输出 和 1:1 变压器 和 源 和 加载 末端 的 50 Ω, f

输出

= 5 mhz, 4x interpolation.

3

ioun 全部-规模 电流 = 80 毫安, f

OSCIN

= 80 mhz, f

DAC

=160 mhz, 2x interpolation.

4

使用 外部 放大器 至 驱动 额外的 加载.

5

内部的 vco 运作 在200 mhz , 设置 至 分隔-用

-

1.

6

因为 clkout2 是 一个 分隔 向下 版本 的 oscin, 它的 jitter 是 典型地 equal 至 oscin.

7

clkout2 是 一个 inverted replica 的 oscin, 如果 设置 至 分隔-用-1.

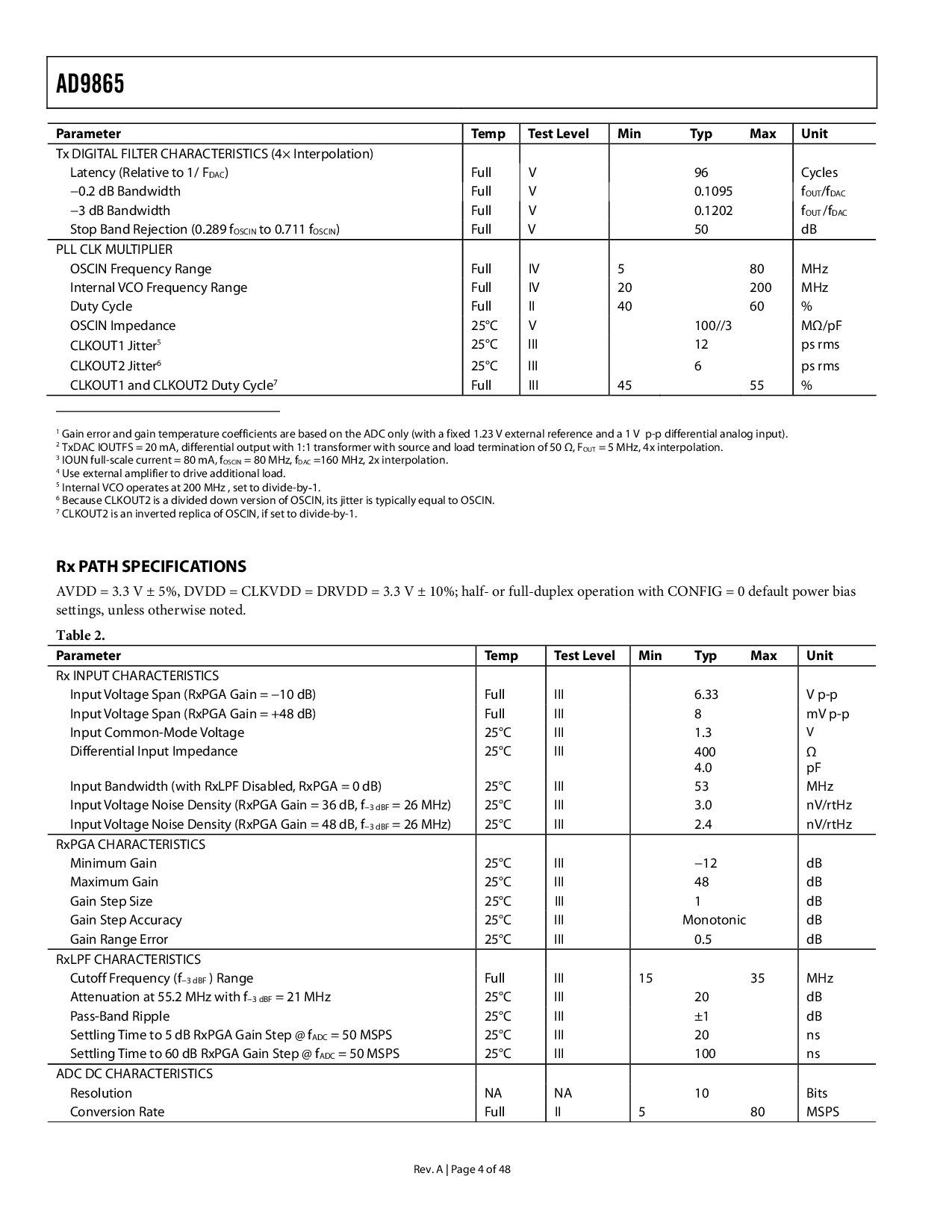

rx path 规格

avdd = 3.3 v ± 5%, dvdd = clkvdd = drvdd = 3.3 v ± 10%; half- 或者 full-duplex 运作 和 config = 0 default 电源 偏差

settings, 除非 否则 指出.

表格 2.

参数 温度 测试 水平的 最小值 典型值 最大值 单位

rx 输入 特性

输入 电压 span (rxpga 增益 = −10 db) 全部 III 6.33 v p-p

输入 电压 span (rxpga 增益 = +48 db) 全部 III 8 mv p-p

输入 一般模式 电压 25°C III 1.3

V

差别的 输入 阻抗 25°C III

400

4.0

Ω

pF

输入 带宽 (和 rxlpf 无能,rxpga = 0 db) 25°C III 53 MHz

输入 电压 噪音 密度 (rxpga 增益 = 36 db, f

−3 dbf

= 26 mhz)

25°C III 3.0 nv/rthz

输入 电压 噪音 密度 (rxpga 增益 = 48 db, f

−3 dbf

= 26 mhz)

25°C III 2.4 nv/rthz

rxpga 特性

最小 增益 25°C III −12 dB

最大 增益 25°C III 48 dB

增益 步伐 大小 25°C III 1 dB

增益 步伐 精度 25°C III Monotonic dB

增益 范围 错误 25°C III 0.5 dB

rxlpf 特性

截止 频率 (f

−3 dbf

) 范围

全部 III 15 35 MHz

attenuation 在 55.2 mhz 和 f

−3 dbf

= 21 mhz

25°C III 20 dB

通过-带宽 波纹 25°C III ±1 dB

安排好 时间 至 5 db rxpga 增益 步伐 @ f

模数转换器

= 50 msps 25°C III 20 ns

安排好 时间 至 60 db rxpga 增益 步伐 @ f

模数转换器

= 50 msps 25°C III 100 ns

模数转换器 直流 特性

决议 NA NA 10 位

转换 比率 全部 II 5 80 MSPS