CYP15G0101DXB

CYV15G0101DXB

文档 #: 38-02031 rev. *i 页 2 的 39

这 cyv15g0101dxb satisfies 这 smpte 259m 和

smpte 292m 遵从 作 每 这 eg34-1999 pathological

测试 (所需的)东西.

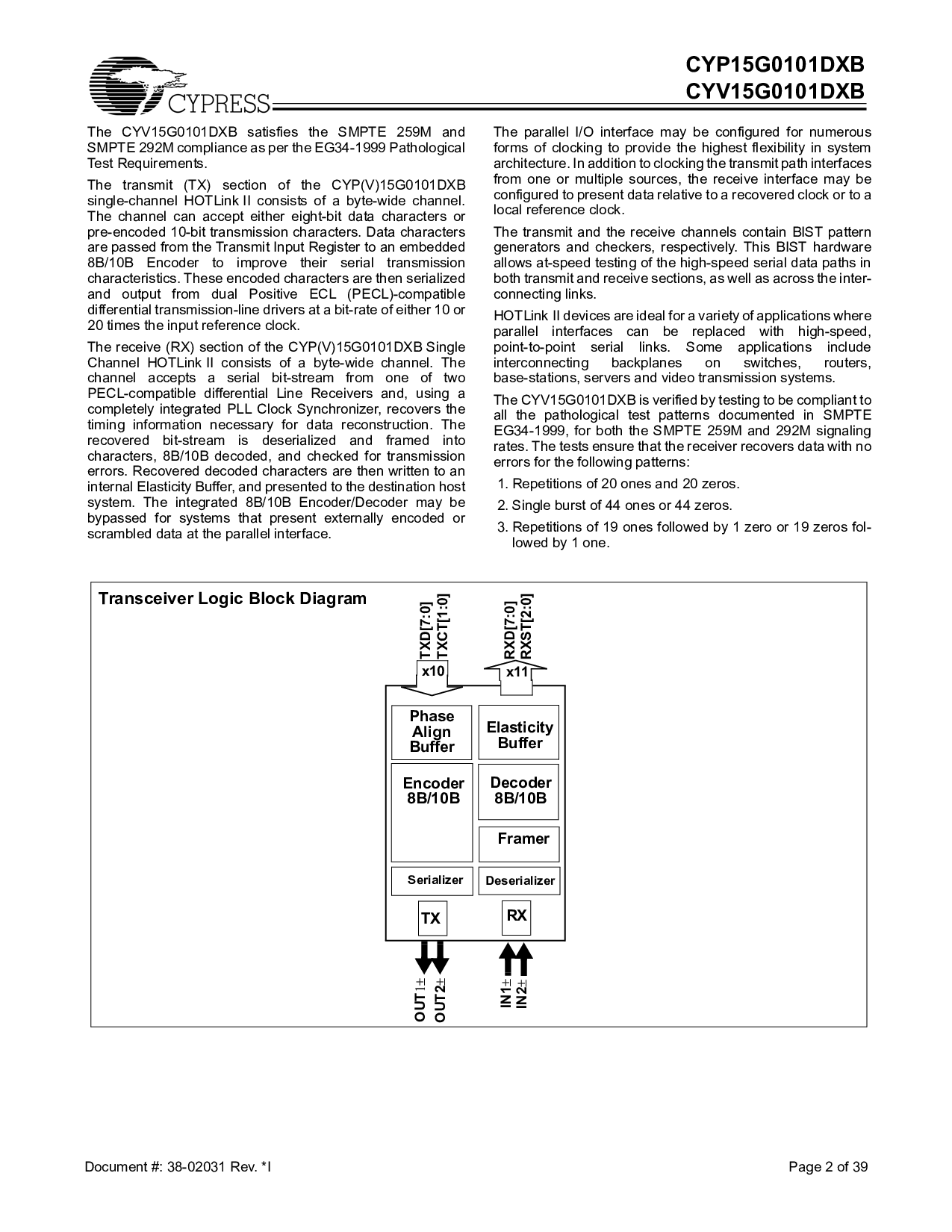

这 transmit (tx) 部分 的 这 cyp(v)15g0101dxb

单独的-频道 hotlink ii 组成 的 一个 字节-宽 频道.

这 频道 能 接受 也 第八-位 数据 characters 或者

前-encoded 10-位 传递 characters. 数据 characters

是 passed 从 这 transmit 输入 寄存器 至 一个 embedded

8b/10b encoder 至 改进 它们的 串行 传递

特性. 这些 encoded characters 是 然后 serialized

和 输出 从 双 积极的 ecl (pecl)-兼容

差别的 传递-线条 驱动器 在 一个 位-比率 的 也 10 或者

20 时间 这 输入 涉及 时钟.

这 receive (rx) 部分 的 这 cyp(v)15g0101dxb 单独的

频道 hotlink ii 组成 的 一个 字节-宽 频道. 这

频道 accepts 一个 串行 位-stream 从 一个 的 二

pecl-兼容 差别的 线条 接受者 和, 使用 一个

完全地 整体的 pll 时钟 synchronizer, recovers 这

定时 信息 需要 为 数据 reconstruction. 这

recovered 位-stream 是 deserialized 和 framed 在

characters, 8b/10b 解码, 和 审查 为 传递

errors. recovered 解码 characters 是 然后 写 至 一个

内部的 elasticity 缓存区, 和 提交 至 这 destination host

系统. 这 整体的 8b/10b encoder/解码器 将 是

绕过 为 系统 那 呈现 externally encoded 或者

scrambled 数据 在 这 并行的 接口.

这 并行的 i/o 接口 将 是 配置 为 numerous

形式 的 clocking 至 提供 这 最高的 flexibility 在 系统

architecture. 在 增加 至 clocking 这 transmit path 接口

从 一个 或者 多样的 来源, 这 receive 接口 将 是

配置 至 呈现 数据 相关的 至 一个 recovered 时钟 或者 至 一个

local 涉及 时钟.

这 transmit 和 这 receive 途径 包含 bist 模式

发生器 和 checkers, 各自. 这个 bist 硬件

准许 在-速 测试 的 这 高-速 串行 数据 paths 在

两个都 transmit 和 receive sections, 作 好 作 横过 这 inter-

连接 links.

HOTLink ii 设备 是 完美的 为 一个 多样性 的 产品 在哪里

并行的 接口 能 是 replaced 和 高-速,

要点-至-要点 串行 links. 一些 产品 包含

interconnecting backplanes 在 switches, routers,

根基-stations, servers 和 video 传递 系统.

这 cyv15g0101dxb 是 核实 用 测试 至 是 一致的 至

所有 这 pathological 测试 patterns documented 在 smpte

eg34-1999, 为 两个都 这 smpte 259m 和 292m signaling

比率. 这 tests 确保 那 这 接受者 recovers 数据 和 非

errors 为 这 下列的 patterns:

1. repetitions 的 20 ones 和 20 zeros.

2. 单独的 burst 的 44 ones 或者 44 zeros.

3. repetitions 的 19 ones followed 用 1 零 或者 19 zeros fol-

lowed 用 1 一个.

x10

Serializer

阶段

Encoder

8b/10b

解码器

8b/10b

x11

Framer

Deserializer

TX

RX

txd[7:0]

rxd[7:0]

输出

OUT2

IN1

IN2

排整齐

缓存区

Elasticity

缓存区

txct[1:0]

rxst[2:0]

transceiver 逻辑 块 图解