rev. 0

ad5303/ad5313/ad5323

–

12

–

串行 接口

这 ad5303/ad5313/ad5323 是 控制 在 一个 多功能的,

3-线 串行 接口, 这个 运作 在 时钟 比率 向上 至

30 mhz 和 是 兼容 和 spi, qspi, microwire 和

dsp 接口 standards.

输入 变换 寄存器

这 输入 变换 寄存器 是 16 位 宽. 数据 是 承载 在 这

设备 作 一个 16-位 文字 下面 这 控制 的 一个 串行 时钟 输入,

sclk. 这 定时 图解 为 这个 运作 是 显示 在 图-

ure 2. 这 16-位 文字 组成 的 四 控制 位 followed 用

8, 10 或者 12 位 的 dac 数据, 取决于 在 这 设备 类型.

这 第一 位 承载 是 这 msb (位 15), 这个 确定

whether 这 数据 是 为 dac 一个 或者 dac b. 位 14 确定 这

输出 范围 (0–v

REF

或者 0–2 v

REF

). 位 13 和 12 控制 这

运行 模式 的 这 dac.

表格 i. 控制 位

电源-在

位 名字 函数 Default

15

一个

/b 0: 数据 写 至 dac 一个 n/一个

1: 数据 写 至 dac b

14 增益 0: 输出 范围 的 0–v

REF

0

1: 输出 范围 的 0-2 v

REF

13 PD1 模式 位 0

12 PD0 模式 位 0

这 remaining 位 是 dac 数据 位, 开始 和 这 msb

和 ending 和 这 lsb. 这 ad5323 使用 所有 12 位 的 dac

数据, 这 ad5313 使用 10 位 和 ignores 这 二 lsbs. 这

ad5303 使用 第八 位 和 ignores 这 last 四 位. 这 数据

format 是 笔直地 二进制的, 和 所有 zeroes 相应的 至 0 v 输出-

放, 和所有 ones 相应的 至 全部-规模 output (v

REF

– 1 lsb).

这

同步

输入 是 一个 水平的-triggered 输入 那 acts 作 一个 框架

同步 信号 和 碎片 使能. 数据 能 仅有的 是 trans-

ferred 在 这 设备 当

同步

是 低. 至 开始 这 串行

数据 转移,

同步

应当 是 带去 低 observing 这 迷你-

mum

同步

至 sclk 起作用的 边缘 建制 时间, t

4

. 之后

同步

变得 低, 串行 数据 将 是 shifted 在 这 设备的 输入 变换

寄存器 在 这 下落 edges 的 sclk 为 16 时钟 脉冲. 任何

数据 和 时钟 脉冲 之后 这 16th 将 是 ignored, 和 非

更远 串行 数据 转移 将 出现 直到

同步

是 带去 高

和 低 又一次.

同步

将 是 带去 高 之后 这 下落 边缘 的 这 16th

sclk 脉冲波, observing 这 最小 sclk 下落 边缘 至

同步

rising 边缘 时间, t

7

.

之后 这 终止 的 串行 数据 转移, 数据 将 automatically 是

transferred 从 这 输入 变换 寄存器 至 这 输入 寄存器 的

这 选择 dac. 如果

同步

是 带去 高 在之前 这 16th 下落

边缘 的 sclk, 这 数据 转移 将 是 aborted 和 这 输入

寄存器 将 不 是 updated.

当 数据 有 被 transferred 在 两个都 输入 寄存器, 这

dac 寄存器 的 两个都 dacs 将 是 同时发生地 updated,

用 带去

LDAC

低.

CLR

是 一个 起作用的-低, 异步的 clear

那 clears 这 输入 和 dac 寄存器 的 两个都 dacs 至 所有 zeroes.

低 电源 串行 接口

至 减少 这 电源 消耗量 的 这 设备 甚至 更远,

这 接口 仅有的 powers 向上 全部地 当 这 设备 是 正在 writ-

ten 至. 作 soon 作 这 16-位 控制 文字 有 被 写 至

这 部分, 这 sclk 和 din 输入 缓存区 是 powered-向下.

它们 仅有的 电源-向上 又一次 下列的 一个 下落 边缘 的

同步

.

翻倍-缓冲 接口

这 ad5303/ad5313/ad5323 dacs 所有 有 翻倍-缓冲

接口 consisting 的 二 banks 的 registers—input 寄存器

和 dac 寄存器. 这 输入 寄存器 是 连接 直接地 至

这 输入 变换 寄存器 和 这 数字的 代号 是 transferred 至 这

相关的 输入 寄存器 在 completion 的 一个 有效的 写 sequence.

这 dac 寄存器 包含 这 数字的 代号 使用 用 这 电阻

string.

进入 至 这 dac 寄存器 是 控制 用 这

LDAC

函数.

当

LDAC

是 高, 这 dac 寄存器 是 latched 和 这 输入

寄存器 将 改变 状态 没有 影响 这 内容 的 这

dac 寄存器. 不管怎样, 当

LDAC

是 brought 低, 这 dac

寄存器 变为 transparent 和 这 内容 的 这 输入 regis-

ter 是 transferred 至 它.

这个 是 有用的 如果 这 用户 需要 同时发生的 updating 的 两个都

dac 输出. 这 用户 将 写 至 两个都 输入 寄存器 indi-

vidually 和 然后, 用 pulsing 这

LDAC

输入 低, 两个都 输出

将 更新 同时发生地.

这些 部分 包含 一个 extra 特性 凭此 这 dac 寄存器

是 不 updated 除非 它的 输入 寄存器 有 被 updated 自从

这 last 时间 那

LDAC

是 brought 低. 正常情况下, 当

LDAC

是 brought 低, 这 dac 寄存器 是 filled 和 这

一个

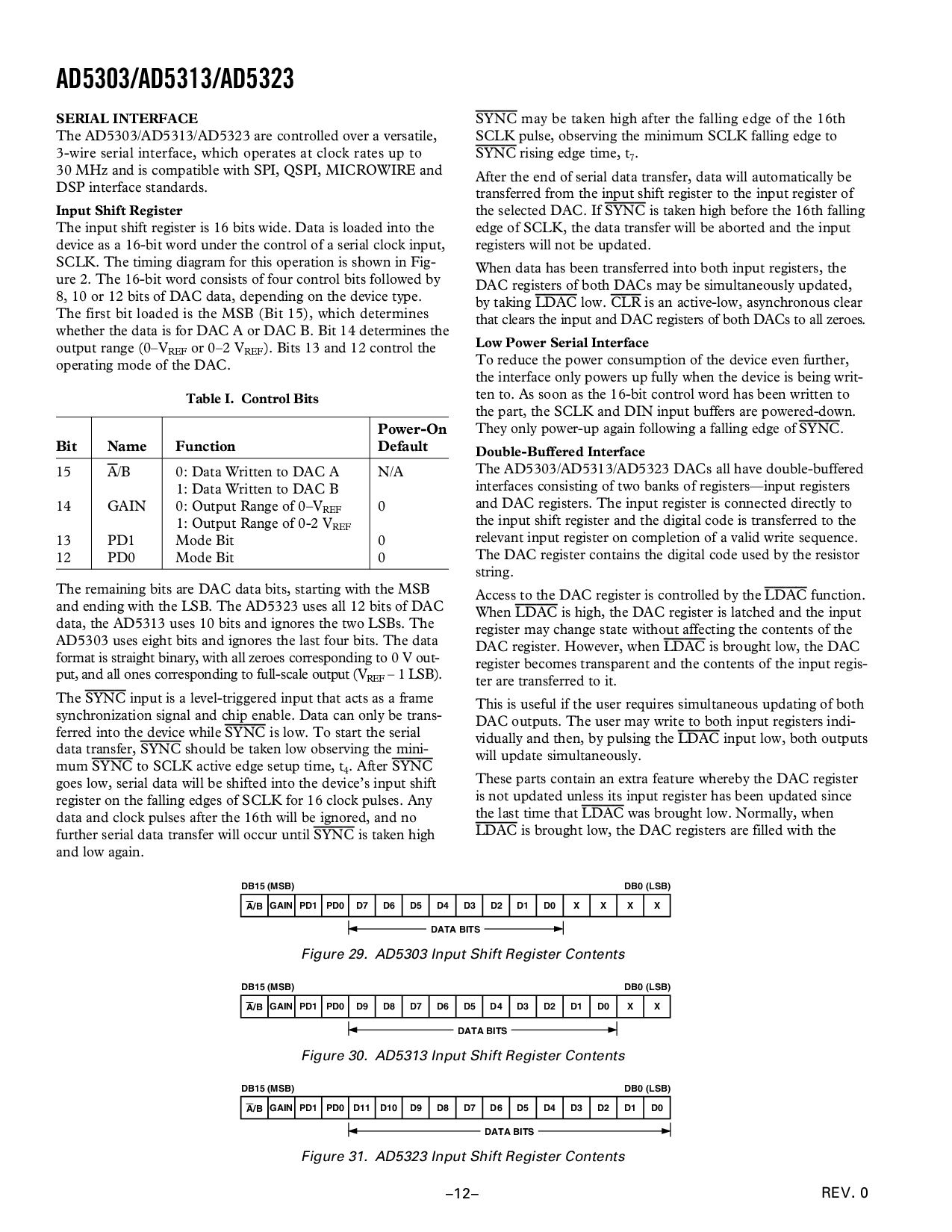

/b

增益

PD1 PD0 D7 D6 D5 D4 D3 D2 D1 D0 X X X X

db0 (lsb)db15 (msb)

数据 位

图示 29. ad5303 输入 变换 寄存器 内容

一个

/b

增益

PD1 PD0 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 X X

db0 (lsb)db15 (msb)

数据 位

图示 30. ad5313 输入 变换 寄存器 内容

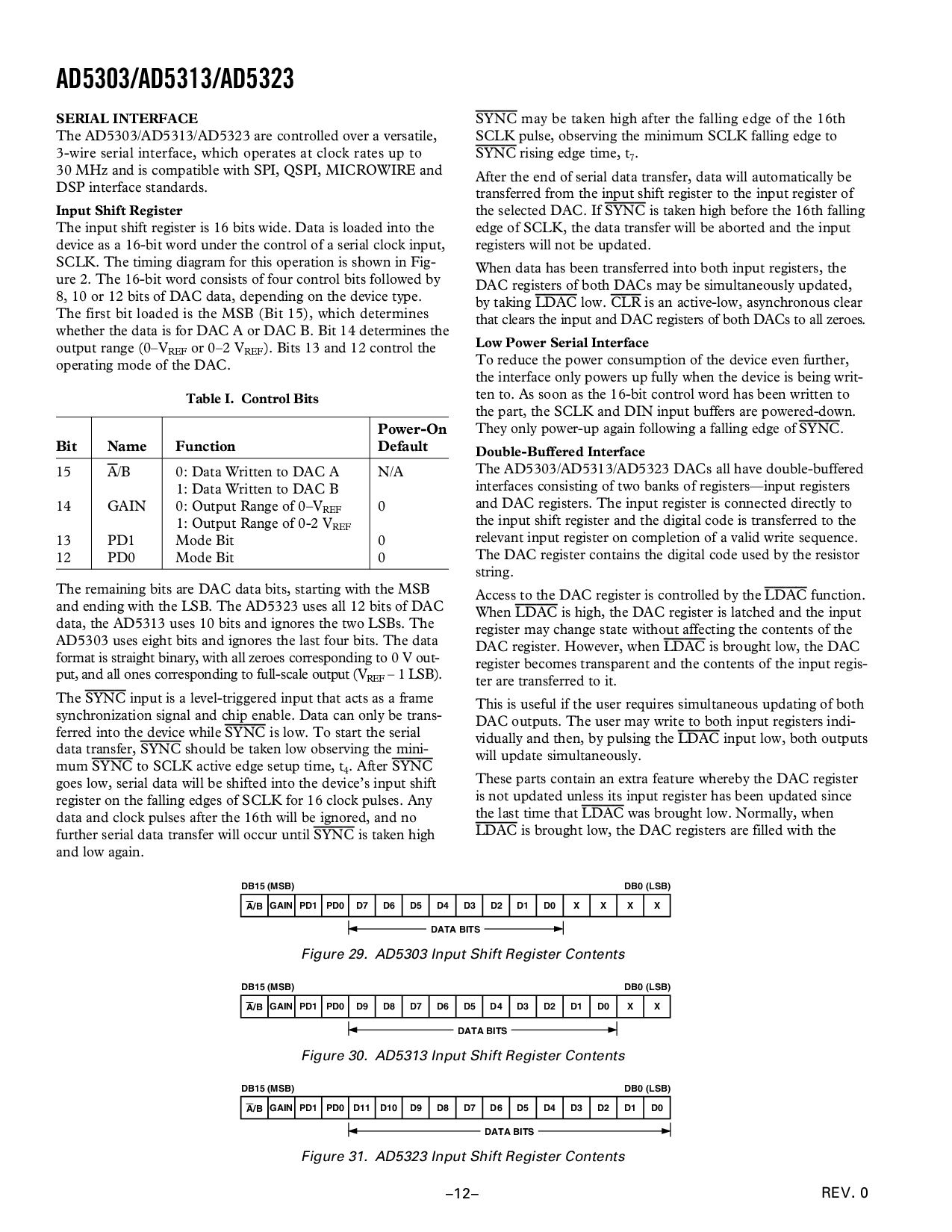

一个

/b

增益

PD1 PD0 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

db0 (lsb)db15 (msb)

数据 位

图示 31. ad5323 输入 变换 寄存器 内容