rev. 0

AD73322L

–5–

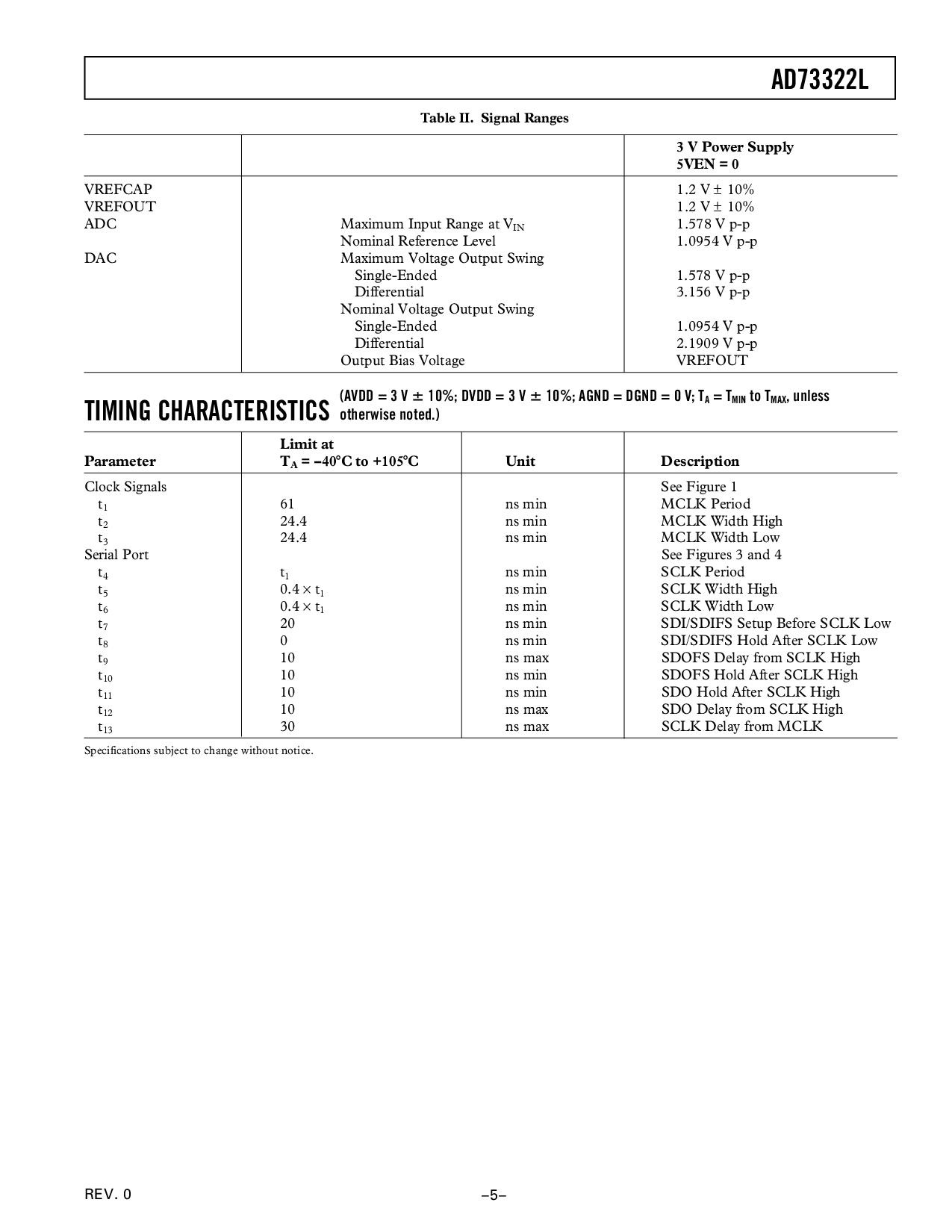

表格 ii. 信号 范围

3 v 电源 供应

5ven = 0

VREFCAP 1.2 v

±

10%

VREFOUT 1.2 v

±

10%

模数转换器 最大 输入 范围 在 v

在

1.578 v p-p

名义上的 涉及 水平的 1.0954 v p-p

DAC 最大 电压 输出 摆动

单独的-结束 1.578 v p-p

差别的 3.156 v p-p

名义上的 电压 输出 摆动

单独的-结束 1.0954 v p-p

差别的 2.1909 v p-p

输出 偏差 电压 VREFOUT

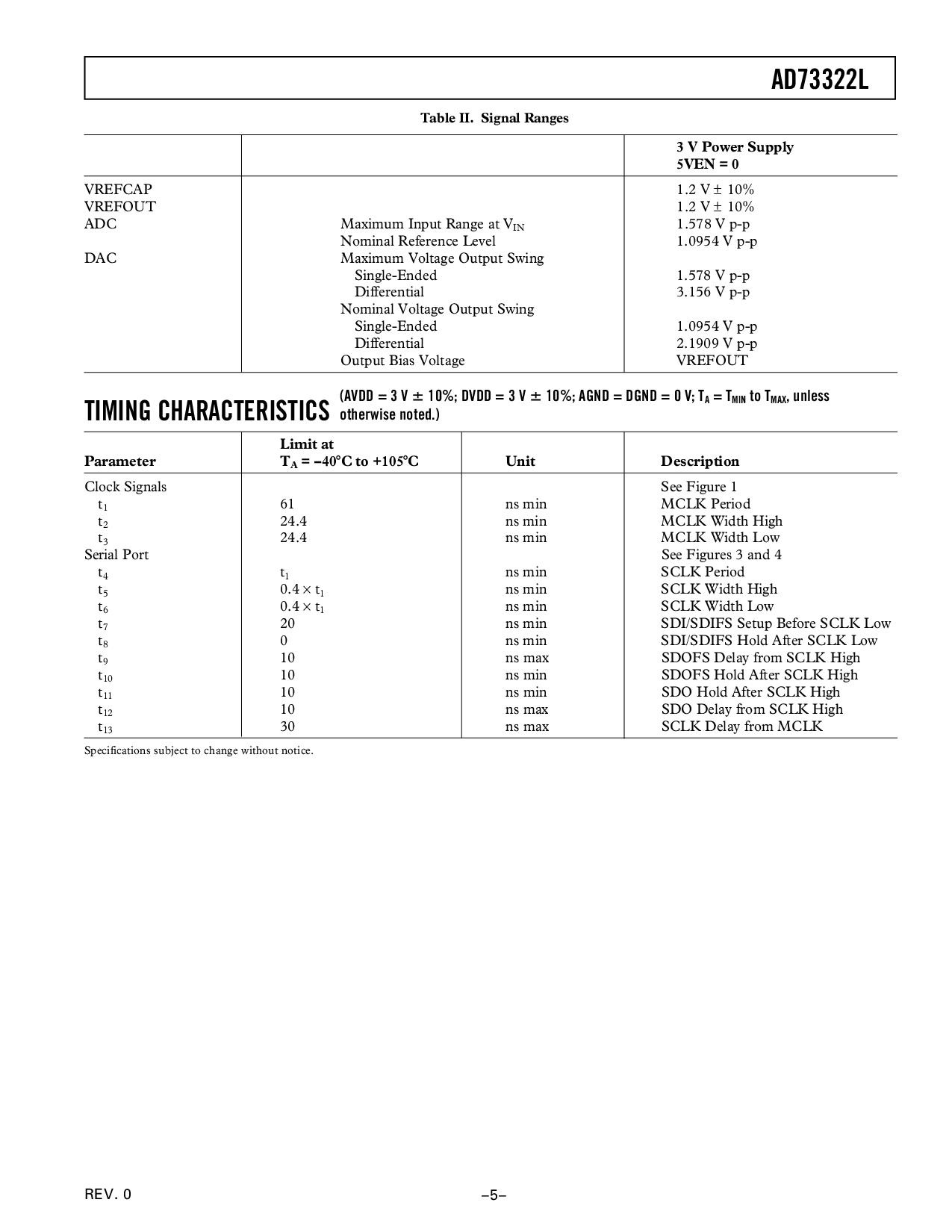

定时 特性

限制 在

参数 T

一个

= –40

c 至 +105

C 单位 描述

时钟 信号 看 图示 1

t

1

61 ns 最小值 mclk 时期

t

2

24.4 ns 最小值 mclk 宽度 高

t

3

24.4 ns 最小值 mclk 宽度 低

串行 端口 看 计算数量 3 和 4

t

4

t

1

ns 最小值 sclk 时期

t

5

0.4

×

t

1

ns 最小值 sclk 宽度 高

t

6

0.4

×

t

1

ns 最小值 sclk 宽度 低

t

7

20 ns 最小值 sdi/sdifs 建制 在之前 sclk 低

t

8

0 ns 最小值 sdi/sdifs 支撑 之后 sclk 低

t

9

10 ns 最大值 sdofs 延迟 从 sclk 高

t

10

10 ns 最小值 sdofs 支撑 之后 sclk 高

t

11

10 ns 最小值 sdo 支撑 之后 sclk 高

t

12

10 ns 最大值 sdo 延迟 从 sclk 高

t

13

30 ns 最大值 sclk 延迟 从 mclk

规格 主题 至 改变 没有 注意.

(avdd = 3 v

10%; dvdd = 3 v

10%; agnd = dgnd = 0 v; t

一个

= t

MlN

至 t

最大值

, 除非

否则 指出.)