AD7715

–5–

rev. c

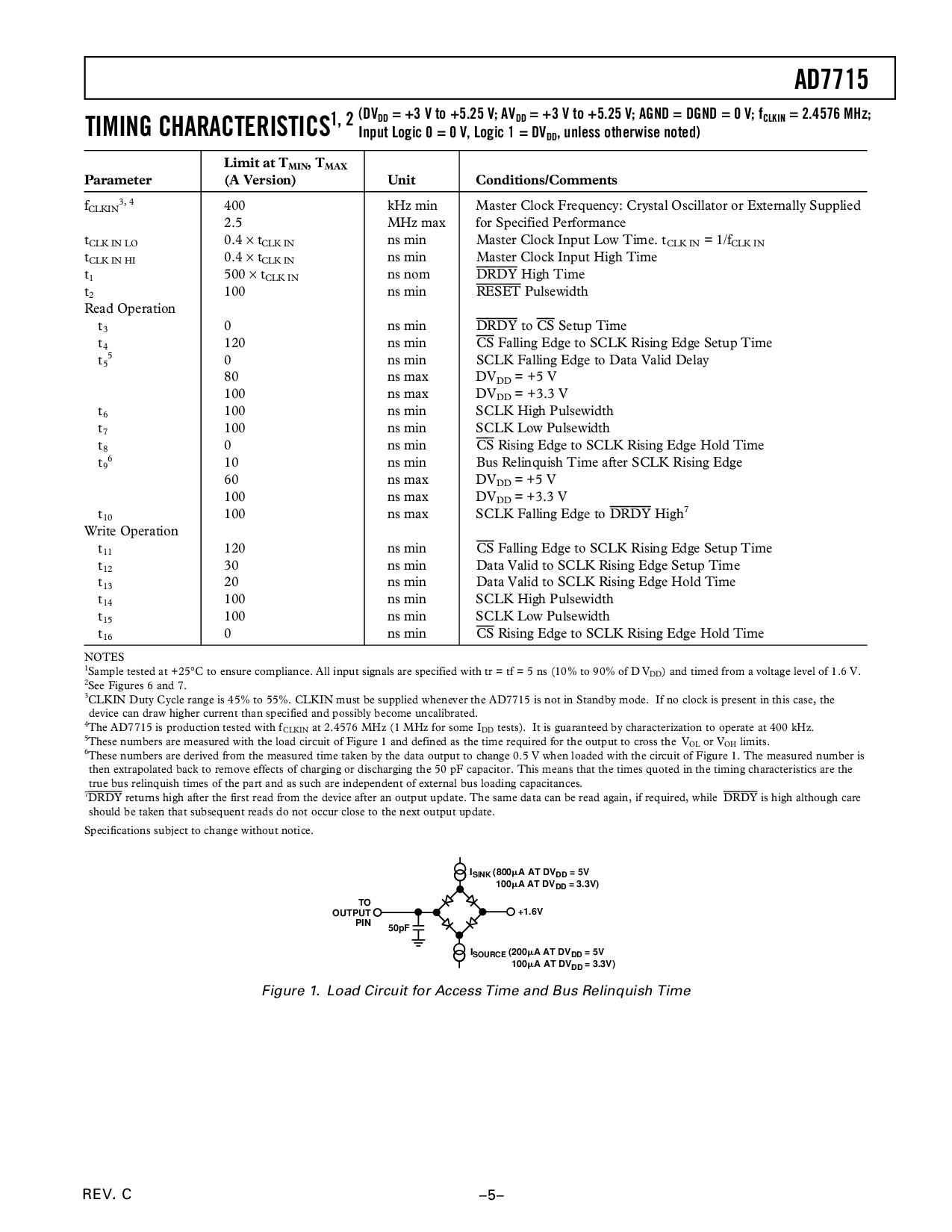

定时 特性

1, 2

限制 在 t

最小值

, t

最大值

参数 (一个 版本) 单位 情况/comments

f

CLKIN

3, 4

400 khz 最小值 主控 时钟 频率: 结晶 振荡器 或者 externally 有提供的

2.5 mhz 最大值 为 指定 效能

t

clk 在 lo

0.4

×

t

clk 在

ns 最小值 主控 时钟 输入 低 时间. t

clk 在

= 1/f

clk 在

t

clk 在 hi

0.4

×

t

clk 在

ns 最小值 主控 时钟 输入 高 时间

t

1

500

×

t

clk 在

ns nom

DRDY

高 时间

t

2

100 ns 最小值

重置

Pulsewidth

读 运作

t

3

0 ns 最小值

DRDY

至

CS

建制 时间

t

4

120 ns 最小值

CS

下落 边缘 至 sclk rising 边缘 建制 时间

t

5

5

0 ns 最小值 sclk 下落 边缘 至 数据 有效的 延迟

80 ns 最大值 DV

DD

= +5␣ V

100 ns 最大值 DV

DD

= +3.3␣ V

t

6

100 ns 最小值 sclk 高 pulsewidth

t

7

100 ns 最小值 sclk 低 pulsewidth

t

8

0 ns 最小值

CS

rising 边缘 至 sclk rising 边缘 支撑 时间

t

9

6

10 ns 最小值 总线 relinquish 时间 之后 sclk rising 边缘

60 ns 最大值 DV

DD

= +5␣ V

100 ns 最大值 DV

DD

= +3.3␣ V

t

10

100 ns 最大值 sclk 下落 边缘 至

DRDY

高

7

写 运作

t

11

120 ns 最小值

CS

下落 边缘 至 sclk rising 边缘 建制 时间

t

12

30 ns 最小值 数据 有效的 至 sclk rising 边缘 建制 时间

t

13

20 ns 最小值 数据 有效的 至 sclk rising 边缘 支撑 时间

t

14

100 ns 最小值 sclk 高 pulsewidth

t

15

100 ns 最小值 sclk 低 pulsewidth

t

16

0 ns 最小值

CS

rising 边缘 至 sclk rising 边缘 支撑 时间

注释

1

样本 测试 在 +25

°

c 至 确保 遵从. 所有 输入 信号 是 指定 和 tr = tf = 5 ns (10% 至 90% 的 d V

DD

) 和 安排时间 从 一个 电压 水平的 的 1.6 v.

2

看 计算数量 6 和 7.

3

clkin 职责 循环 范围 是 45% 至 55%. clkin 必须 是 有提供的 whenever 这 ad7715 是 不 在 备用物品 模式. 如果 非 时钟 是 呈现 在 这个 情况, 这

设备 能 绘制 高等级的 电流 比 指定 和 possibly 变为 uncalibrated.

4

这 ad7715 是 生产 测试 和 f

CLKIN

在 2.4576␣ mhz (1␣ mhz 为 一些 i

DD

tests). 它 是 有保证的 用 描绘 至 运作 在 400␣ khz.

5

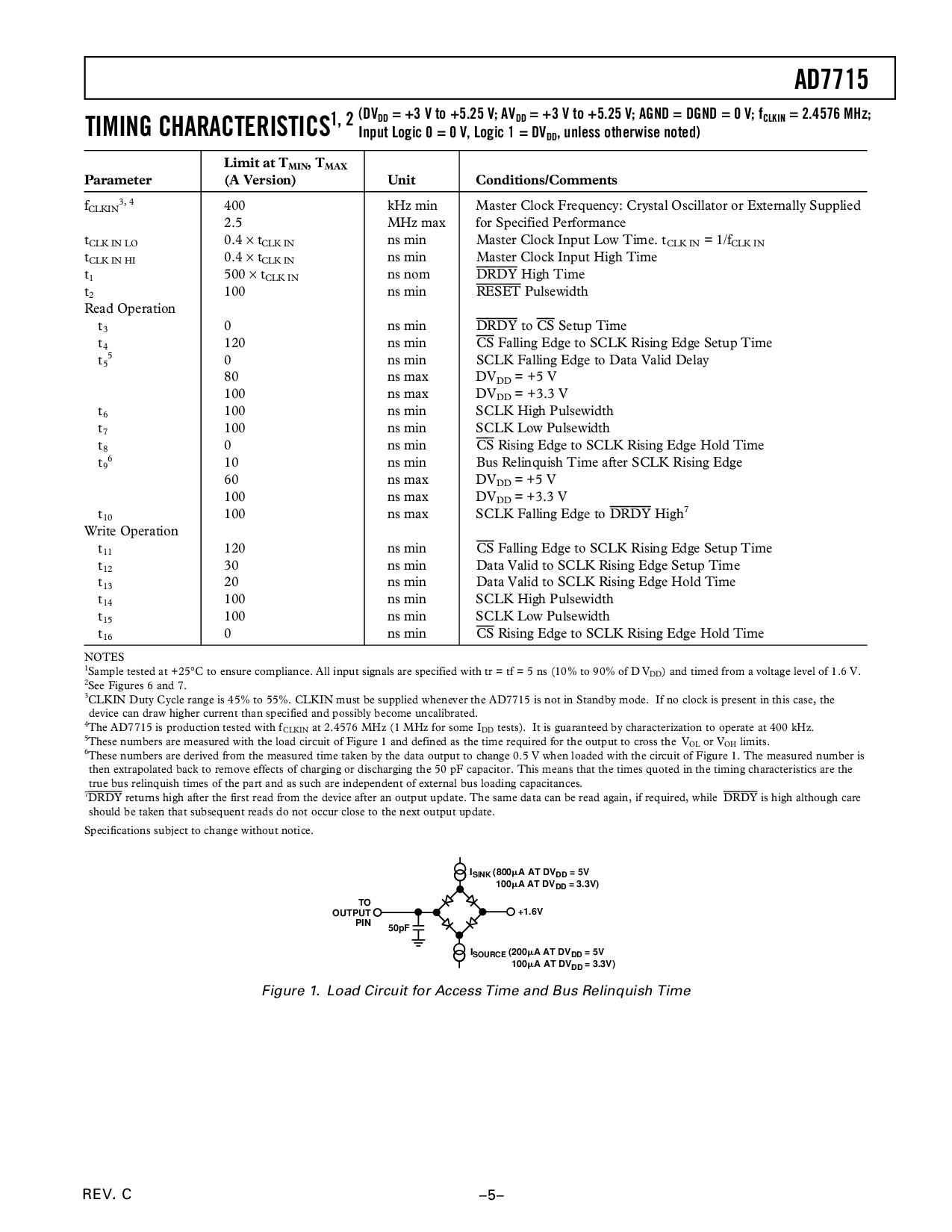

这些 号码 是 量过的 和 这 加载 电路 的 图示 1 和 定义 作 这 时间 必需的 为 这 输出 至 交叉 这 V

OL

或者 v

OH

限制.

6

这些 号码 是 获得 从 这 量过的 时间 带去 用 这 数据 输出 至 改变 0.5␣ v 当 承载 和 这 电路 的 图示 1. 这 量过的 号码 是

然后 extrapolated 后面的 至 除去 影响 的 charging 或者 discharging 这 50 pf 电容. 这个 意思 那 这 时间 quoted 在 这 定时 特性 是 这

真实 总线 relinquish 时间 的 这 部分 和 作 此类 是 独立 的 外部 总线 加载 capacitances.

7

DRDY

returns 高 之后 这 第一 读 从 这 设备 之后 一个 输出 更新. 这 一样 数据 能 是 读 又一次, 如果 必需的, 当

DRDY

是 高 虽然 小心

应当 是 带去 那 subsequent 读 做 不 出现 关闭 至 这 next 输出 更新.

规格 主题 至 改变 没有 注意.

至

输出

管脚

+1.6v

I

下沉

(800

一个 在 dv

DD

= 5v

100

一个 在 dv

DD

= 3.3v)

50pF

I

源

(200

一个 在 dv

DD

= 5v

100

一个 在 dv

DD

= 3.3v)

图示 1. 加载 电路 为 进入 时间 和 总线 relinquish 时间

(dv

DD

= +3␣ v 至 +5.25␣ v; av

DD

= +3␣ v 至 +5.25␣ v; agnd = dgnd = 0 v; f

CLKIN

= 2.4576␣ mhz;

输入 逻辑 0 = 0 v, 逻辑 1 = dv

DD

, 除非 否则 指出)