rev. 0

AD7738

–7–

管脚 函数 描述

管脚 非. Mnemonic 描述

1 SCLK 串行 时钟. 施密特-triggered 逻辑 输入. 一个 外部 串行 时钟 是 应用 至 这个 输入 至 转移

串行 数据 至 或者 从 这 ad7738.

2 MCLKIN 主控 时钟 信号 为 这 模数转换器. 这个 能 是 提供 在 这 表格 的 一个 结晶/共振器 或者 外部

时钟. 一个 结晶/共振器 能 是 系 横过 这 mclkin 和 mclkout 管脚. alternatively, 这 mclkin

管脚 能 是 驱动 和 一个 cmos 兼容 时钟 和 mclkout left unconnected.

3MCLKOUT 当 这 主控 时钟 为 这 设备 是 一个 结晶/共振器, 这 结晶/共振器 是 连接 在

mclkin 和 mclkout. 如果 一个 外部 时钟 是 应用 至 这 mclkin, mclkout 提供 一个

inverted 时钟 信号 或者 能 是 切换 止 至 更小的 这 设备 电源 消耗量. mclkout 是

有能力 的 驱动 一个 cmos 加载.

4

CS

碎片 选择. 起作用的 低 施密特 triggered 逻辑 输入 和 一个 内部的 拉-向上 电阻. 和 这个 输入

hardwired 低, 这 ad7738 能 运作 在 它的 3-线 接口 模式 使用 sclk, din, 和 dout.

CS

能 是 使用 至 选择 这 设备 在 系统 和 更多 比 一个 设备 在 这 串行 总线. 它 能 也 是 使用 作

一个 8-位 框架 同步 信号.

5

重置

施密特-triggered 逻辑 输入. 起作用的 低 输入 那 resets 这 控制 逻辑, 接口 逻辑, 数字的 filter,

相似物 modulator, 和 所有 在-碎片 寄存器 的 这 部分 至 电源-在 状态. effectively, everything 在 这

部分 除了 这 时钟 振荡器 是 重置 当 这

重置

管脚 是 exercised.

6AV

DD

相似物 积极的 供应 电压. 5 v 至 agnd 名义上的.

7 aincom/p0 相似物 输入 一般 终端/数字的 输出. 这 管脚 是 决定 用 这 p0 dir 位; 这 数字的

value 能 是 写 作 这 p0 位 在 这 i/o 端口 寄存器. 这 数字的 电压 是 关联 至 相似物

供应. 当 配置 作 一个 输入 (p0 dir 位 设置 至 1), 这 单独的-结束 相似物 输入 0 至 7 能 是

关联 至 这个 管脚’s 电压 水平的.

8

同步

/p1

同步

/数字的 输入/数字的 输出. 这 管脚 方向 是 决定 用 这 p1 dir 位; 这 数字的 值

能 是 读/写 作 这 p1 位 在 这 i/o 端口 寄存器. 当 这 同步 使能 位 在 这 i/o 端口

寄存器 是 设置 至 1, 这

同步

/p1 管脚 能 是 使用 至 同步 这 ad7738 modulator 和 数字的 过滤

和 其它 设备 在 这 系统. 这 数字的 电压 是 关联 至 这 相似物 供应. 当 配置

作 一个 输入, 这 管脚 应当 是 系 高 或者 低.

9–12, AIN0–AIN7 相似物 输入

17–20

13 muxout(+) 相似物 多路调制器 积极的 输出

14 muxout(–) 相似物 多路调制器 负的 输出

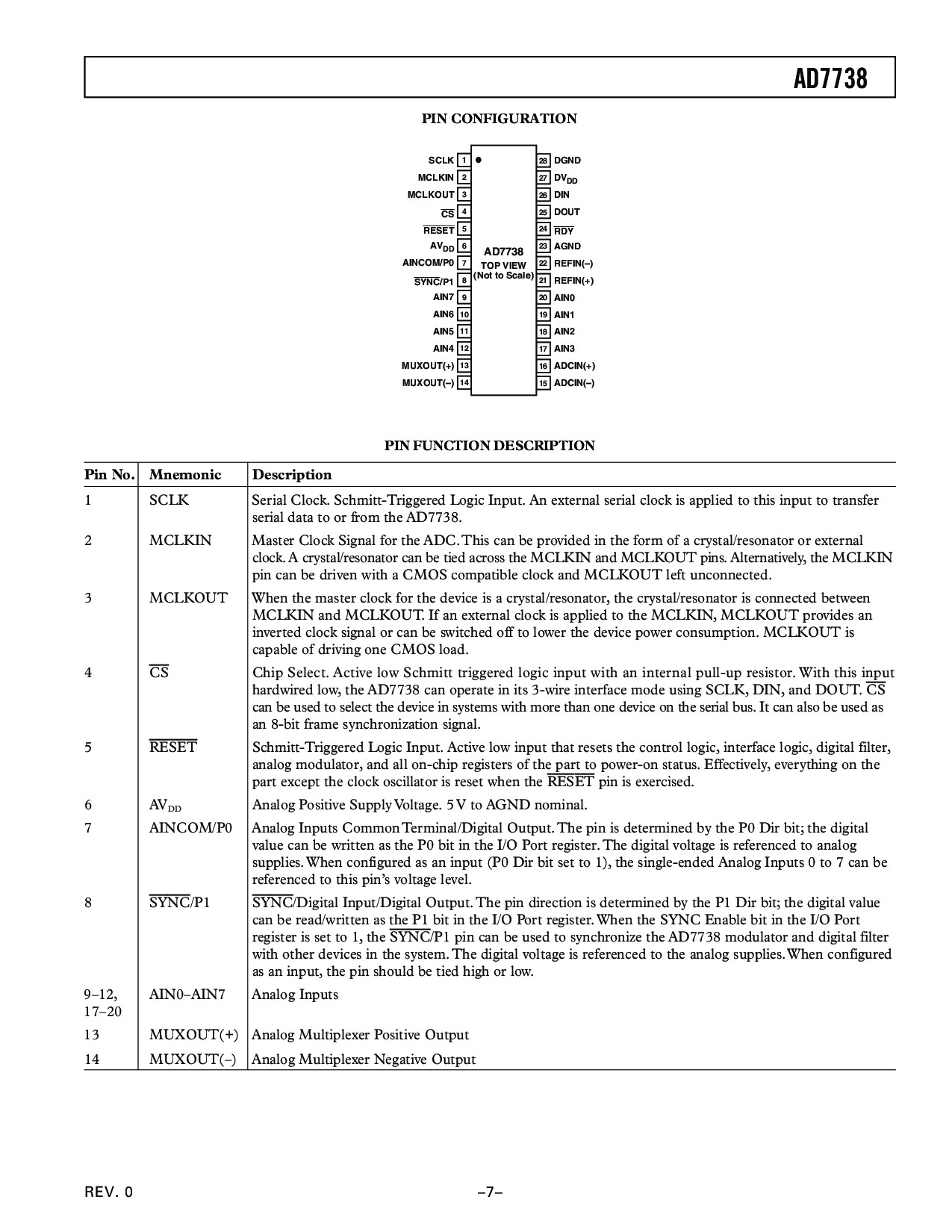

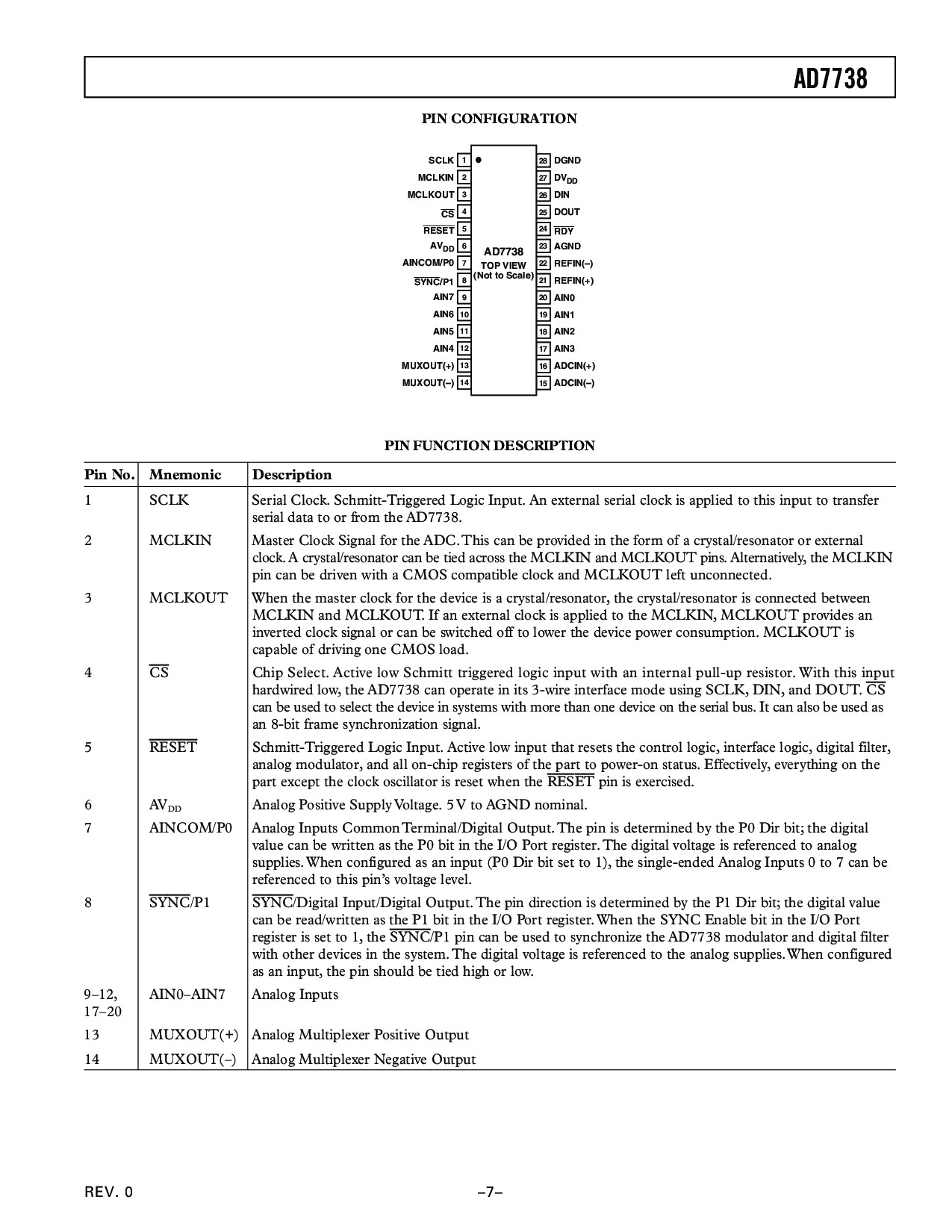

管脚 配置

顶 视图

(不 至 规模)

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

AD7738

SCLK

DGND

MCLKIN

DV

DD

MCLKOUT

DIN

CS

DOUT

重置

RDY

AV

DD

AGND

aincom/p0

refin(–)

同步

/p1

refin(+)

AIN7

AIN0

AIN6

AIN1

AIN5

AIN2

AIN4

AIN3

muxout(+)

adcin(+)

muxout(–)

adcin(–)