rev. c

–3–

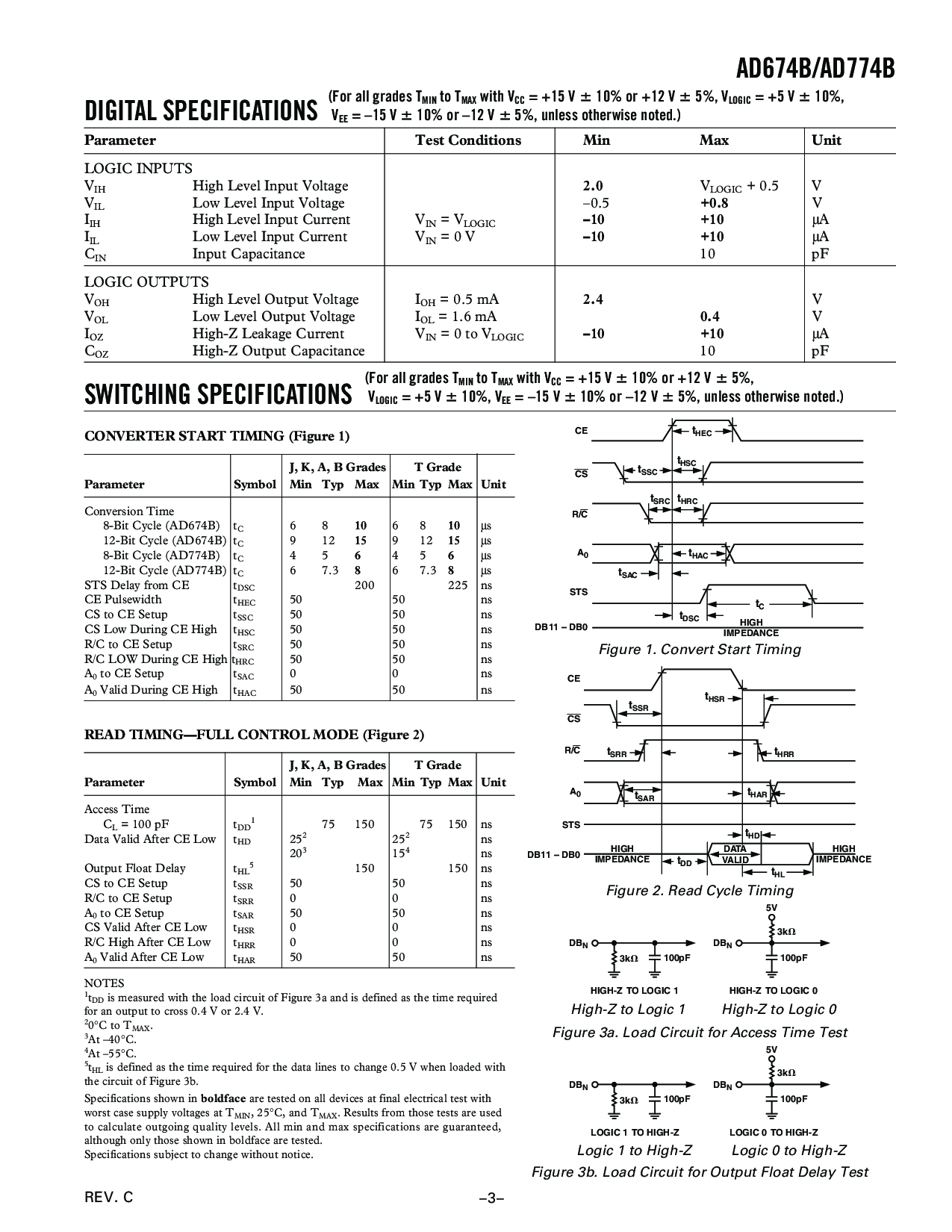

转换器 开始 定时 (图示 1)

j, k, 一个, b grades t 等级

参数 标识 最小值 典型值 最大值 最小值 典型值 最大值 单位

转换 时间

8-位 循环 (ad674b) t

C

68

10

68

10

µ

s

12-位 循环 (ad674b) t

C

912

15

912

15

µ

s

8-位 循环 (ad774b) t

C

45

6

45

6

µ

s

12-位 循环 (ad774b) t

C

6 7.3

8

6 7.3

8

µ

s

sts 延迟 从 ce t

DSC

200 225 ns

ce pulsewidth t

HEC

50 50 ns

CS

至 ce 建制 t

SSC

50 50 ns

CS

低 在 ce 高 t

HSC

50 50 ns

r/

C

至 ce 建制 t

SRC

50 50 ns

r/

C

低 在 ce 高 t

HRC

50 50 ns

一个

0

至 ce 建制 t

SAC

00ns

一个

0

有效的 在 ce 高 t

HAC

50 50 ns

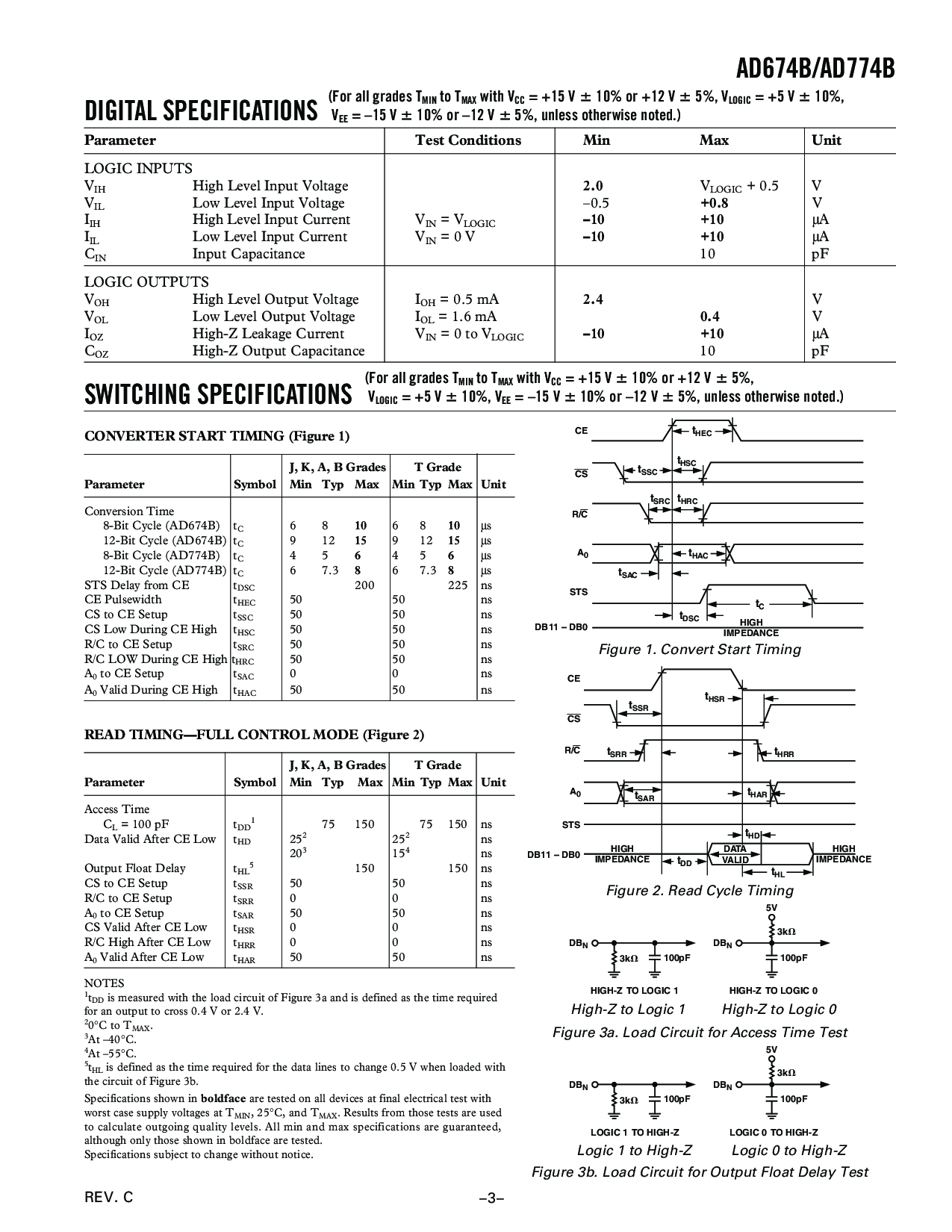

读 timing—full 控制 模式 (图示 2)

j, k, 一个, b grades t 等级

参数 标识 最小值 典型值 最大值 最小值 典型值 最大值 单位

进入 时间

C

L

= 100 pf t

DD

1

75 150 75 150 ns

数据 有效的 之后 ce 低 t

HD

25

2

25

2

ns

20

3

15

4

ns

输出 float 延迟 t

HL

5

150 150 ns

CS

至 ce 建制 t

SSR

50 50 ns

r/

C

至 ce 建制 t

SRR

00ns

一个

0

至 ce 建制 t

SAR

50 50 ns

CS

有效的 之后 ce 低 t

HSR

00ns

r/

C

高 之后 ce 低 t

HRR

00ns

一个

0

有效的 之后 ce 低 t

HAR

50 50 ns

注释

1

t

DD

是 量过的 和 这 加载 电路 的 图示 3a 和 是 定义 作 这 时间 必需的

为 一个 输出 至 交叉 0.4 v 或者 2.4 v.

2

0

°

c 至 t

最大值

.

3

在 –40

°

c.

4

在 –55

°

c.

5

t

HL

是 定义 作 这 时间 必需的 为 这 数据 线条至 改变 0.5 v 当 承载 和

这 电路 的 图示 3b.

规格 显示 在

黑体字

是 测试 在 所有 设备 在 最终 电的 测试 和

worst 情况 供应 电压 在 t

最小值

, 25

°

c, 和 t

最大值

. 结果 从 那些 tests 是 使用

至 计算 优于 质量 水平. 所有 最小值 和 最大值 规格 是 有保证的,

虽然 仅有的 那些 显示 在 黑体字 是 测试.

规格 主题 至 改变 没有 注意.

参数 测试 情况 最小值 最大值 单位

逻辑 输入

V

IH

高 水平的 输入 电压

2.0

V

逻辑

+ 0.5 V

V

IL

低 水平的 输入 电压 –0.5

+0.8

V

I

IH

高 水平的 输入 电流 V

在

= v

逻辑

–10 +10

µ

一个

I

IL

低 水平的 输入 电流 V

在

= 0 v

–10 +10

µ

一个

C

在

输入 电容 10 pF

逻辑 输出

V

OH

高 水平的 输出 电压 I

OH

= 0.5 毫安

2.4

V

V

OL

低 水平的 输出 电压 I

OL

= 1.6 毫安

0.4

V

I

OZ

高-z 泄漏 电流 V

在

= 0 至 v

逻辑

–10 +10

µ

一个

C

OZ

高-z 输出 电容 10 pF

数字的 规格

(为 所有 grades t

最小值

至 t

最大值

和 v

CC

= +15 v

10% 或者 +12 v

5%, v

逻辑

= +5 v

10%,

V

EE

= –15 v

10% 或者 –12 v

5%, 除非 否则 指出.)

切换 规格

(为 所有 grades t

最小值

至 t

最大值

和 v

CC

= +15 v

10% 或者 +12 v

5%,

V

逻辑

= +5 v

10%, v

EE

= –15 v

10% 或者 –12 v

5%, 除非 否则 指出.)

t

HEC

t

HSC

t

SSC

t

HRC

t

SRC

t

SAC

t

HAC

t

C

t

DSC

CE

CS

r/

C

一个

0

STS

DB11

–

DB0

高

阻抗

图示 1. 转变 开始 定时

t

SSR

CE

CS

r/

C

一个

0

STS

DB11

–

DB0

t

HSR

t

HRR

t

HAR

t

HD

t

SAR

t

SRR

高

阻抗

数据

VALID

高

阻抗

t

HL

t

DD

图示 2. 读 循环 定时

DB

N

3k

100pF

DB

N

3k

100pF

5V

高-z 至 逻辑 0high-z 至 逻辑 1

高-z 至 逻辑 1 高-z 至 逻辑 0

图示 3a. 加载 电路 为 进入 时间 测试

DB

N

3k

100pF

逻辑 1 至 高-z

DB

N

3k

100pF

5V

逻辑 0 至 高-z

逻辑 1 至 高-z 逻辑 0 至 高-z

图示 3b. 加载 电路 为 输出 float 延迟 测试

ad674b/ad774b