初步的 技术的 数据

AD9725

rev. pra | 页 5 的 16

数字的 规格

表格 3. t

最小值

至 t

最大值

, avdd1, avdd2, dbvdd = 3.3 v, advdd, acvdd, clkvdd, dvdd = 2.5 v , i

OUTFS

= 20 毫安, 除非

否则 指出. 规格 主题 至 改变 没有 注意.

参数 情况 最小值 典型值 最大值 单位

数字的 输入 vcm = 0.875 v 至 1.575 v

差别的 逻辑 ‘1’

(放 在 footnote, 和 delete

column?)

0.1 0.6 v

差别的 逻辑 ‘0’ –0.6 –0.1 V

逻辑 ‘1’ 电流 3.5 毫安

逻辑 ‘0’ 电流 3.5 毫安

差别的 输入 阻抗 100 W

差别的 输入 电容 3 pF

数据 建制 时间 (t

DS

) 0.9 ns

数据 支撑 时间 (t

DH

) –0.3 ns

数据 时钟 输出 延迟 ( t

DCO

) 2.4 ns

串行 控制 总线

最大 sclk 频率 (fsclk) 15 MHz

最小 时钟 脉冲波 宽度 高 (t

PWH

) 30 ns

最小 时钟 脉冲波 宽度 低 (t

PWL

) 30 ns

最大 时钟 上升/下降 时间 1 ms

最小 数据/碎片 选择 设置 向上 时间 (t

DS

) 25 ns

最小 数据 支撑 时间 (t

DH

) 0 ns

最大 数据 有效的 时间 (t

DV

) 30 ns

重置 脉冲波 宽度 1.5 ns

输入 (sdi, sdio, sclk, csb)

逻辑 ‘1’ 电压 2.1 3 V

逻辑 ‘0’ 电压 0 0.9 V

逻辑 ‘1’ 电流 –10 +10 µA

逻辑 ‘0’ 电流 –10 +10 µA

输入 电容 5 pF

sdio 输出

逻辑 ‘1’ 电压 drvdd–0.6 V

逻辑 ‘0’ 电压 0.4 V

逻辑 ‘1’ 电流 30 50 毫安

逻辑 ‘0’ 电流 30 50 毫安

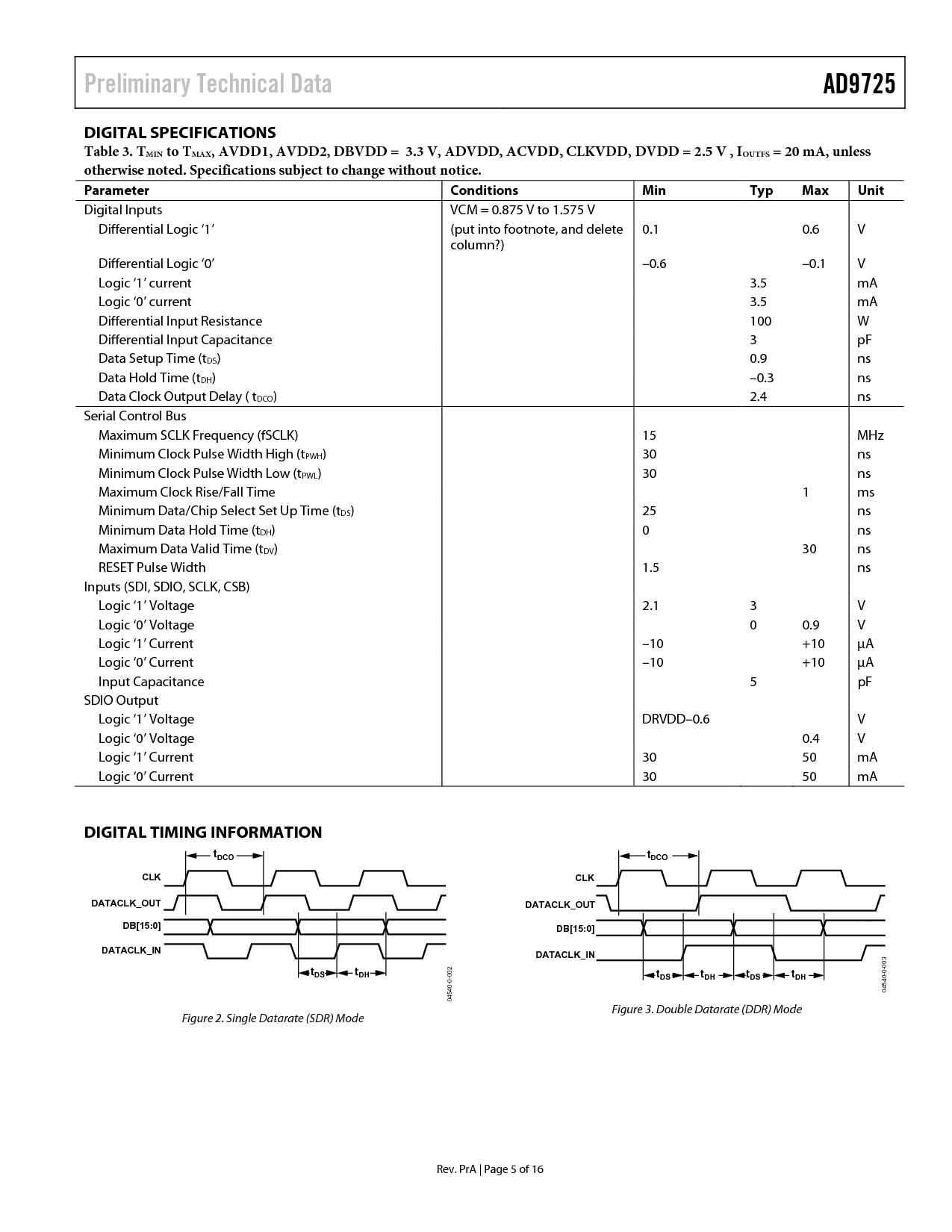

数字的 定时 信息

04540-0-002

CLK

db[15:0]

dataclk_在

dataclk_ou

T

t

DCO

t

DH

t

DS

图示 2. 单独的 datarate (sdr) 模式

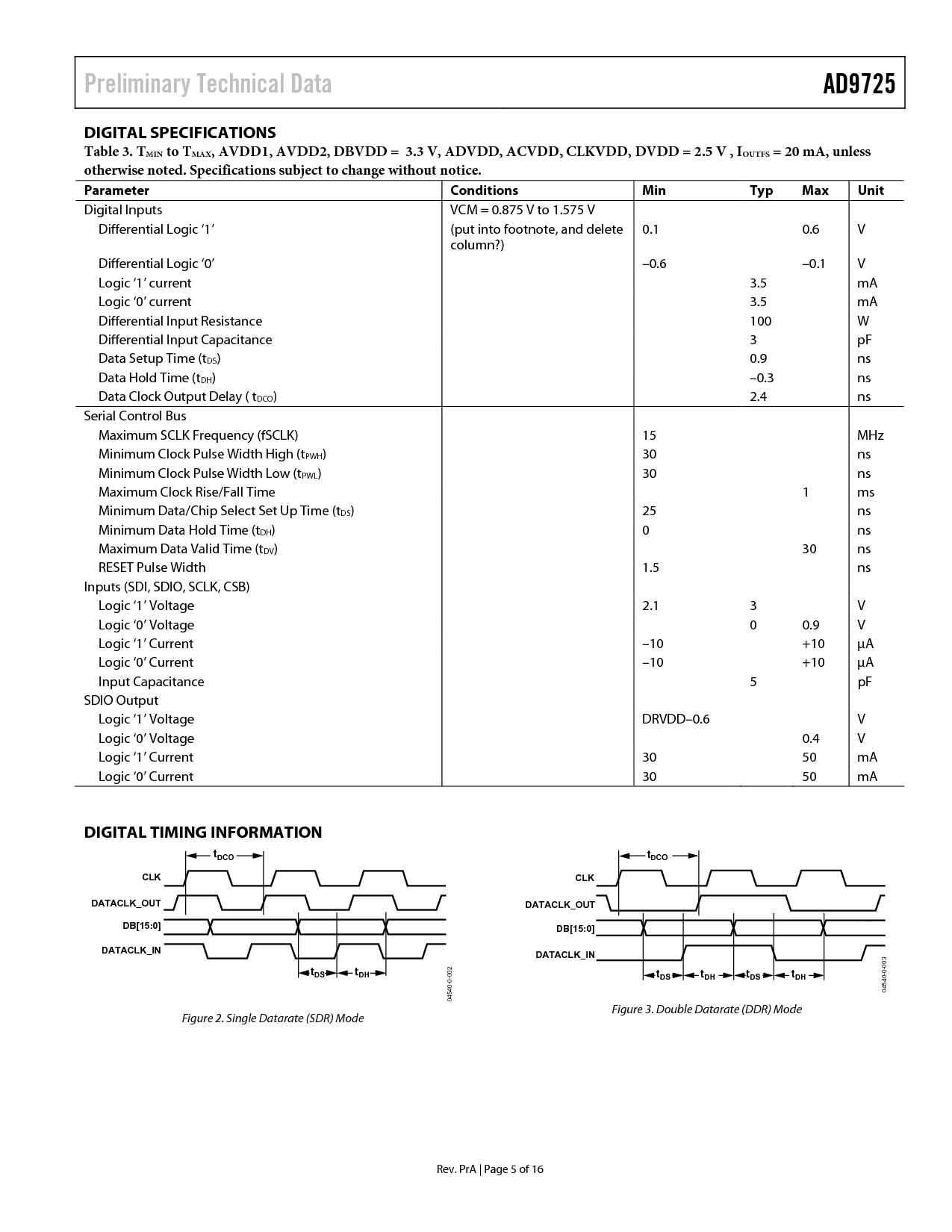

04540-0-003

t

DCO

t

DS

t

DH

t

DH

t

DS

CLK

db[15:0]

dataclk_在

dataclk_输出

图示 3. 翻倍 datarate (ddr) 模式