初步的 技术的 数据

AD9725

rev. pra | 页 9 的 16

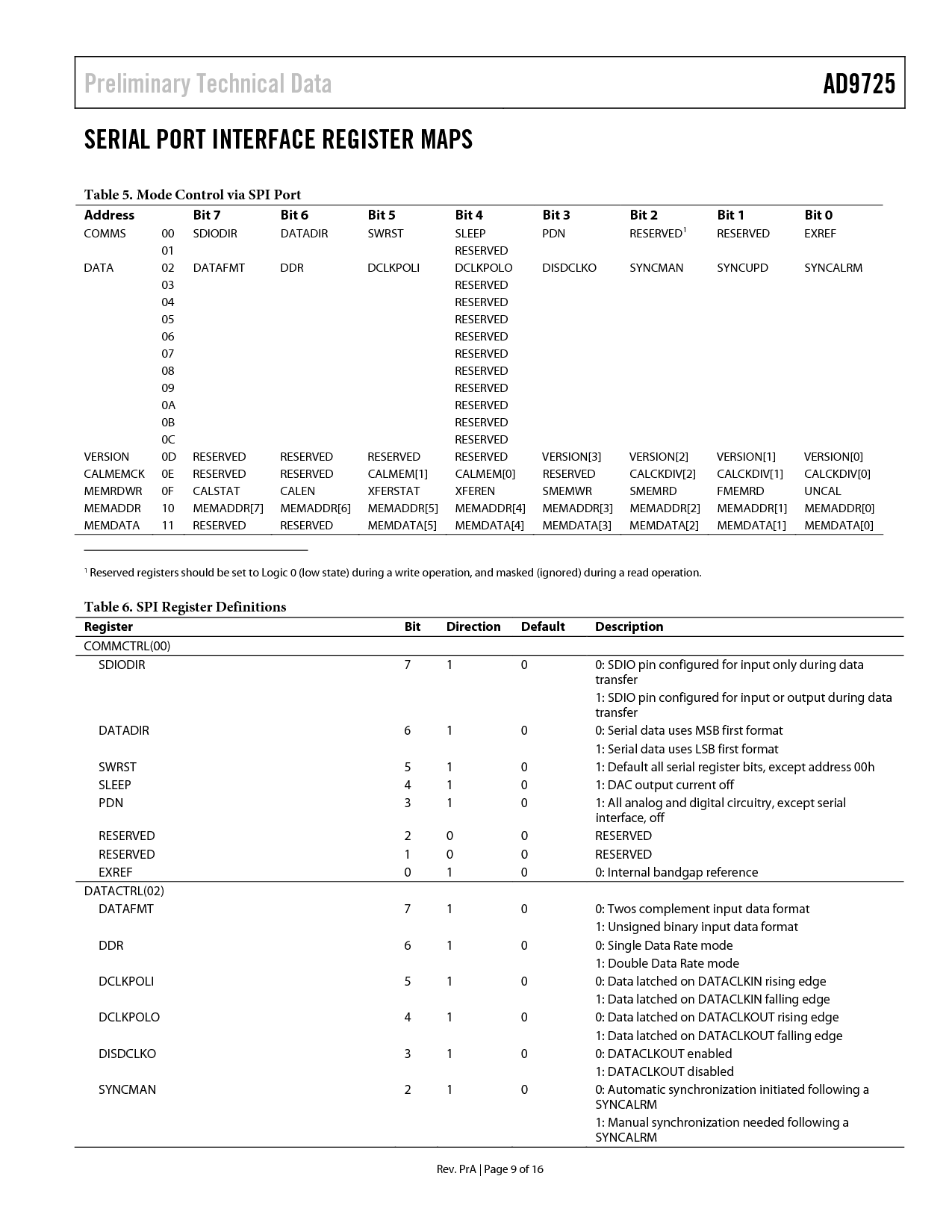

串行 端口 接口 寄存器 maps

表格 5. 模式 控制 通过 spi 端口

地址 位 7 位 6 位 5 位 4 位 3 位 2 位 1 位 0

comms 00 sdiodir DATADIR SWRST 睡眠 PDN 保留

1

保留 EXREF

01 保留

数据 02 datafmt ddr dclkpoli dclkpoloDISDCLKO SYNCMAN SYNCUPD SYNCALRM

03 保留

04 保留

05 保留

06 保留

07 保留

08 保留

09 保留

0a 保留

0b 保留

0c 保留

版本 0d 保留 保留 保留 保留 version[3] version[2] version[1] version[0]

calmemck 0e 保留 保留 calmem[1] calmem[0] reserved calckdiv[2] calckdiv[1] calckdiv[0]

memrdwr 0f calstat CALEN XFERSTAT XFEREN SMEMWR SMEMRD FMEMRD UNCAL

MEMADDR 10 memaddr[7] memaddr[6] memaddr[5] memaddr[4] memaddr[3] memaddr[2] memaddr[1] memaddr[0]

memdata 11 保留 保留 memdata[5] memdata[4] memdata[3] memdata[2] memdata[1] memdata[0]

1

保留 寄存器 应当 是 设置 至 逻辑 0 (低 状态) 在 一个 写 运作, 和 masked (ignored) 在 一个 读 运作.

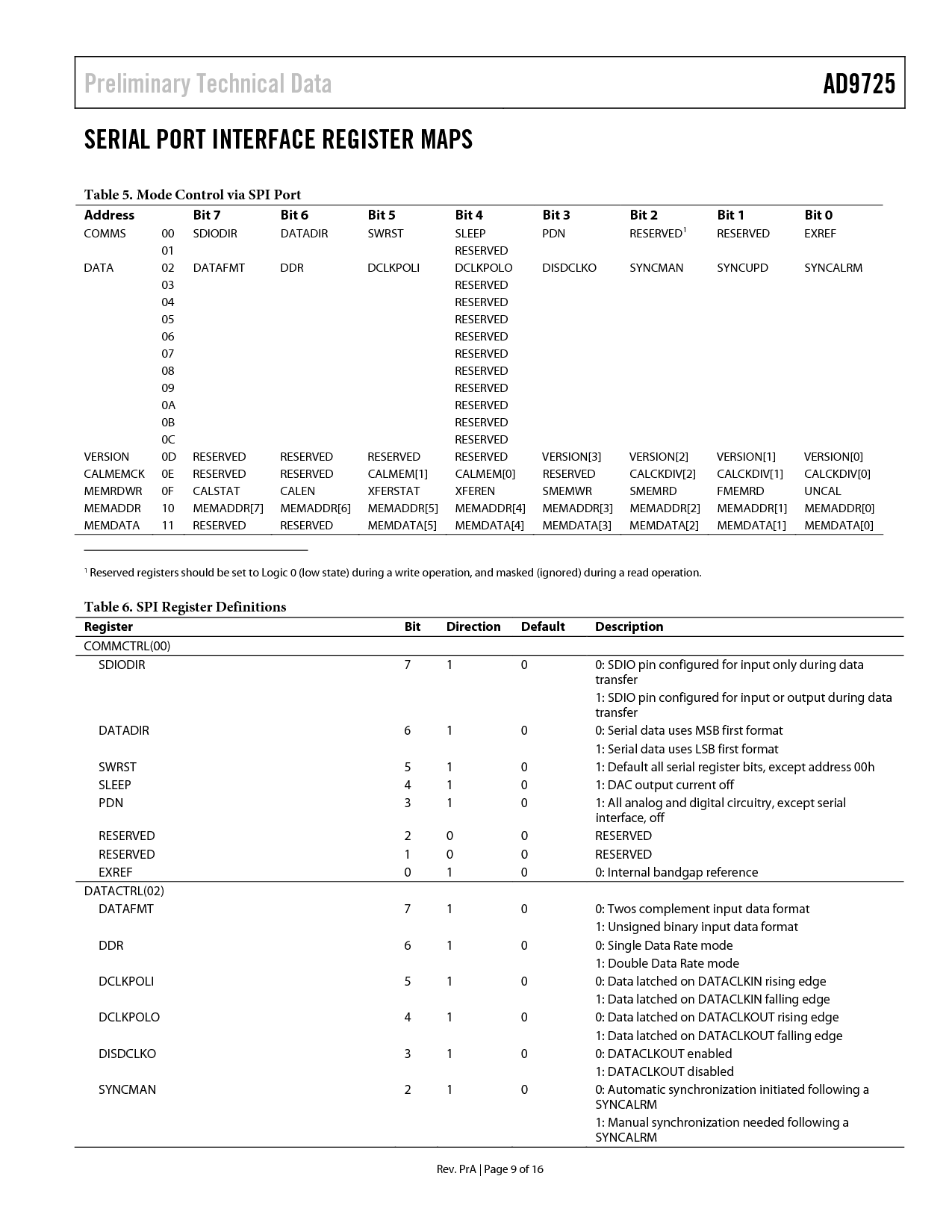

表格 6. spi 寄存器 定义

寄存器 位 方向 default 描述

commctrl(00)

SDIODIR 7 1 0 0: sdio 管脚 configured 为 输入 仅有的 在 数据

转移

1: sdio 管脚 配置 为 输入 或者 输出 在 数据

转移

DATADIR 6 1 0 0: 串行 数据 使用 msb 第一 format

1: 串行 数据 使用 lsb 第一 format

SWRST 5 1 0 1: default 所有 串行寄存器 位, 除了 地址 00h

睡眠 4 1 0 1: dac 输出 电流 止

PDN 3 1 0 1: 所有 相似物 和 数字的 电路系统, 除了 串行

接口, 止

保留 2 0 0 保留

保留 1 0 0 保留

EXREF 0 1 0 0: 内部的 bandgap 涉及

datactrl(02)

DATAFMT 7 1 0 0: twos complement 输入 数据 format

1: unsigned 二进制的 输入 数据 format

DDR 6 1 0 0: 单独的 数据 比率 模式

1: 翻倍 数据 比率 模式

DCLKPOLI 5 1 0 0: 数据 latched 在 dataclkin rising 边缘

1: 数据 latched 在 dataclkin 下落 边缘

DCLKPOLO 4 1 0 0: 数据 latched 在 dataclkout rising 边缘

1: 数据 latched 在 dataclkout 下落 边缘

disdclko 3 1 0 0: dataclkout 使能

1: dataclkout 无能

SYNCMAN 2 1 0 0: 自动 同步 initiated 下列的 一个

SYNCALRM

1: 手工的 同步 需要 下列的 一个

SYNCALRM