rev. 0

AD9887

–7–

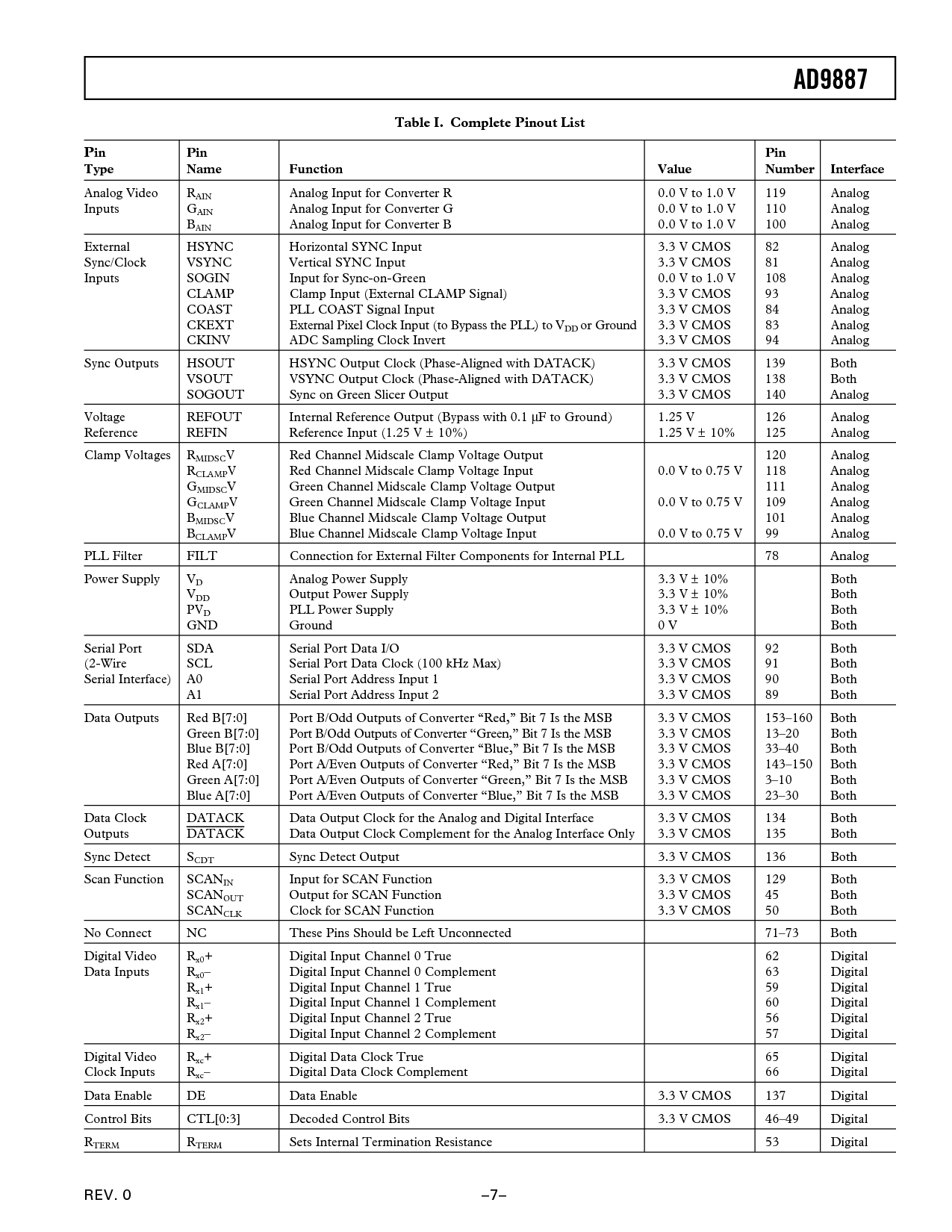

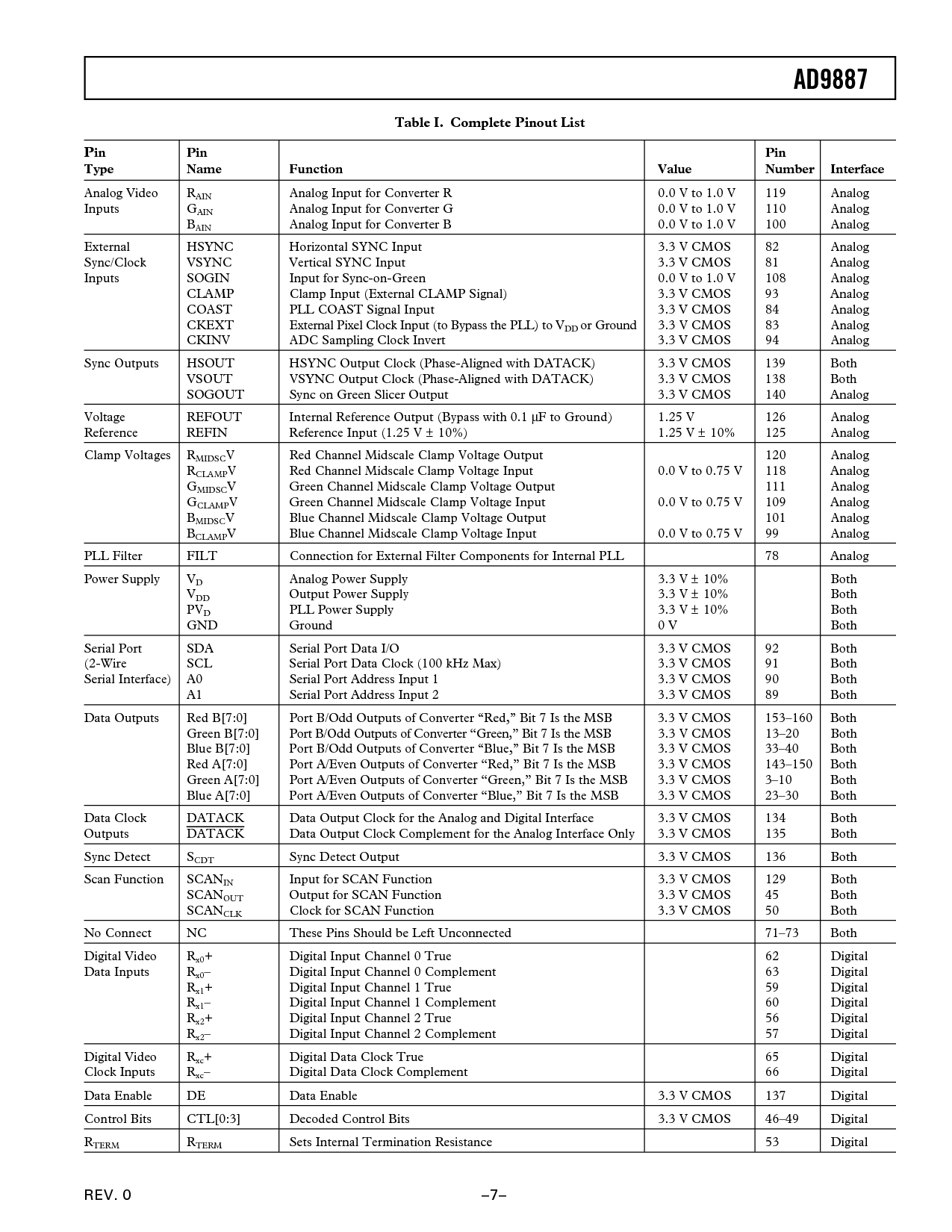

表格 i. 完全 引脚 列表

P

在 管脚 管脚

类型 名字 函数 值 号码 接口

相似物 video R

AIN

相似物 输入 为 转换器 r 0.0 v 至 1.0 v 119 相似物

输入 G

AIN

相似物 输入 为 转换器 g 0.0 v 至 1.0 v 110 相似物

B

AIN

相似物 输入 为 转换器 b 0.0 v 至 1.0 v 100 相似物

外部 HSYNC horizontal 同步 输入 3.3 v cmos 82 相似物

同步/时钟 VSYNC vertical 同步 输入 3.3 v cmos 81 相似物

输入 SOGIN 输入 为 同步-在-绿色 0.0 v 至 1.0 v 108 相似物

CLAMP clamp 输入 (外部 clamp 信号) 3.3 v cmos 93 相似物

COAST pll coast 信号 输入 3.3 v cmos 84 相似物

CKEXT 外部 pixel clock 输入 (至 绕过 这 pll) 至 v

DD

或者 地面 3.3 vCMOS 83 相似物

CKINV 模数转换器 抽样 时钟 invert 3.3 v cmos 94 相似物

同步 输出 HSOUT hsync 输出 时钟 (阶段-排整齐 和 datack) 3.3 v cmos 139 两个都

VSOUT vsync 输出 时钟 (阶段-排整齐 和 datack) 3.3 v cmos 138 两个都

SOGOUT 同步 在 绿色 slicer 输出 3.3 v cmos 140 相似物

电压 REFOUT 内部的 涉及 输出 (绕过 和 0.1

µ

f 至 地面) 1.25 v 126 相似物

涉及 REFIN 涉及 输入 (1.25 v

±

10%) 1.25 v

±

10% 125 相似物

clamp 电压 R

MIDSC

V red 频道 midscale clamp 电压 输出 120 相似物

R

CLAMP

V red 频道 midscale clamp 电压 输入 0.0 v 至 0.75 v 118 相似物

G

MIDSC

V 绿色 频道 midscale clamp 电压 输出 111 相似物

G

CLAMP

V 绿色 频道 midscale clamp 电压 输入 0.0 v 至 0.75 v 109 相似物

B

MIDSC

V 蓝 频道 midscale clamp 电压 输出 101 相似物

B

CLAMP

V 蓝 频道 midscale clamp 电压 输入 0.0 v 至 0.75 v 99 相似物

pll 过滤 FILT 连接 为 外部 过滤 组件 为 内部的 pll 78 相似物

电源 供应 V

D

相似物 电源 供应 3.3 v

±

10% 两个都

V

DD

输出 电源 供应 3.3 v

±

10% 两个都

PV

D

pll 电源 供应 3.3 v

±

10% 两个都

地 地面 0 v 两个都

串行 端口 SDA 串行 端口 数据 i/o 3.3 v cmos 92 两个都

(2-线 SCL 串行 端口 数据 时钟 (100 khz 最大值) 3.3 v cmos 91 两个都

串行 接口) A0 串行 端口 地址 输入 1 3.3 v cmos 90 两个都

A1 串行 端口 地址 输入 2 3.3 v cmos 89 两个都

数据 输出 red b[7:0] 端口 b/odd 输出 的 转换器 “red,” 位 7 是 这 msb 3.3 v cmos 153–160 两个都

绿色 b[7:0] 端口 b/odd 输出 的 转换器 “green,” 位 7 是 这 msb 3.3 vCMOS 13–20 两个都

蓝 b[7:0] 端口 b/odd 输出 的 转换器 “blue,” 位 7 是 这 msb 3.3 v cmos 33–40 两个都

red a[7:0] 端口 一个/甚至 输出 的 转换器 “red,” 位 7 是 这 msb 3.3 v cmos 143–150 两个都

绿色 a[7:0] 端口 一个/甚至 输出 的 转换器 “green,” 位 7 是 这 msb 3.3 v cmos 3–10 两个都

蓝 a[7:0] 端口 一个/甚至 输出 的 转换器 “blue,” 位 7 是 这 msb 3.3 v cmos 23–30 两个都

数据 时钟 DATACK 数据 输出 时钟 为 这 相似物 和 数字的 接口 3.3 v cmos 134 两个都

输出

DATACK

数据 输出 时钟 complement 为 这 相似物 接口 仅有的 3.3 v cmos 135 两个都

同步 发现 S

CDT

同步 发现 输出 3.3 v cmos 136 两个都

scan 函数 SCAN

在

输入 为 scan 函数 3.3 v cmos 129 两个都

SCAN

输出

输出 为 scan 函数 3.3 v cmos 45 两个都

SCAN

CLK

时钟 为 scan 函数 3.3 v cmos 50 两个都

非 连接 NC 这些 管脚 应当 是 left unconnected 71–73 两个都

数字的 video R

x0

+ 数字的 输入 频道 0 真实 62 数字的

数据 输入 R

x0

– 数字的 输入 频道 0 complement 63 数字的

R

x1

+ 数字的 输入 频道 1 真实 59 数字的

R

x1

– 数字的 输入 频道 1 complement 60 数字的

R

x2

+ 数字的 输入 频道 2 真实 56 数字的

R

x2

– 数字的 输入 频道 2 complement 57 数字的

数字的 video R

xc

+ 数字的 数据 时钟 真实 65 数字的

时钟 输入 R

xc

– 数字的 数据 时钟 complement 66 数字的

数据 使能 DE 数据 使能 3.3 v cmos 137 数字的

控制 位 ctl[0:3] 解码 控制 位 3.3 v cmos 46–49 数字的

R

期

R

期

sets 内部的 末端 阻抗 53 数字的