DAC8420

rev. 0

–7–

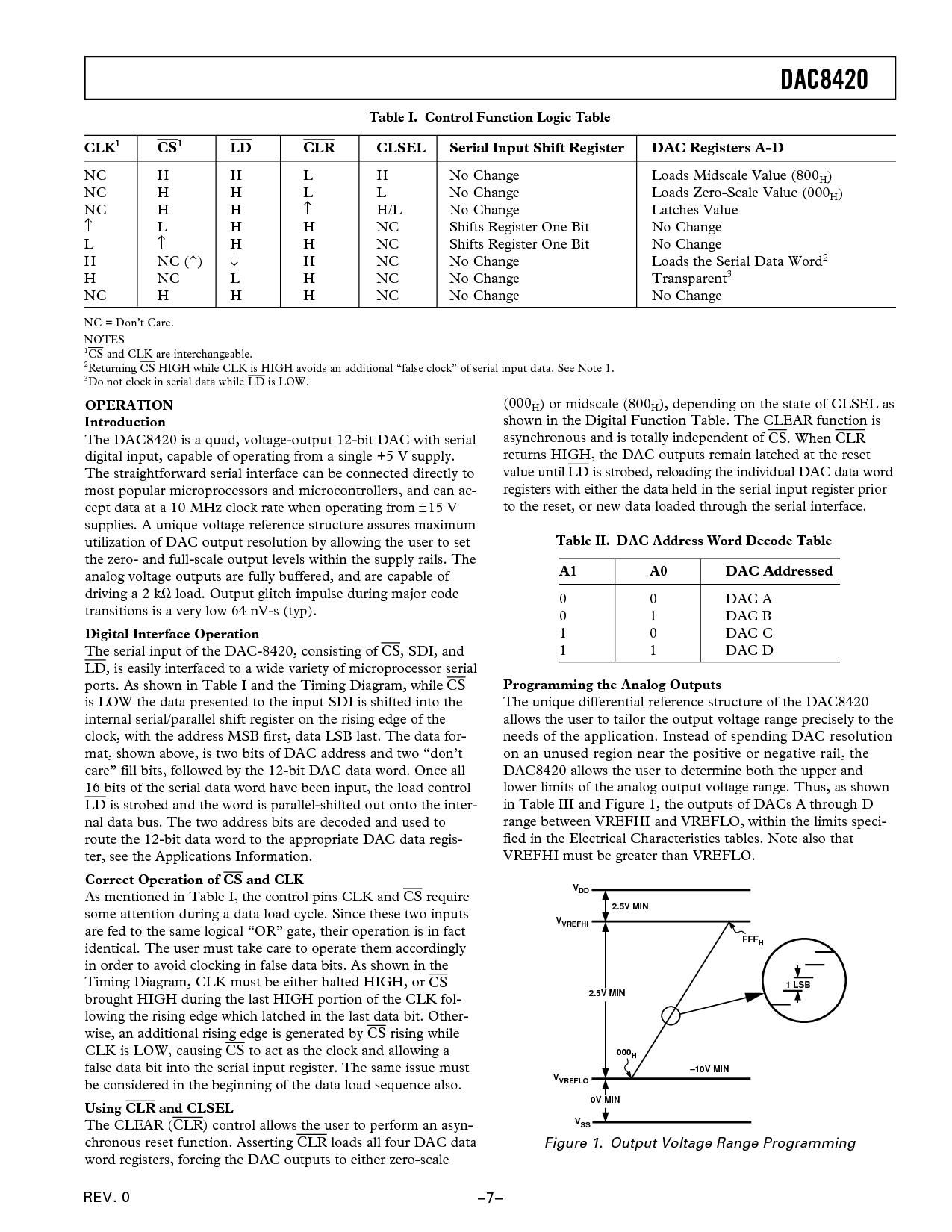

表格 i. 控制 函数 逻辑 表格

CLK

1

CS

1

LD CLR

CLSEL 串行 输入 变换 寄存器 dac 寄存器 一个-d

NC H H L H 非 改变 负载 midscale 值 (800

H

)

NC H H L L 非 改变 负载 零-规模 值 (000

H

)

NC H H

↑

h/l 非 改变 latches 值

↑

L H H NC shifts 寄存器 一个 位 非 改变

L

↑

H H NC shifts 寄存器 一个 位 非 改变

H nc (

↑

)

↓

H NC 非 改变 负载 这 串行 数据 文字

2

H NC L H NC 非 改变 Transparent

3

NC H H H NC 非 改变 非 改变

nc = don’t 小心.

注释

1

CS

和 clk 是 interchangeable.

2

Returning

CS

高 当 clk 是 高 避免 一个 额外的 “false clock” 的 串行 输入 数据. 看 便条 1.

3

做 不 时钟 在 串行 数据 当

LD

是 低.

运作

介绍

这 dac8420 是 一个 四方形, 电压-输出 12-位 dac 和 串行

数字的 输入, 有能力 的 运行 从 一个 单独的 +5 v 供应.

这 straightforward 串行 接口 能 是 连接 直接地 至

大多数 popular 微处理器 和 微控制器, 和 能 交流-

cept 数据 在 一个 10 mhz 时钟 比率 当 运行 从

±

15 v

供应. 一个 唯一的 电压 涉及 结构 assures 最大

utilization 的 dac 输出 决议 用 准许 这 用户 至 设置

这 零- 和 全部-规模 输出 水平 在里面 这 供应 围栏. 这

相似物 电压 输出 是 全部地 缓冲, 和 是 有能力 的

驱动 一个 2 k

Ω

加载. 输出 glitch impulse 在 主要的 代号

transitions 是 一个 非常 低 64 nv-s (典型值).

数字的 接口 运作

这 串行 输入 的 这 dac-8420, consisting 的

CS

, sdi, 和

LD

, 是 容易地 连接 至 一个 宽 多样性 的 微处理器 串行

端口. 作 显示 在 表格 i 和 这 定时 图解, 当

CS

是 低 这 数据 提交 至 这 输入 sdi 是 shifted 在 这

内部的 串行/并行的 变换 寄存器 在 这 rising 边缘 的 这

时钟, 和 这 地址 msb 第一, 数据 lsb last. 这 数据 为-

mat, 显示 在之上, 是 二 位 的 dac 地址 和 二 “don’t

care” fill 位, followed 用 这 12-位 dac 数据 文字. once 所有

16 位 的 这 串行 数据 文字 有 被 输入, 这 加载 控制

LD

是 strobed 和 这 文字 是 并行的-shifted 输出 面向 这 inter-

nal 数据 总线. 这 二 地址 位 是 解码 和 使用 至

route 这 12-位 数据 文字 至 这 适合的 dac 数据 regis-

ter, 看 这 产品 信息.

准确无误的 运作 的

CS

和 clk

作 提到 在 表格 i, 这 控制 管脚 clk 和

CS

需要

一些 注意 在 一个 数据 加载 循环. 自从 这些 二 输入

是 喂养 至 这 一样 logical “or” 门, 它们的 运作 是 在 事实

完全同样的. 这 用户 必须 引领 小心 至 运作 它们 accordingly

在 顺序 至 避免 clocking 在 false 数据 位. 作 显示 在 这

定时 图解, clk 必须 是 也 halted 高, 或者

CS

brought 高 在 这 last 高 portion 的 这 clk fol-

lowing 这 rising 边缘 这个 latched 在 这 last 数据 位. 其它-

wise, 一个 额外的 rising 边缘 是 发生 用

CS

rising 当

clk 是 低, 造成

CS

至 act 作 这 时钟 和 准许 一个

false 数据 位 在 这 串行 输入 寄存器. 这 一样 公布 必须

是 考虑 在 这 beginning 的 这 数据 加载 sequence 也.

使用

CLR

和 clsel

这 clear (

CLR

) 控制 准许 这 用户 至 执行 一个 asyn-

chronous 重置 函数. asserting

CLR

负载 所有 四 dac 数据

文字 寄存器, forcing 这 dac 输出 至 也 零-规模

(000

H

) 或者 midscale (800

H

), 取决于 在 这 状态 的 clsel 作

显示 在 这 数字的 函数 表格. 这 clear 函数 是

异步的 和 是 totally 独立 的

CS

. 当

CLR

returns 高, 这 dac 输出 仍然是 latched 在 这 重置

值 直到

LD

是 strobed, reloading 这 单独的 dac 数据 文字

寄存器 和 也 这 数据 使保持 在这 串行 输入 register prior

至 这 重置, 或者 新 数据 承载 通过 这 串行 接口.

表格 ii. dac 地址 文字 decode 表格

A1 A0 dac addressed

0 0 dac 一个

0 1 dac b

1 0 dac c

1 1 dac d

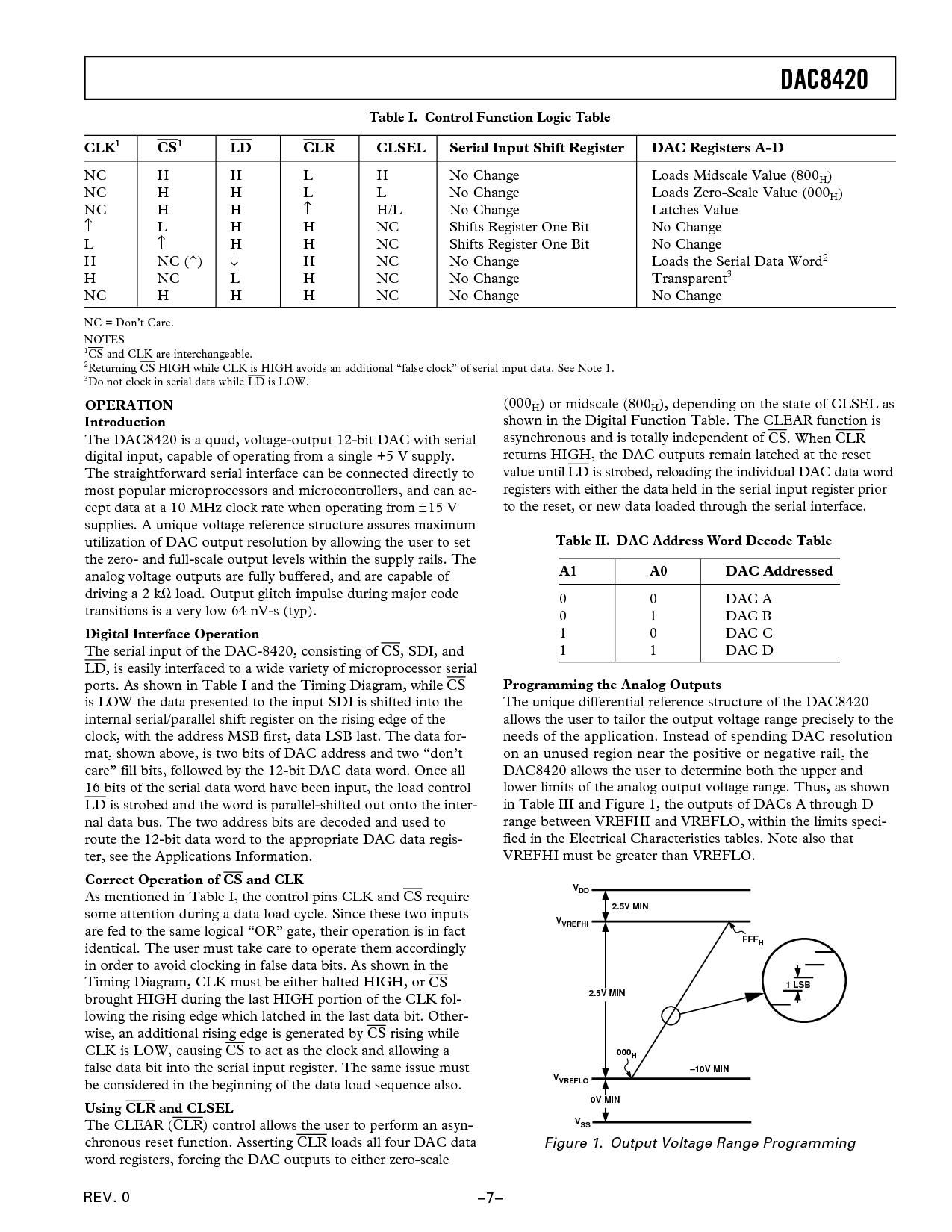

程序编制 这 相似物 输出

这 唯一的 差别的 涉及 结构 的 这 dac8420

准许 这 用户 至 tailor 这 输出 电压 范围 precisely 至 这

needs 的 这 应用. instead 的 spending dac 决议

在 一个 unused 区域 near 这 积极的 或者 负的 栏杆, 这

dac8420 准许 这 用户 至 决定 两个都 这 upper 和

更小的 限制 的 这 相似物 输出 电压 范围. 因此, 作 显示

在 表格 iii 和 图示 1, 这 输出 的 dacs 一个 通过 d

范围 在 vrefhi 和 vreflo, 在里面 这 限制 speci-

fied 在 这 电的 特性 tables. 便条 也 那

vrefhi 必须 是 更好 比 vreflo.

1 lsb

FFF

H

000

H

2.5v 最小值

2.5v 最小值

0v 最小值

V

DD

V

VREFHI

V

VREFLO

V

SS

–10v 最小值

图示 1. 输出 电压 范围 程序编制