数字的 接口

(持续)

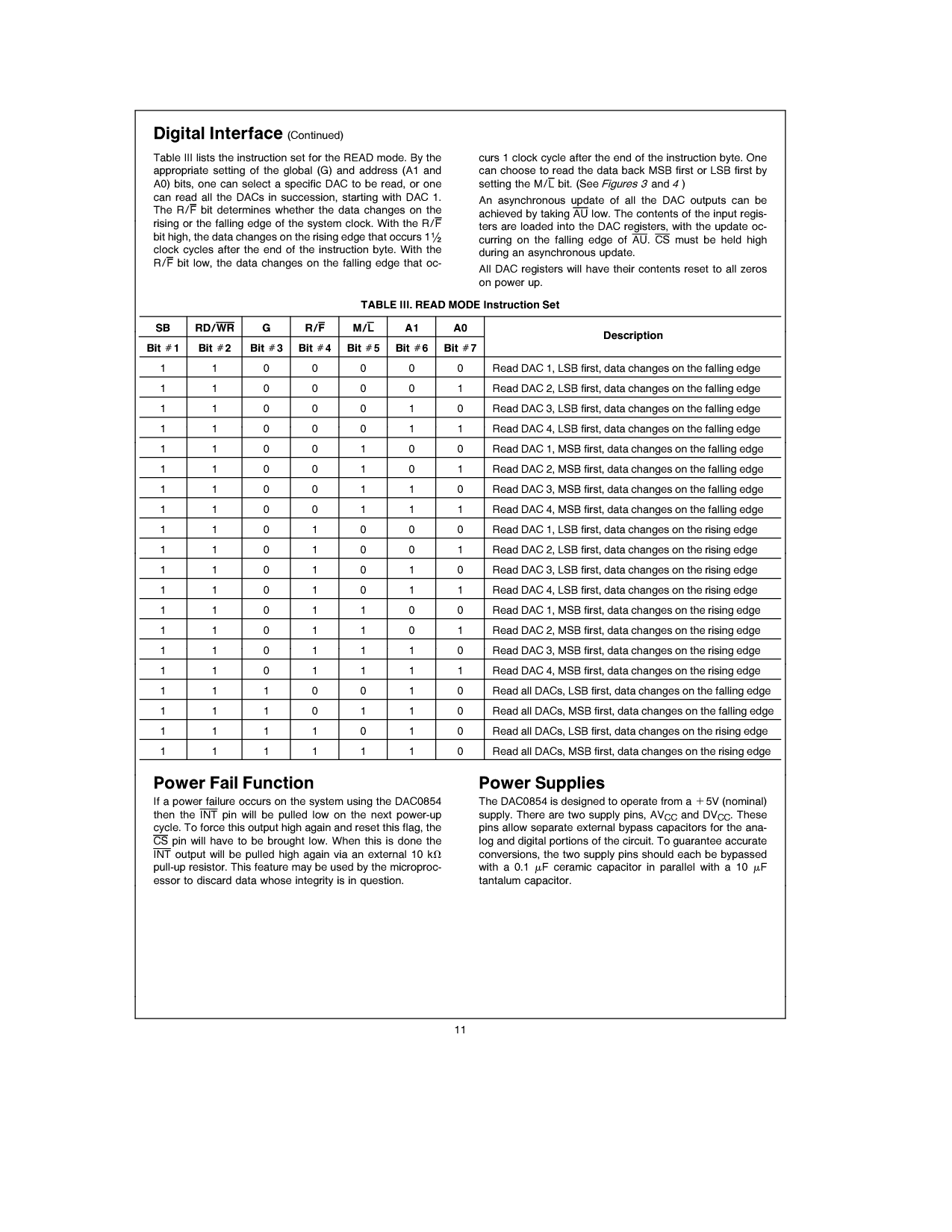

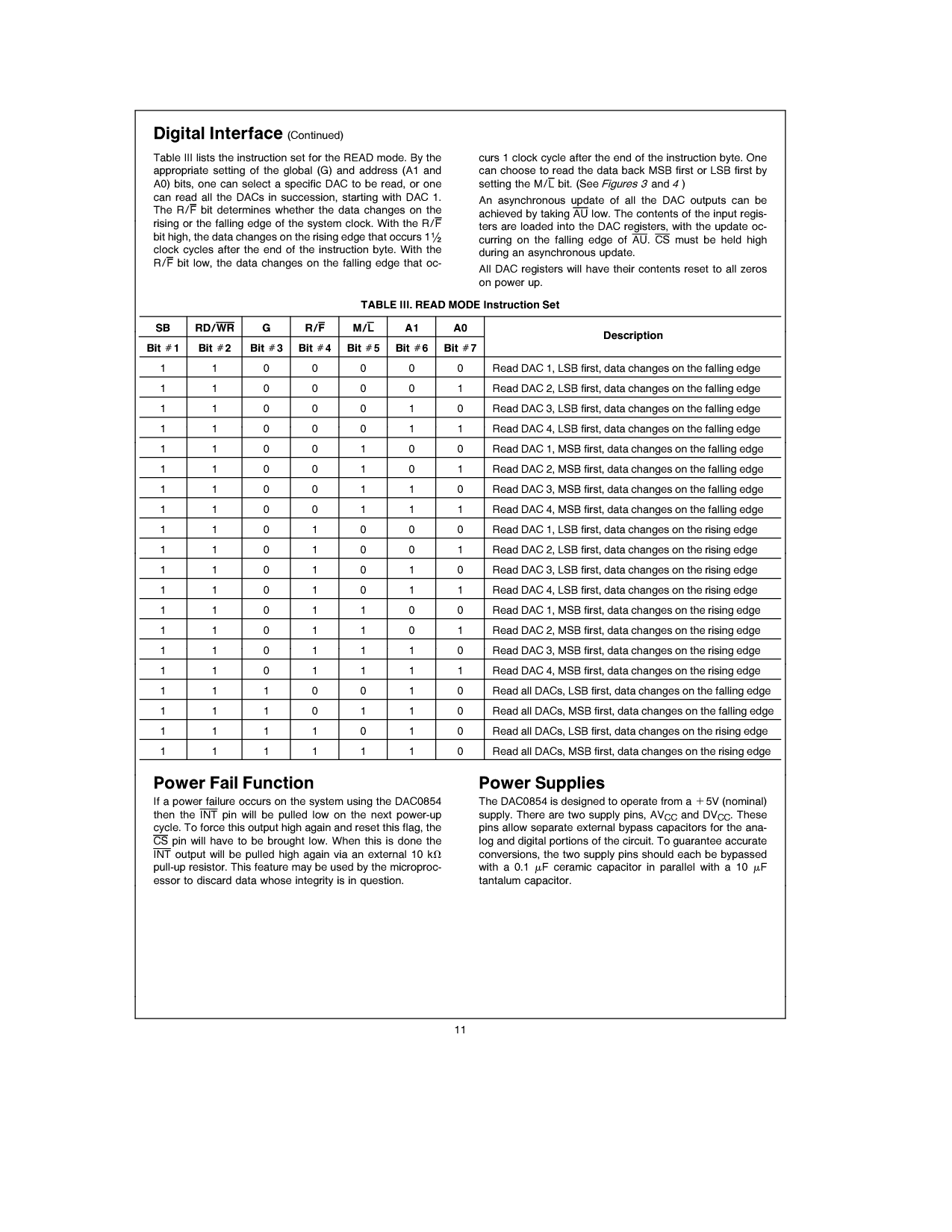

表格 III lists 这 操作指南 设置 为 这 读 mode 用 这

适合的 设置 的 这 global (g) 和 地址 (a1 和

a0) bits 一个 能 选择 一个 明确的 DAC 至 是 read 或者 一个

能 读 所有 这 DACs 在 succession 开始 和 DAC 1

这 RF

位 确定 whether 这 数据 改变 在 这

rising 或者 这 下落 边缘 的 这 系统 clock 和 这 RF

位 high 这 数据 改变 在 这 rising 边缘 那 occurs 1

时钟 循环 之后 这 终止 的 这 操作指南 byte 和 这

RF

位 low 这 数据 改变 在 这 下落 边缘 那 oc-

curs 1 时钟 循环 之后 这 终止 的 这 操作指南 byte 一个

能 choose 至 读 这 数据 后面的 MSB 第一 或者 LSB 第一 用

设置 这 ML

bit (看

计算数量 3

和

4

)

一个 异步的 更新 的 所有 这 DAC 输出 能 是

达到 用 带去 AU

low 这 内容 的 这 输入 regis-

ters 是 承载 在 这 DAC registers 和 这 更新 oc-

curring 在 这 下落 边缘 的 AU

CS必须 是 使保持 高

在 一个 异步的 update

所有 DAC 寄存器 将 有 它们的 内容 重置 至 所有 zeros

在 电源 up

表格 III 读 模式 操作指南 设置

SB RDWR G RF ML A1 A0

描述

位

1 位

2 位

3 位

4 位

5 位

6 位

7

1 1 0 0 0 0 0 读 DAC 1 LSB first 数据 改变 在 这 下落 边缘

1 1 0 0 0 0 1 读 DAC 2 LSB first 数据 改变 在 这 下落 边缘

1 1 0 0 0 1 0 读 DAC 3 LSB first 数据 改变 在 这 下落 边缘

1 1 0 0 0 1 1 读 DAC 4 LSB first 数据 改变 在 这 下落 边缘

1 1 0 0 1 0 0 读 DAC 1 MSB first 数据 改变 在 这 下落 边缘

1 1 0 0 1 0 1 读 DAC 2 MSB first 数据 改变 在 这 下落 边缘

1 1 0 0 1 1 0 读 DAC 3 MSB first 数据 改变 在 这 下落 边缘

1 1 0 0 1 1 1 读 DAC 4 MSB first 数据 改变 在 这 下落 边缘

1 1 0 1 0 0 0 读 DAC 1 LSB first 数据 改变 在 这 rising 边缘

1 1 0 1 0 0 1 读 DAC 2 LSB first 数据 改变 在 这 rising 边缘

1 1 0 1 0 1 0 读 DAC 3 LSB first 数据 改变 在 这 rising 边缘

1 1 0 1 0 1 1 读 DAC 4 LSB first 数据 改变 在 这 rising 边缘

1 1 0 1 1 0 0 读 DAC 1 MSB first 数据 改变 在 这 rising 边缘

1 1 0 1 1 0 1 读 DAC 2 MSB first 数据 改变 在 这 rising 边缘

1 1 0 1 1 1 0 读 DAC 3 MSB first 数据 改变 在 这 rising 边缘

1 1 0 1 1 1 1 读 DAC 4 MSB first 数据 改变 在 这 rising 边缘

1 1 1 0 0 1 0 读 所有 DACs LSB first 数据 改变 在 这 下落 边缘

1 1 1 0 1 1 0 读 所有 DACs MSB first 数据 改变 在 这 下落 边缘

1 1 1 1 0 1 0 读 所有 DACs LSB first 数据 改变 在 这 rising 边缘

1 1 1 1 1 1 0 读 所有 DACs MSB first 数据 改变 在 这 rising 边缘

电源 失败 函数

如果 一个 电源 失败 occurs 在 这 系统 使用 这 DAC0854

然后 这 INT

管脚 将 是 牵引的 低 在 这 next 电源-向上

cycle 至 强迫 这个 输出 高 又一次 和 重置 这个 flag 这

CS

管脚 将 有 至 是 brought low 当 这个 是 完毕 这

INT

输出 将 是 牵引的 高 又一次 通过 一个 外部 10 k

X

拉-向上 resistor 这个 特性 将 是 使用 用 这 microproc-

essor 至 discard 数据 谁的 integrity 是 在 question

电源 供应

这 DAC0854 是 设计 至 运作 从 一个

一个

5V (名义上的)

supply 那里 是 二 供应 pins AV

CC

和 DV

CC

这些

管脚 准许 独立的 外部 绕过 电容 为 这 ana-

log 和 数字的 portions 的 这 circuit 至 保证 精确

conversions 这 二 供应 管脚 应当 各自 是 绕过

和 一个 01

m

F 陶瓷的 电容 在 并行的 和 一个 10

m

F

tantalum capacitor

11