www.德州仪器.com

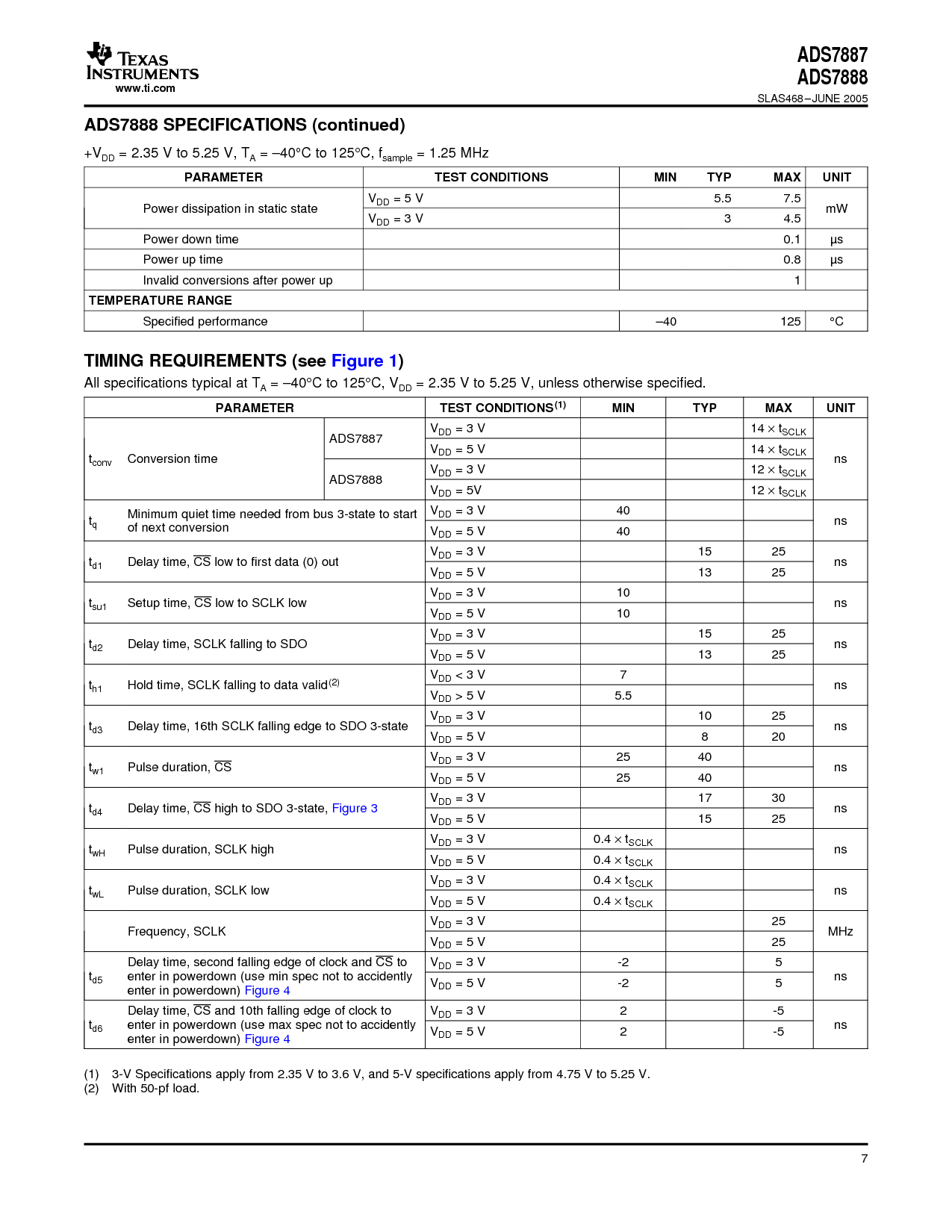

timingrequirements(看Figure1)

ADS7887

ADS7888

SLAS468–JUNE2005

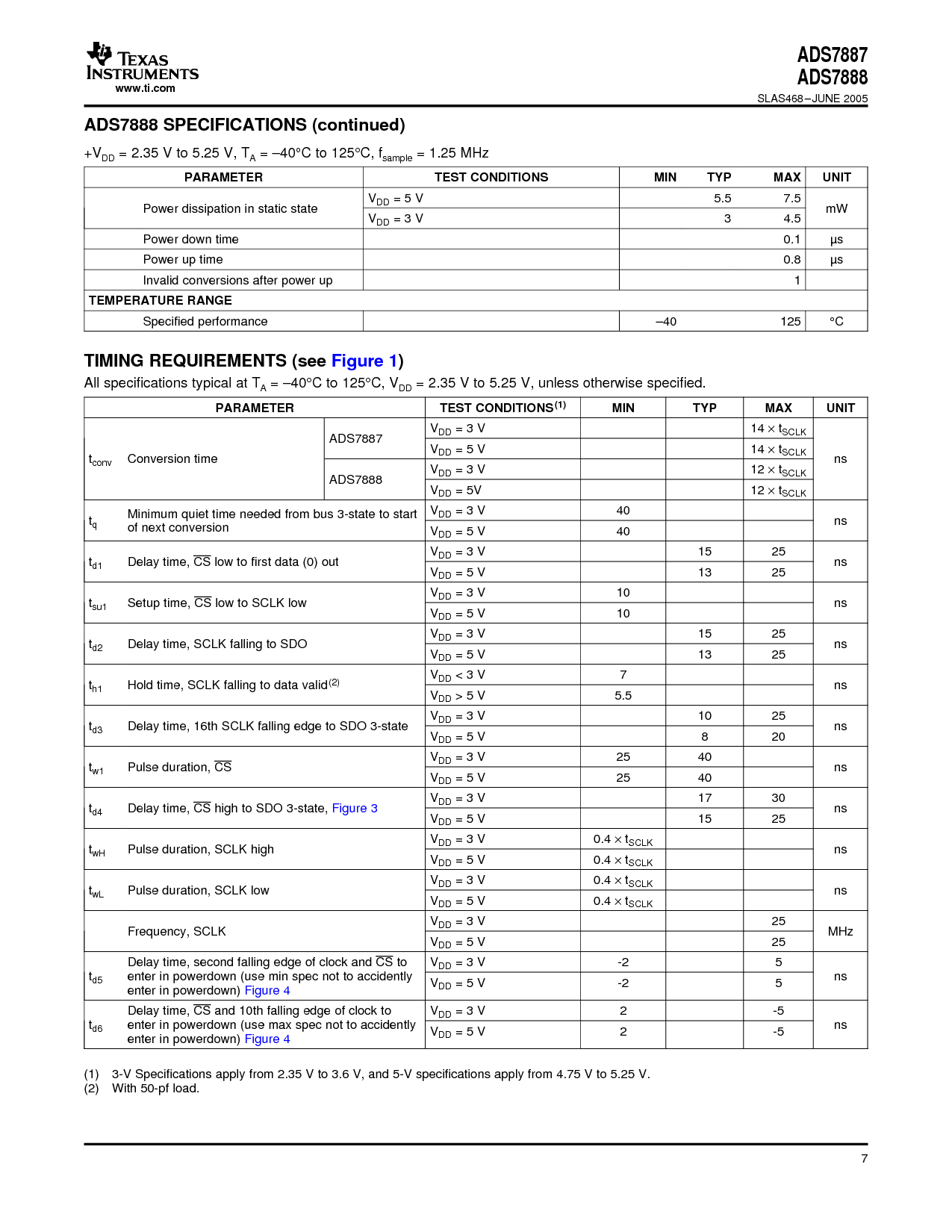

ads7888specifications(持续)

+V

DD

=2.35vto5.25v,t

一个

=–40

°

Cto125

°

c,f

样本

=1.25mhz

PARAMETERTESTCONDITIONSMINTYPMAXUNIT

V

DD

=5v5.57.5

PowerdissipationinstaticstatemW

V

DD

=3v34.5

powerdowntime0.1µs

poweruptime0.8µs

Invalidconversionsafterpowerup1

TEMPERATURERANGE

Specifiedperformance–40125

°

C

AllspecificationstypicalatT

一个

=–40

°

Cto125

°

c,v

DD

=2.35vto5.25v,unlessotherwisespecified.

PARAMETERTESTCONDITIONS

(1)

MINTYPMAXUNIT

V

DD

=3V14

×

t

SCLK

ADS7887

V

DD

=5V14

×

t

SCLK

t

conv

Conversiontimens

V

DD

=3V12

×

t

SCLK

ADS7888

V

DD

=5V12

×

t

SCLK

V

DD

=3V40

minimumquiettimeneededfrombus3-statetostart

t

q

ns

ofnextconversion

V

DD

=5V40

V

DD

=3V1525

t

d1

delaytime,cslowtofirstdata(0)outns

V

DD

=5V1325

V

DD

=3V10

t

su1

setuptime,cslowtosclklowns

V

DD

=5V10

V

DD

=3V1525

t

d2

delaytime,sclkfallingtosdons

V

DD

=5V1325

V

DD

<3v7

t

h1

holdtime,sclkfallingtodatavalid

(2)

ns

V

DD

>5v5.5

V

DD

=3V1025

t

d3

delaytime,16thsclkfallingedgetosdo3-statens

V

DD

=5V820

V

DD

=3V2540

t

w1

pulseduration,csns

V

DD

=5V2540

V

DD

=3V1730

t

d4

delaytime,cshightosdo3-状态,Figure3ns

V

DD

=5V1525

V

DD

=3v0.4

×

t

SCLK

t

wH

pulseduration,sclkhighns

V

DD

=5v0.4

×

t

SCLK

V

DD

=3v0.4

×

t

SCLK

t

wL

pulseduration,sclklowns

V

DD

=5v0.4

×

t

SCLK

V

DD

=3V25

频率,sclkmhz

V

DD

=5V25

delaytime,secondfallingedgeofclockandcstov

DD

=3v-25

t

d5

enterinpowerdown(useminspecnottoaccidentlyns

V

DD

=5v-25

enterinpowerdown)Figure4

delaytime,csand10thfallingedgeofclocktov

DD

=3v2-5

t

d6

enterinpowerdown(usemaxspecnottoaccidentlyns

V

DD

=5v2-5

enterinpowerdown)Figure4

(1)3-vspecificationsapplyfrom2.35vto3.6v,and5-vspecificationsapplyfrom4.75vto5.25v.

(2)with50-pfload.

7