www.德州仪器.com

ADS7888NORMALOPERATION

1

2 4

5

6

12

15

CS

SCLK

SDO

0

0 0

D7 D6

D1

D0

11

0

0

16

t

d1

t

d2

t

h1

t

conv

1/throughput

t

q

t

d3

t

w1

b

t

su1

一个

0

1

2 4

5

6

12

CS

SCLK

SDO

0

0 0

D7 D6

D1

D0

11

t

d1

t

d2

t

h1

t

conv

1/throughput

t

q

t

h1

t

w1

b

t

su1

一个

t

d4

POWERDOWNMODE

ADS7887

ADS7888

SLAS468–JUNE2005

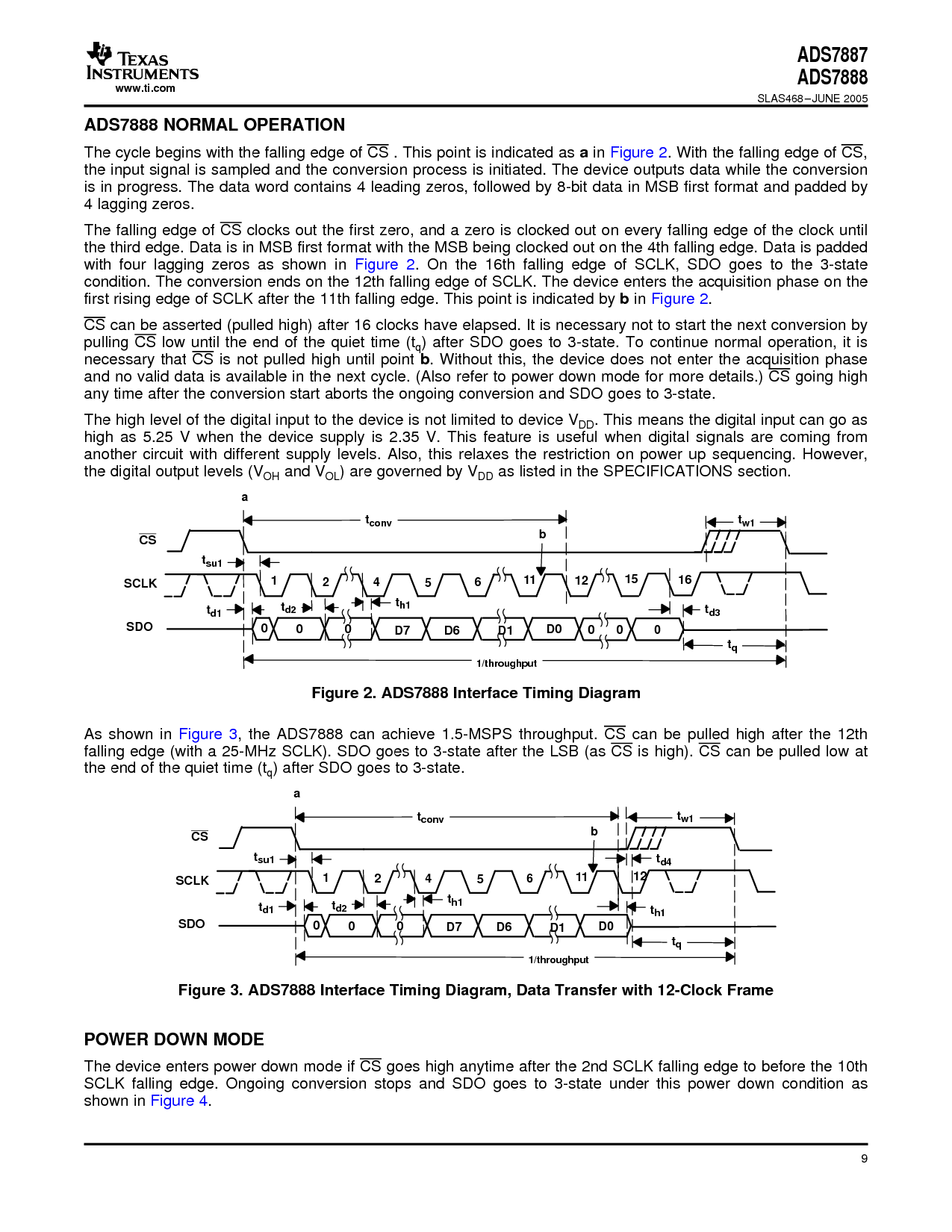

thecyclebeginswiththefallingedgeofcs.thispointisindicatedas

一个

在Figure2.withthefallingedgeofcs,

theinputsignalissampledandtheconversionprocessisinitiated.thedeviceoutputsdatawhiletheconversion

isinprogress.thedatawordcontains4leadingzeros,followedby8-bitdatainmsbfirstformatandpaddedby

4laggingzeros.

thefallingedgeofcsclocksoutthefirstzero,andazeroisclockedoutoneveryfallingedgeoftheclockuntil

thethirdedge.dataisinmsbfirstformatwiththemsbbeingclockedoutonthe4thfallingedge.dataispadded

withfourlaggingzerosasshowninFigure2.onthe16thfallingedgeofsclk,sdogoestothe3-状态

情况.theconversionendsonthe12thfallingedgeofsclk.thedeviceenterstheacquisitionphaseonthe

firstrisingedgeofsclkafterthe11thfallingedge.thispointisindicatedby

b

在Figure2.

cscanbeasserted(pulledhigh)after16clockshaveelapsed.itisnecessarynottostartthenextconversionby

pullingcslowuntiltheendofthequiettime(t

q

)aftersdogoesto3-状态.tocontinuenormaloperation,itis

necessarythatCSisnotpulledhighuntilpoint

b

.withoutthis,thedevicedoesnotentertheacquisitionphase

andnovaliddataisavailableinthenextcycle.(alsorefertopowerdownmodeformoredetails.)csgoinghigh

anytimeaftertheconversionstartabortstheongoingconversionandsdogoesto3-状态.

ThehighlevelofthedigitalinputtothedeviceisnotlimitedtodeviceV

DD

.thismeansthedigitalinputcangoas

highas5.25vwhenthedevicesupplyis2.35v.thisfeatureisusefulwhendigitalsignalsarecomingfrom

anothercircuitwithdifferentsupplylevels.也,thisrelaxestherestrictiononpowerupsequencing.不管怎样,

thedigitaloutputlevels(v

OH

andV

OL

)aregovernedbyv

DD

aslistedinthespecificationssection.

figure2.ads7888interfacetimingdiagram

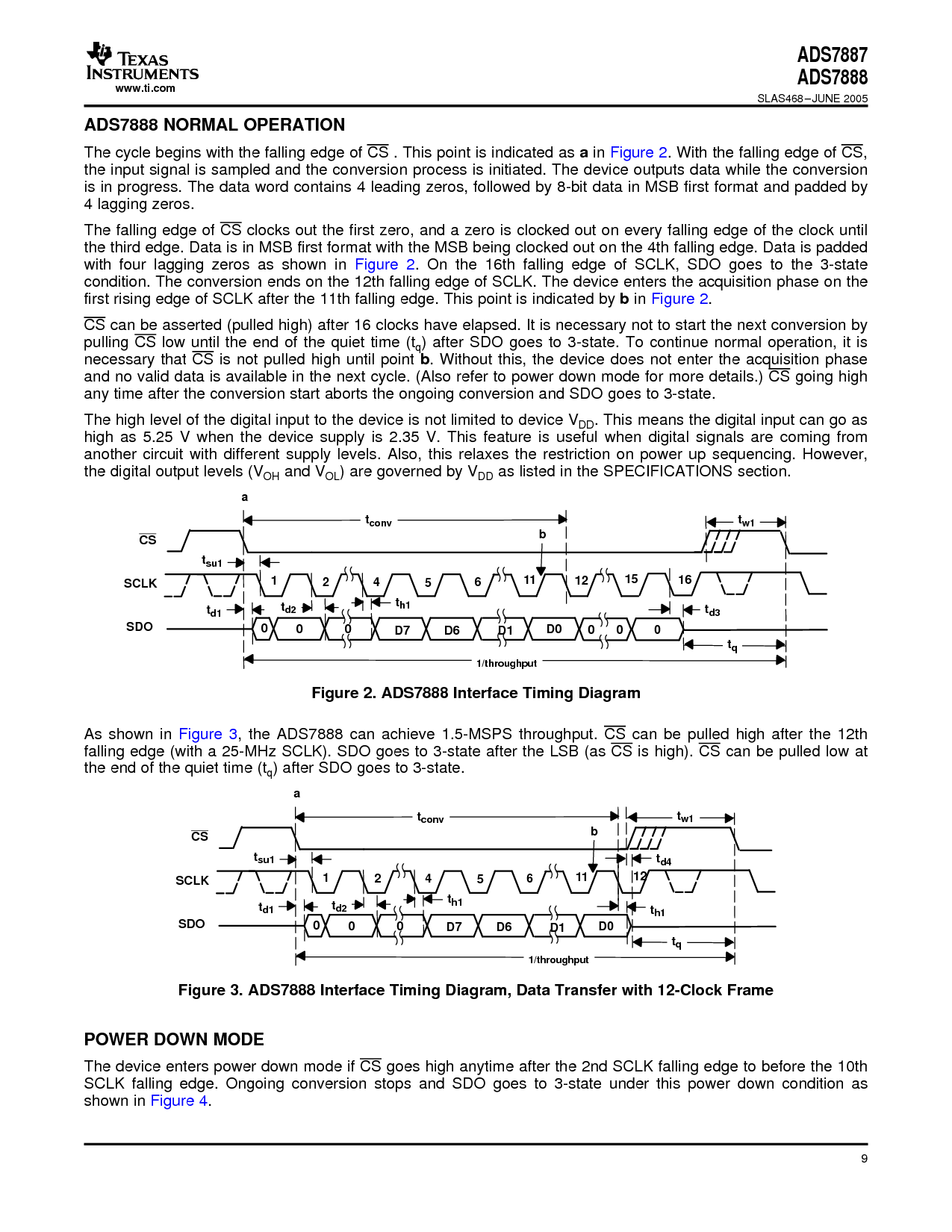

AsshowninFigure3,theads7888canachieve1.5-mspsthroughput.cscanbepulledhighafterthe12th

fallingedge(witha25-mhzsclk).sdogoesto3-stateafterthelsb(ascsishigh).cscanbepulledlowat

theendofthequiettime(t

q

)aftersdogoesto3-状态.

figure3.ads7888interfacetimingdiagram,datatransferwith12-clockframe

ThedeviceenterspowerdownmodeifCSgoeshighanytimeafterthe2ndSCLKfallingedgetobeforethe10th

sclkfallingedge.ongoingconversionstopsandsdogoesto3-stateunderthispowerdownconditionas

showninFigure4.

9