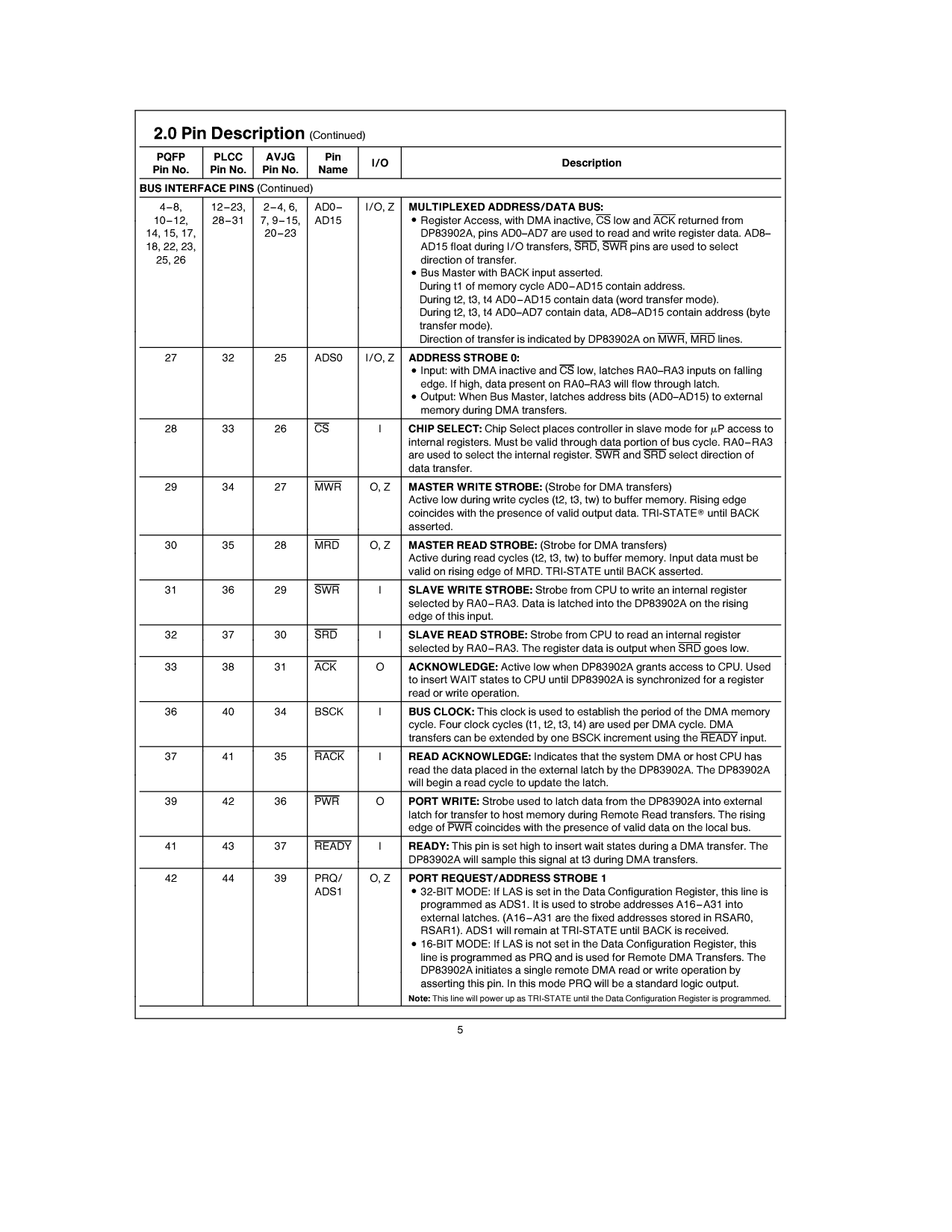

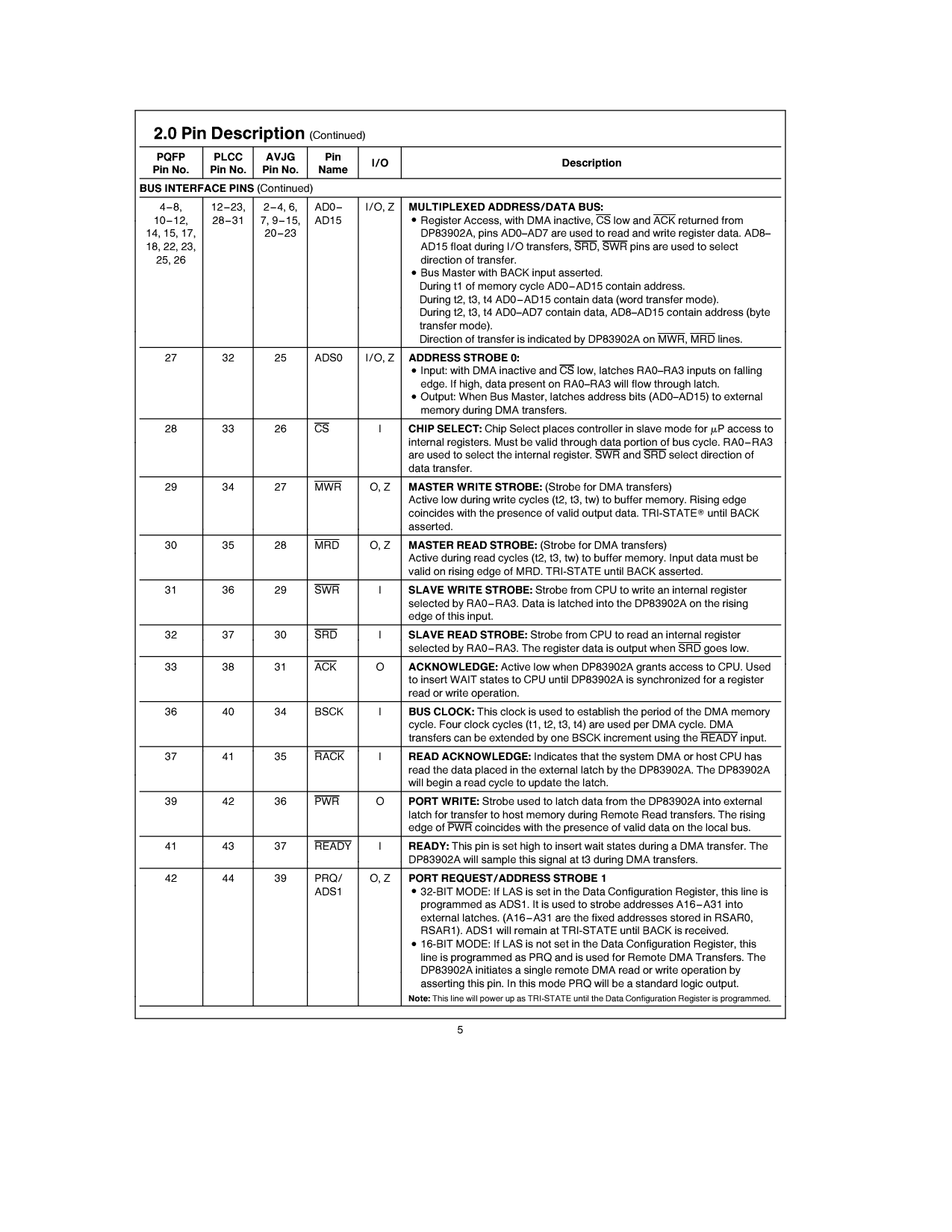

20 管脚 描述

(持续)

PQFP PLCC AVJG 管脚

IO 描述

管脚 No 管脚 No 管脚 No 名字

总线 接口 管脚

(持续)

4–8 12–23 2–4 6 AD0– IO Z

多路复用 ADDRESSDATA BUS

10–12 28–31 7 9–15 AD15

寄存器 Access 和 DMA inactive CS 低 和 ACK returned 从

14 15 17 20–23 DP83902A 管脚 AD0–AD7 是 使用 至 读 和 写 寄存器 data AD8–

18 22 23 AD15 float 在 IO transfers SRD

SWR 管脚 是 使用 至 选择

25 26 方向 的 transfer

总线 主控 和 后面的 输入 asserted

在 t1 的 记忆 循环 AD0–AD15 包含 address

在 t2 t3 t4 AD0–AD15 包含 数据 (文字 转移 模式)

在 t2 t3 t4 AD0–AD7 包含 data AD8–AD15 包含 地址 (字节

转移 模式)

方向 的 转移 是 表明 用 DP83902A 在 MWR

MRD lines

27 32 25 ADS0 IO Z

地址 STROBE 0

Input 和 DMA inactive 和 CS low latches RA0–RA3 输入 在 下落

edge 如果 high 数据 呈现 在 RA0–RA3 将 流动 通过 latch

Output 当 总线 Master latches 地址 位 (ad0–ad15) 至 外部

记忆 在 DMA transfers

28 33 26 CS I

碎片 SELECT

碎片 选择 places 控制 在 从动装置 模式 为

m

P 进入 至

内部的 registers 必须 是 有效的 通过 数据 portion 的 总线 cycle RA0–RA3

是 使用 至 选择 这 内部的 register SWR

和 SRD 选择 方向 的

数据 transfer

29 34 27 MWR O Z

主控 写 STROBE

(strobe 为 DMA transfers)

起作用的 低 在 写 循环 (t2 t3 tw) 至 缓存区 memory Rising 边缘

coincides 和 这 存在 的 有效的 输出 data 触发-状态

直到 后面的

asserted

30 35 28 MRD O Z

主控 读 STROBE

(strobe 为 DMA transfers)

起作用的 在 读 循环 (t2 t3 tw) 至 缓存区 memory 输入 数据 必须 是

有效的 在 rising 边缘 的 MRD 触发-状态 直到 后面的 asserted

31 36 29 SWR I

从动装置 写 STROBE

Strobe 从 CPU 至 写 一个 内部的 寄存器

选择 用 RA0–RA3 数据 是 latched 在 这 DP83902A 在 这 rising

边缘 的 这个 input

32 37 30 SRD I

从动装置 读 STROBE

Strobe 从 CPU 至 读 一个 内部的 寄存器

选择 用 RA0–RA3 这 寄存器 数据 是 输出 当 SRD 变得 low

33 38 31 ACK O

ACKNOWLEDGE

起作用的 低 当 DP83902A grants 进入 至 CPU 使用

至 insert WAIT states 至 CPU 直到 DP83902A 是 同步 为 一个 寄存器

读 或者 写 operation

36 40 34 BSCK I

总线 CLOCK

这个 时钟 是 使用 至 establish 这 时期 的 这 DMA 记忆

cycle 四 时钟 循环 (t1 t2 t3 t4) 是 使用 每 DMA cycle DMA

transfers 能 是 扩展 用 一个 BSCK increment 使用 这 准备好

input

37 41 35 RACK I

读 ACKNOWLEDGE

Indicates 那 这 系统 DMA 或者 host CPU 有

读 这 数据 放置 在 这 外部 获得 用 这 DP83902A 这 DP83902A

将 begin 一个 读 循环 至 更新 这 latch

39 42 36 PWR O

端口 WRITE

Strobe 使用 至 获得 数据 从 这 DP83902A 在 外部

获得 为 转移 至 host 记忆 在 偏远的 读 transfers 这 rising

边缘 的 PWR

coincides 和 这 存在 的 有效的 数据 在 这 local bus

41 43 37 准备好 I

READY

这个 管脚 是 设置 高 至 insert wait states 在 一个 DMA transfer 这

DP83902A 将 样本 这个 信号 在 t3 在 DMA transfers

42 44 39 PRQ O Z

端口 REQUESTADDRESS STROBE 1

ADS1

32-位 MODE 如果 LAS 是 设置 在 这 数据 配置 Register 这个 线条 是

编写程序 作 ADS1 它 是 使用 至 strobe 地址 A16–A31 在

外部 latches (a16–A31 是 这 fixed 地址 贮存 在 RSAR0

rsar1) ADS1 将 仍然是 在 触发-状态 直到 后面的 是 received

16-位 MODE 如果 LAS 是 不 设置 在 这 数据 配置 Register 这个

线条 是 编写程序 作 PRQ 和 是 使用 为 偏远的 DMA Transfers 这

DP83902A initiates 一个 单独的 偏远的 DMA 读 或者 写 运作 用

asserting 这个 pin 在 这个 模式 PRQ 将 是 一个 标准 逻辑 output

Note

这个 线条 将 电源 向上 作 触发-状态 直到 这 数据 配置 寄存器 是 programmed

5