1 的 6 071700

特性

所有-硅 时间 延迟

二 可编程序的 输出 从 一个 单独的

输入 生产 输出-至-输出 延迟

在 9 和 84 ns 取决于 在 设备

类型

可编程序的 通过 四 输入 管脚

可编程序的 increments 的 3 至 5 ns 和 一个

最小 的 9 ns 和 一个 最大 的 84 ns

输出 脉冲波 是 一个 再版 的 输入 脉冲波

之后

延迟 和 两个都 leading 和 trailing 边缘

精度

标准 16-管脚 插件 或者 表面 挂载 16-管脚

SOIC

自动-insertable

低-电源 cmos 设计 是 ttl-兼容

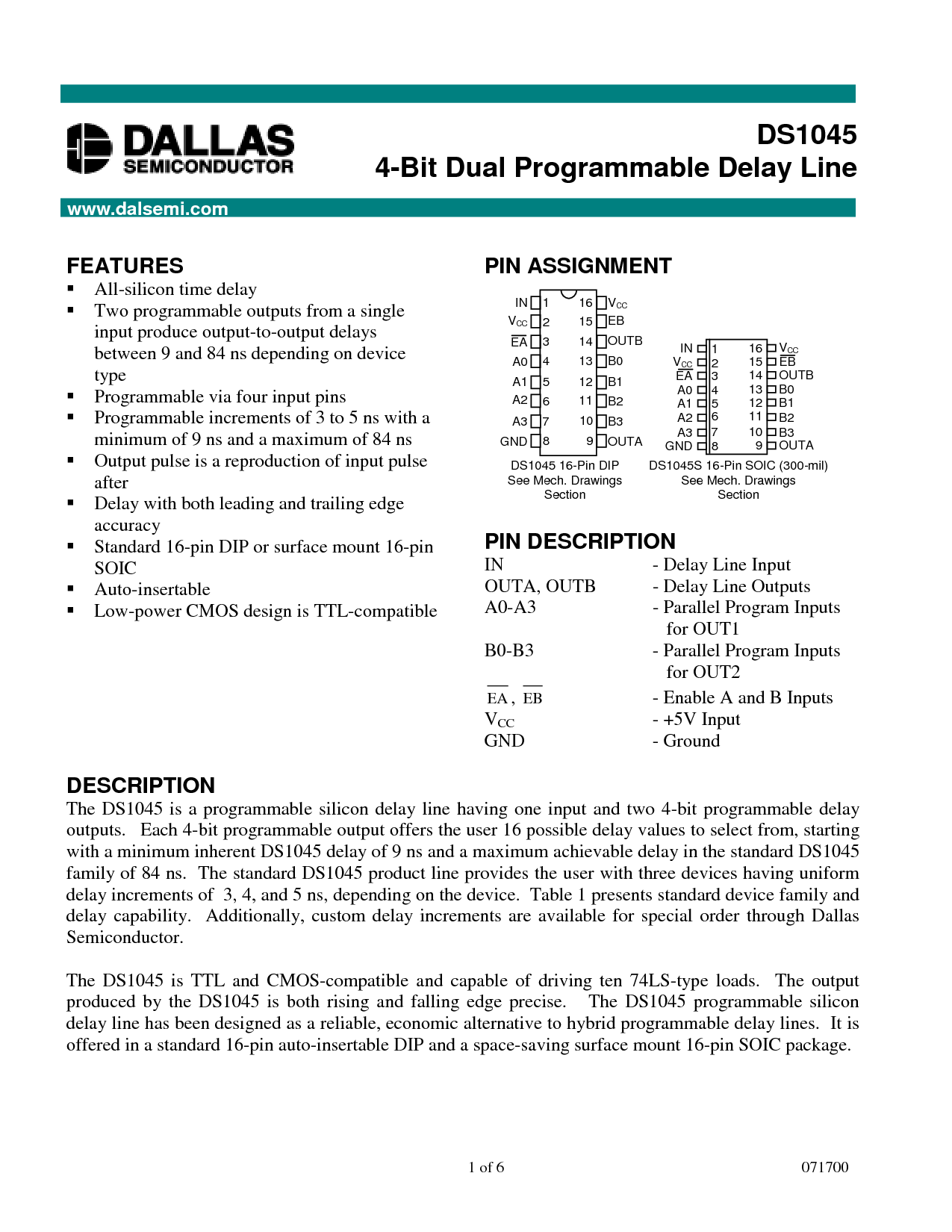

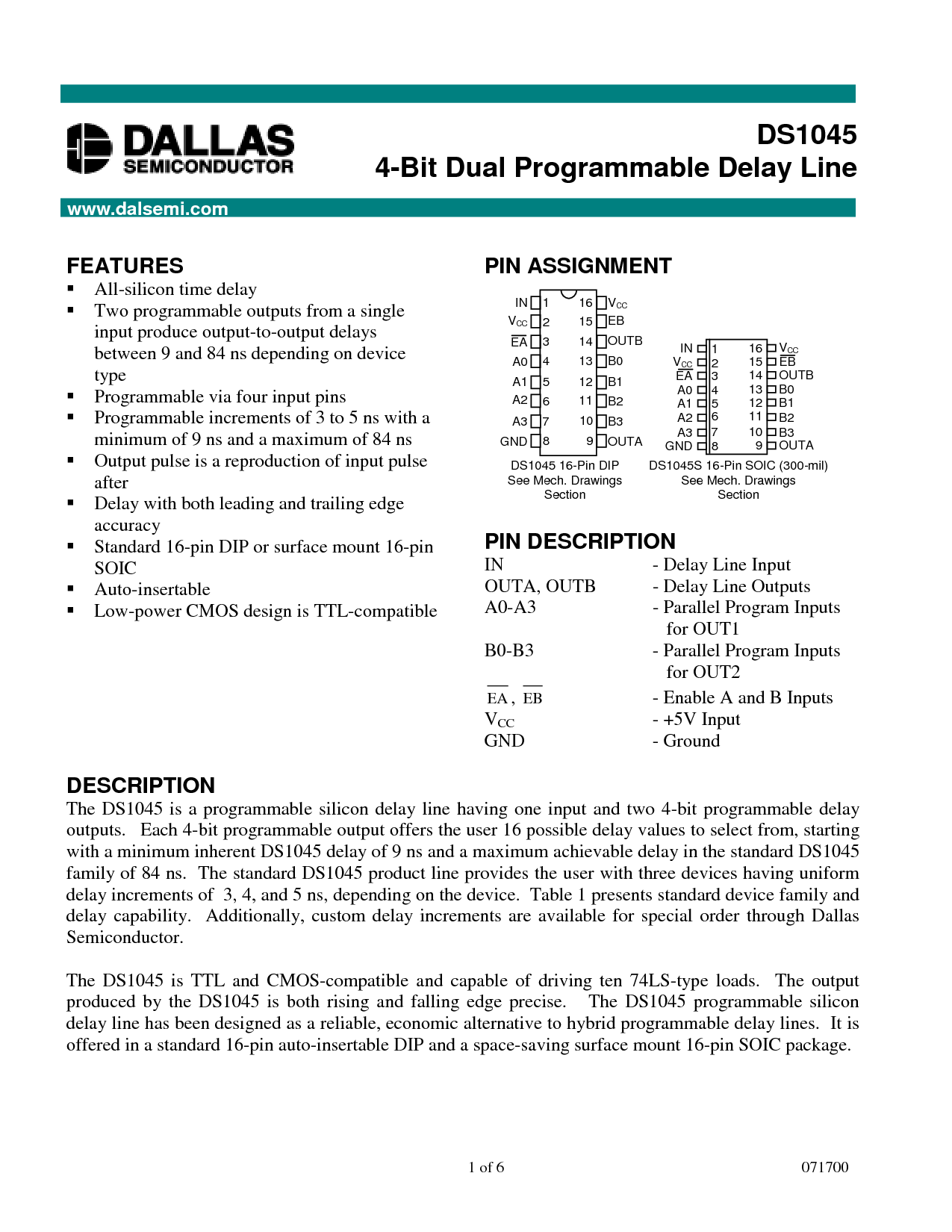

管脚 分派

管脚 描述

在 - 延迟 线条 输入

outa, outb - 延迟 线条 输出

a0-a3 - 并行的 程序 输入

为 out1

b0-b3 - 并行的 程序 输入

为 out2

EA

,

EB

- 使能 一个 和 b 输入

V

CC

- +5v 输入

地 - 地面

描述

这 ds1045 是 一个 可编程序的 硅 延迟 线条 having 一个 输入 和 二 4-位 可编程序的 延迟

输出. 各自 4-位 可编程序的 输出 提供 这 用户 16 可能 延迟 值 至 选择 从, 开始

和 一个 最小 固有的 ds1045 延迟 的 9 ns 和 一个 最大 achievable 延迟 在 这 标准 ds1045

家族 的 84 ns. 这 标准 ds1045 产品 线条 提供 这 用户 和 三 设备 having uniform

延迟 increments 的 3, 4, 和 5 ns, 取决于 在 这 设备. 表格 1 presents 标准 设备 家族 和

延迟 能力. additionally, custom 延迟 increments 是 有 为 特定的 顺序 通过 达拉斯市

半导体.

这 ds1045 是 ttl 和 cmos-兼容 和 有能力 的 驱动 ten 74ls-类型 负载. 这 输出

生产 用 这 ds1045 是 两个都 rising 和 下落 边缘 准确的. 这 ds1045 可编程序的 硅

延迟 线条 有 被 设计 作 一个 可依靠的, economic alternative 至 混合的 可编程序的 延迟 线条. 它 是

offered 在 一个 标准 16-管脚 自动-insertable 插件 和 一个 空间-节省 表面 挂载 16-管脚 soic package.

DS1045

4-位 双 可编程序的 延迟 线条

www.dalsemi.com

在

V

CC

EA

A0

A1

A2

A3

地

V

CC

EB

OUTB

B0

B1

B2

B3

OUTA

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

在

V

CC

16

1

V

CC

EA

A0

A1

A2

A3

地

EB

OUTB

B0

B1

B2

B3

OUTA

2

3

4

5

6

7

8

15

14

13

12

11

10

9

ds1045 16-管脚 插件

看 mech. 绘画

部分

ds1045s 16-管脚 soic (300-mil)

看 mech. 绘画

部分