DS21372

6 的 21

2. 并行的 控制 接口

这 ds21372 是 控制 通过 一个 多路复用 bi-directional 地址/数据 总线 用 一个 外部

微控制器 或者 微处理器. 这 ds21372 能 运作 和 也 intel 或者 motorola 总线 定时

配置. 如果 这 bts 管脚 是 系 低, intel 定时 将 是 选择; 如果 系 高, motorola 定时 将

是 选择. 所有 motorola 总线 信号 是 列表 在 parenthesis (). 看 这 定时 图解 在 这 一个.c.

电的 特性 为 更多 详细信息. 这 多路复用 总线 在 这 ds21372 saves 管脚 因为 这

地址 信息 和 数据 信息 share 这 一样 信号 paths. 这 地址 是 提交 至 这

管脚 在 这 第一 portion 的 这 总线 循环 和 数据 将 是 transferred 在 这 管脚 在 第二 portion 的

这 总线 循环. 地址 必须 是 有效的 较早的 至 这 下落 边缘 的 ale(作), 在 这个 时间 这 ds21372

latches 这 地址 从 这 ad0 至 ad7 管脚. 有效的 写 数据 必须 是 呈现 和 使保持 稳固的 在

这 后来的 portion 的 这 ds 或者

WR

脉冲. 在 一个 读 循环, 这 ds21372 输出 一个 字节 的 数据 在 这

latter portion 的 这 ds 或者

RD

脉冲. 这 读 循环 是 terminated 和 这 总线 returns 至 一个 高

阻抗 状态 作

RD

transitions 高 在 intel 定时 或者 作 ds transitions 低 在 motorola 定时. 这

ds21372 能 也 是 容易地 连接 至 非-多路复用 buses. rclk 和 tclk 是 使用 至 更新

counters 和 加载 transmit 和 receive 模式 寄存器. 在 慢 时钟 比率, sufficient 时间 必须 是

允许 为 这些 端口 行动.

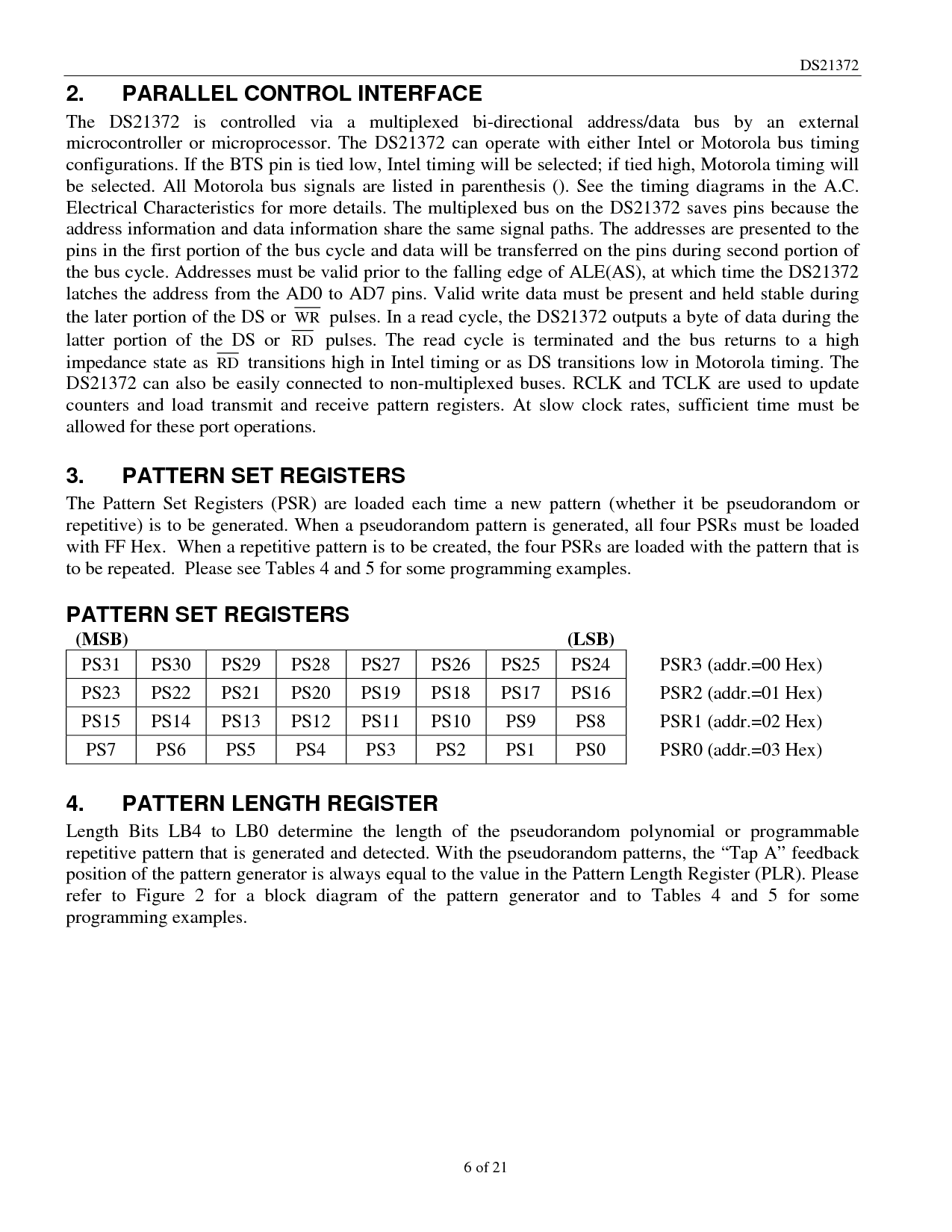

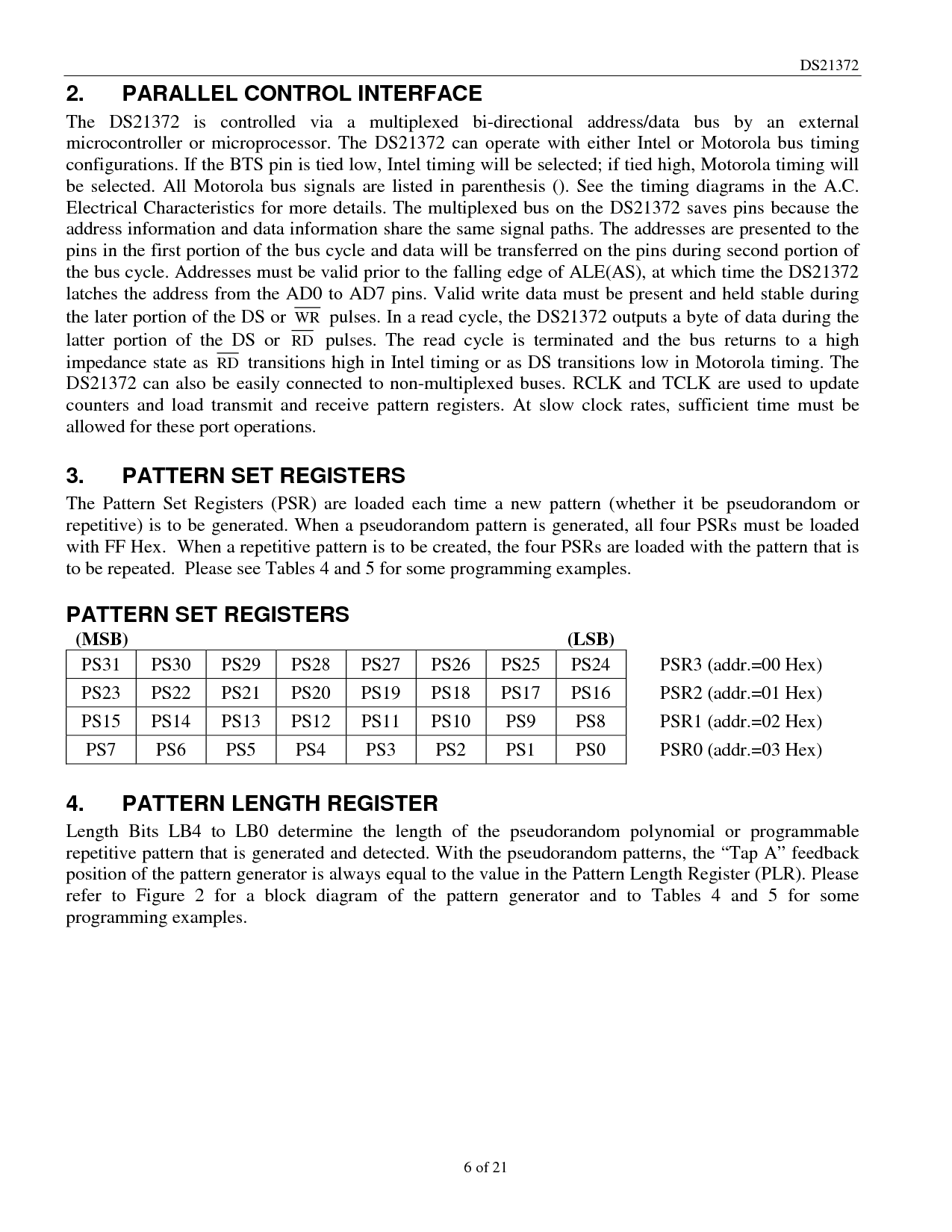

3. 模式 设置 寄存器

这 模式 设置 寄存器 (psr) 是 承载 各自 时间 一个 新 模式 (whether 它 是 pseudorandom 或者

repetitive) 是 至 是 发生. 当 一个 pseudorandom 模式 是 发生, 所有 四 psrs 必须 是 承载

和 ff 十六进制. 当 一个 repetitive 模式 是 至 是 创建, 这 四 psrs 是 承载 和 这 模式 那 是

至 是 重复的. 请 看 tables 4 和 5 为 一些 程序编制 examples.

模式 设置 寄存器

(msb) (lsb)

PS31 PS30 PS29 PS28 PS27 PS26 PS25 PS24 psr3 (地址.=00 十六进制)

PS23 PS22 PS21 PS20 PS19 PS18 PS17 PS16 psr2 (地址.=01 十六进制)

PS15 PS14 PS13 PS12 PS11 PS10 PS9 PS8 psr1 (地址.=02 十六进制)

PS7 PS6 PS5 PS4 PS3 PS2 PS1 PS0 psr0 (地址.=03 十六进制)

4. 模式 长度 寄存器

长度 位 lb4 至 lb0 决定 这 长度 的 这 pseudorandom polynomial 或者 可编程序的

repetitive 模式 那 是 发生 和 发现. 和 这 pseudorandom patterns, 这 “tap a” 反馈

位置 的 这 模式 发生器 是 总是 equal 至 这 值 在 这 模式 长度 寄存器 (plr). 请

谈及 至 图示 2 为 一个 块 图解 的 这 模式 发生器 和 至 tables 4 和 5 为 一些

程序编制 examples.