接受者 切换 特性

在 推荐 运行 供应 和 温度 范围 除非 否则 指定

标识 参数 最小值 典型值 最大值 单位

CLHT cmos/ttl 低-至-高 转变 时间 (

图示 3

) 3.5 6.5 ns

CHLT cmos/ttl 高-至-低 转变 时间 (

图示 3

) 2.7 6.5 ns

RCOP RxCLK 输出 时期 (

图示 7

) 25 T 50 ns

RSKM 接受者 Skew 余裕 (便条 6) f

=

20 MHz 1.1 ns

V

CC

=

5v, T

一个

=

25˚C (

图示 17

)f

=

40 MHz 700 ps

RCOH RxCLK 输出 高 时间 (

图示 7

)f

=

20 MHz 19 ns

f

=

40 MHz 6 ns

RCOL RxCLK 输出 低 时间 (

图示 7

)f

=

20 MHz 21.5 ns

f

=

40 MHz 10.5 ns

RSRC RxCLK 建制 至 RxCLK 输出 (

图示 7

)f

=

20 MHz 14 ns

f

=

40 MHz 4.5 ns

RHRC RxCLK 支撑 至 RxCLK 输出 (

图示 7

)f

=

20 MHz 16 ns

f

=

40 MHz 6.5 ns

RCCD RxCLK 在 至 RxCLK 输出 延迟

@

25˚c, V

CC

=

5.0v (

图示 9

) 7.6 11.9 ns

RPLLS 接受者 阶段 锁 循环 设置 (

图示 11

)10ms

RPDD 接受者 Powerdown 延迟 (

图示 15

)1µs

便条 6:

接受者 Skew 余裕 是 定义 作 这 有效的 数据 抽样 区域 在 这 接受者 输入. 这个 余裕 takes 在 账户 为 传输者 输出 skew(tccs)

和 这 建制 和 支撑 时间 (内部的 数据 抽样 window), 准许 LVDS 缆索 skew 依赖 在 类型/长度 和 源 时钟(txclk 在) jitter.

RSKM

≥

缆索 skew (类型, 长度) + 源 时钟 jitter (循环 至 循环).

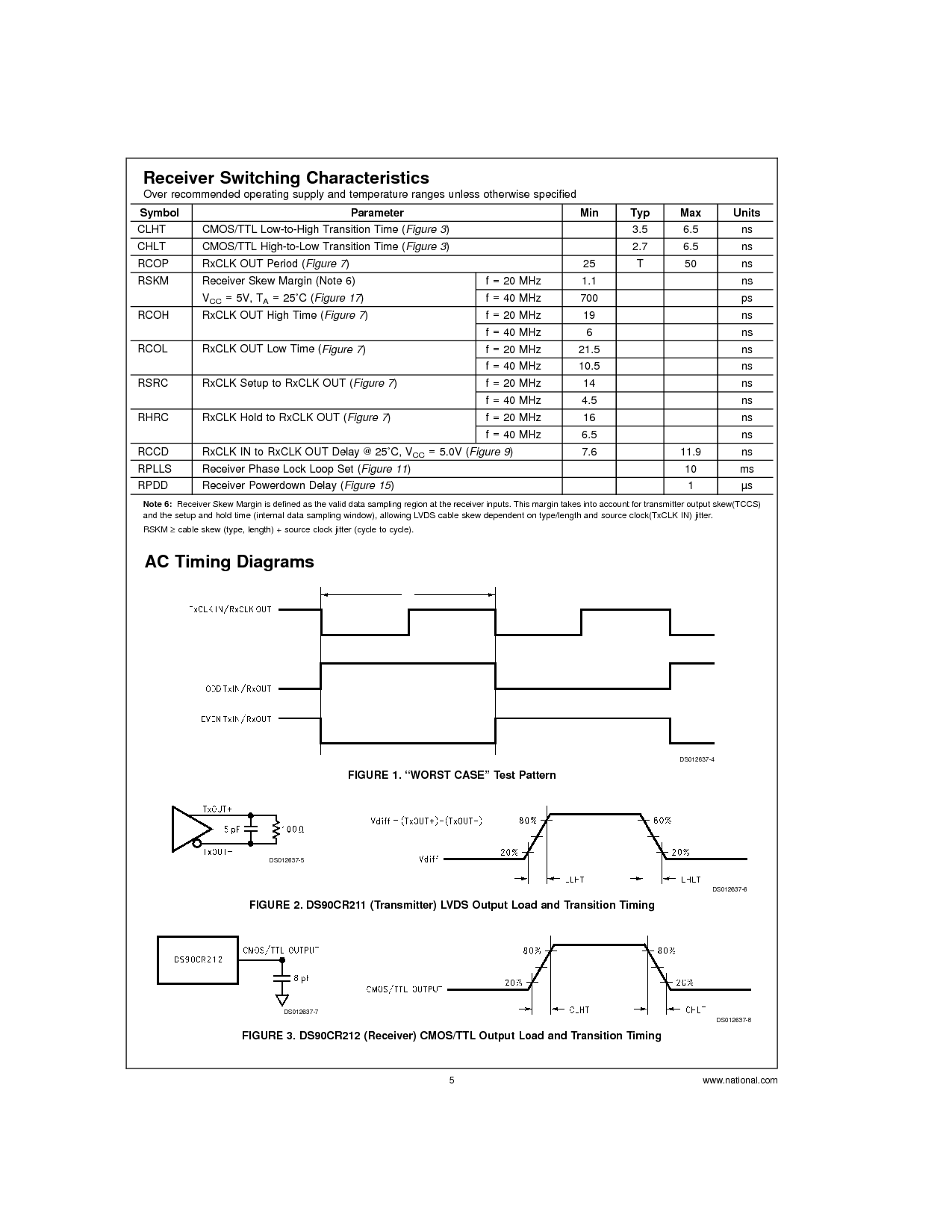

交流 定时 图解

ds012637-4

图示 1. “WORST CASE” 测试 模式

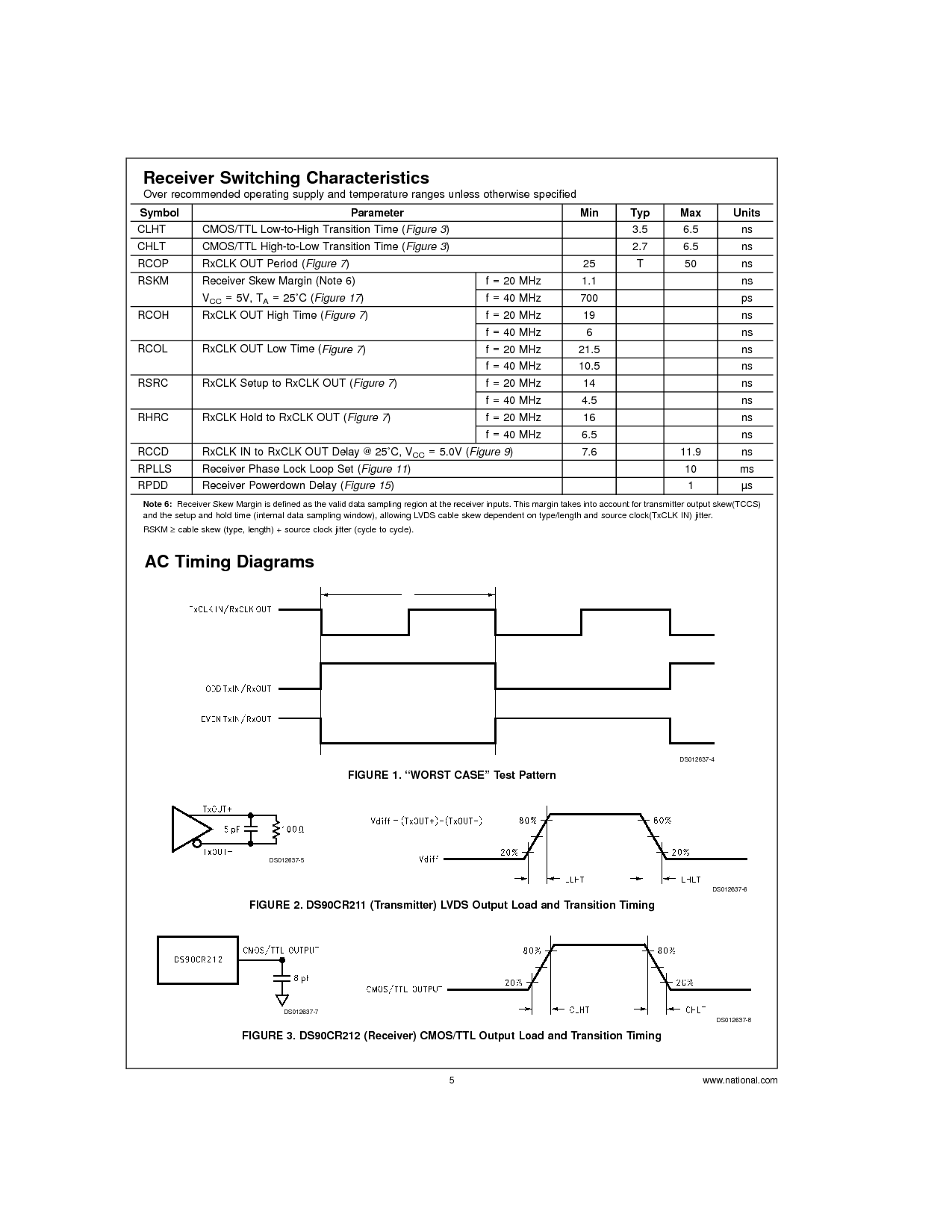

ds012637-5

ds012637-6

图示 2. DS90CR211 (传输者) LVDS 输出 加载 和 转变 定时

ds012637-7

ds012637-8

图示 3. DS90CR212 (接受者) cmos/ttl 输出 加载 和 转变 定时

www.国家的.com5