®

dsp101/102

7

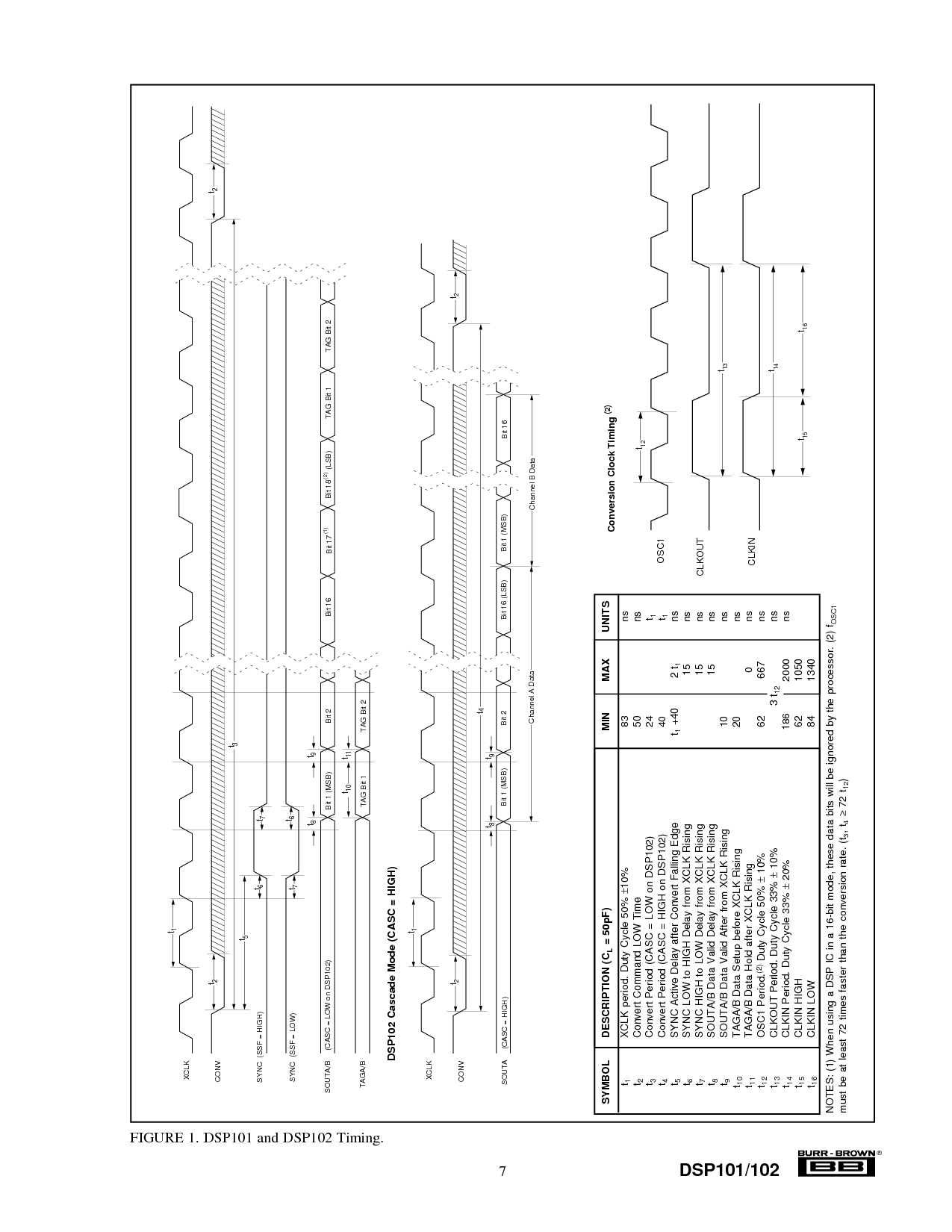

图示 1. dsp101 和 dsp102 定时.

注释: (1) 当 使用 一个 dsp ic 在 一个 16-位 模式, 这些 数据 位 将 是 ignored 用 这 processor. (2) f

OSC1

必须 是 在 least 72 时间 faster 比 这 转换 比率. (t

3

, t

4

≥

72 t

12

)

标识 描述 (c

L

= 50pf) 最小值 最大值 单位

t

1

xclk 时期. 职责 循环 50%

±

10% 83 ns

t

2

转变 command 低 时间 50 ns

t

3

转变 时期 (casc = 低 在 dsp102) 24 t

1

t

4

转变 时期 (casc = 高 在 dsp102) 40 t

1

t

5

同步 起作用的 延迟 之后 转变 下落 边缘 t

1

+40 2 t

1

ns

t

6

同步 低 至 高 延迟 从 xclk rising 15 ns

t

7

同步 高 至 低 延迟 从 xclk rising 15 ns

t

8

souta/b 数据 有效的 延迟 从 xclk rising 15 ns

t

9

souta/b 数据 有效的 之后 从 xclk rising 10 ns

t

10

taga/b 数据 建制 在之前 xclk rising 20 ns

t

11

taga/b 数据 支撑 之后 xclk rising 0 ns

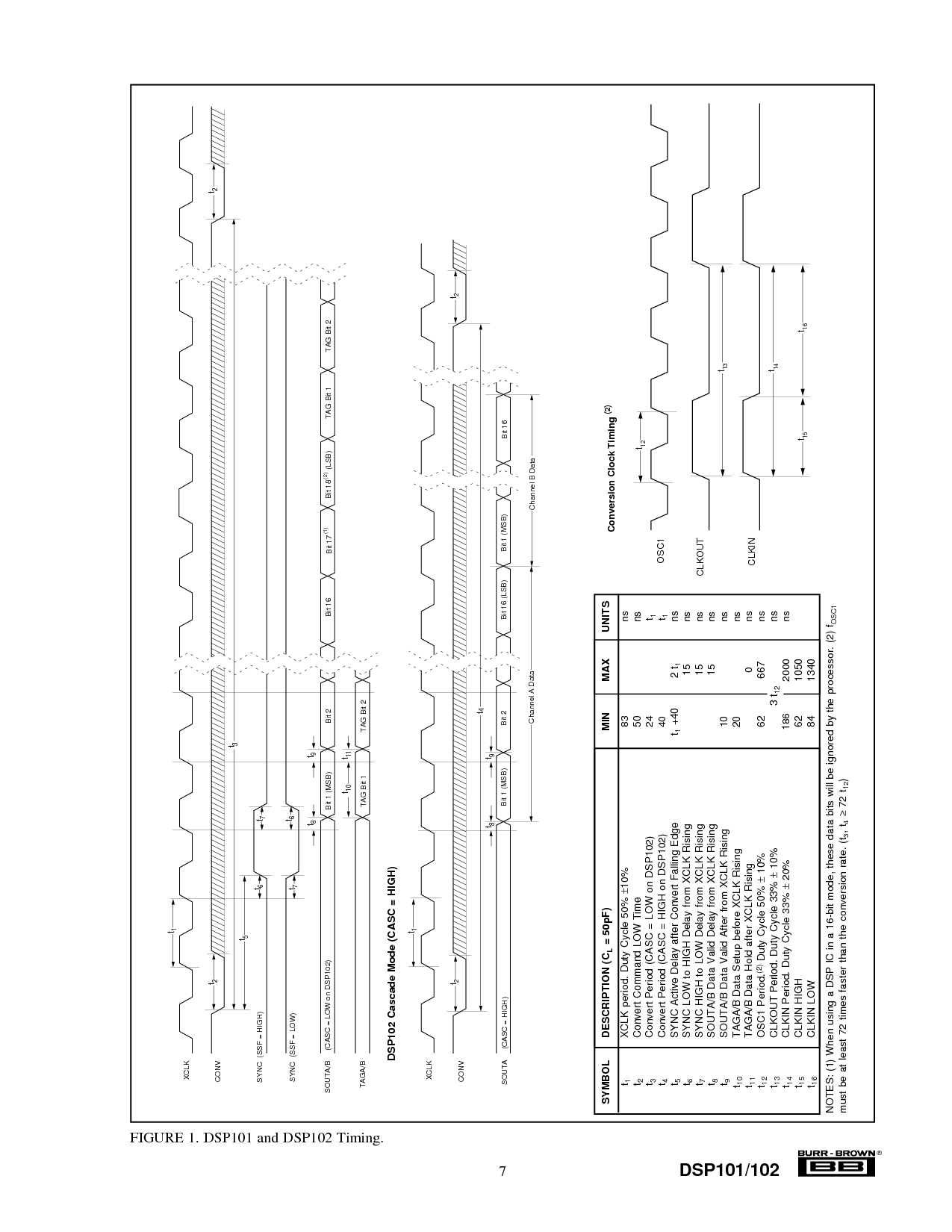

t

12

osc1 时期.

(2)

职责 循环 50%

±

10% 62 667 ns

t

13

clkout 时期. 职责 循环 33%

±

10% 3 t

12

ns

t

14

clkin 时期. 职责 循环 33%

±

20% 186 2000 ns

t

15

clkin 高 62 1050

t

16

clkin 低 84 1340

t

12

t

13

t

14

OSC1

CLKOUT

CLKIN

转换 时钟 定时

(2)

t

15

t

16

XCLK

CONV

同步 (ssf = 高)

同步 (ssf = 低)

XCLK

CONV

souta (casc = 高)

位 1 (msb)

t

2

t

5

t

3

t

2

t

6

t

7

t

6

t

7

t

4

t

9

位 1 (msb) 位 2 位 16 (lsb)

t

2

t

1

t

1

t

2

位 16

dsp102 cascade 模式 (casc = 高)

频道 一个 数据

频道 b 数据

souta/b (casc = 低 在 dsp102)

t

9

位 1 (msb) 位 2 位 16

位 17

位 18 (lsb)

(1) (2)

t

8

tag 位 1 tag 位 2

taga/b

t

11

tag 位 1 tag 位 2

t

10

t

8