®

dsp101/102

9

这 转变 command 在 管脚 21 导致 一个 同步 脉冲波 至 是

输出 在 管脚 15, followed 用 这 数据 从 这 previous

转换 输出 在 管脚 20. 这 同步 脉冲波 将 是 高

为 一个 位 时钟 循环, 自从 管脚 12 是 系 高. (一个 低

同步 脉冲波 将 是 输出 在 管脚 15 如果 管脚 12 是 系 低.)

数据 是 serially transmitted 在 一个 msb-第一 数据 stream, 在

二进制的 二’s complement format. 两个都 这 同步 脉冲波 (管脚

15) 和 这 数据 stream (管脚 20) 是 同步 至 这 位

时钟 (在 管脚 13 和 16), 和 这 定时 relationships

显示 在 图示 1.

之后 这 18 位 的 数据 从 这 previous 转换 有

被 transmitted, 管脚 20 将 continue 至 时钟 输出 lows

直到 一个 新 转变 command restarts 这 处理, 自从 管脚

18 (这 tag 输入) 是 grounded. 如果 管脚 18 是 系 高, 管脚

20 将 时钟 输出 highs 在 转换 循环.

转换

一个 下落 边缘 在 管脚 21 (conv) puts 这 内部的 抽样

电容 在 这 支撑 状态 和 最小 aperture jitter,

initiates 一个 转换 同步 至 这 转换 时钟,

和 输出 这 数据 从 这 previous 转换 和 一个

适合的 同步 脉冲波. 在 这 dsp102, 一个 单独的 转变

command 同时发生地 样本 两个都 途径. 这 tim-

ing relationship 在 这 转变 command, 同步 和

这 输出 数据 是 显示 在 图示 1. 两个都 同步 和 这

输出 数据 是 同步 至 xclk, 这 系统 位 时钟.

下列的 一个 转变 command 下落 边缘, 管脚 21 必须 是

使保持 低 在 least 50ns.

转变 commands 能 是 sent 至 这 dsp101 和 dsp102

完全地 异步的 至 其它 clocks 在 这 系统. 这个

准许 外部 events 至 是 使用 至 触发 conversions.

从 图示 1, 它 能 是 seen 那 二 不同的 clocking

情况 必须 是 考虑 在 determining 这 最小

可接受的 时间 在 转变 commands. 第一, 那里

需要 至 是 一个 最小 的 24 xclk 时期 在 转变

commands, 至 准许 内部的 同步 和 transmis-

sion 的 同步 和 这 数据. (在 这 cascade 模式 在 这

dsp102, 那里 需要 至 是 在 least 40 xclk 时期 在

转变 commands, 至 准许 传递 的 这 32-位 数据

words.) 当 使用 和 dsp processors 编写程序 为

数据 words 变长 比 16 位, 这 传递 时间 至 这

处理器 将 决定 这 最小 时间 在 con-

vert commands.

这 第二 限制 在 转变 commands 是 这 需要-

ment 那 这 内部的 相似物-至-数字的 转换器 是 给

足够的 时间 至 完全 一个 转换, 变换 这 数据 至 这

输出 寄存器, 和 acquire 一个 新 样本. 这个 情况 是

符合 用 having 一个 最小 的 24 clkin 时期 在

转变 commands, 或者 一个 最小 的 72 时钟 循环 在

osc1, 如果 它 是 使用 至 发生 这 转换 时钟 (clkout

驱动 clkin).

信号 acquisition

之后 一个 转换 是 完成, 这 dsp101 或者 dsp102

将 转变 后面的 至 这 抽样 模式. 和 在 least 24

clkin 时期 在 转变 commands, 这 一个/d 将

有 had sufficient 时间 至 acquire 一个 新 输入 样本 至 全部

评估 精度.

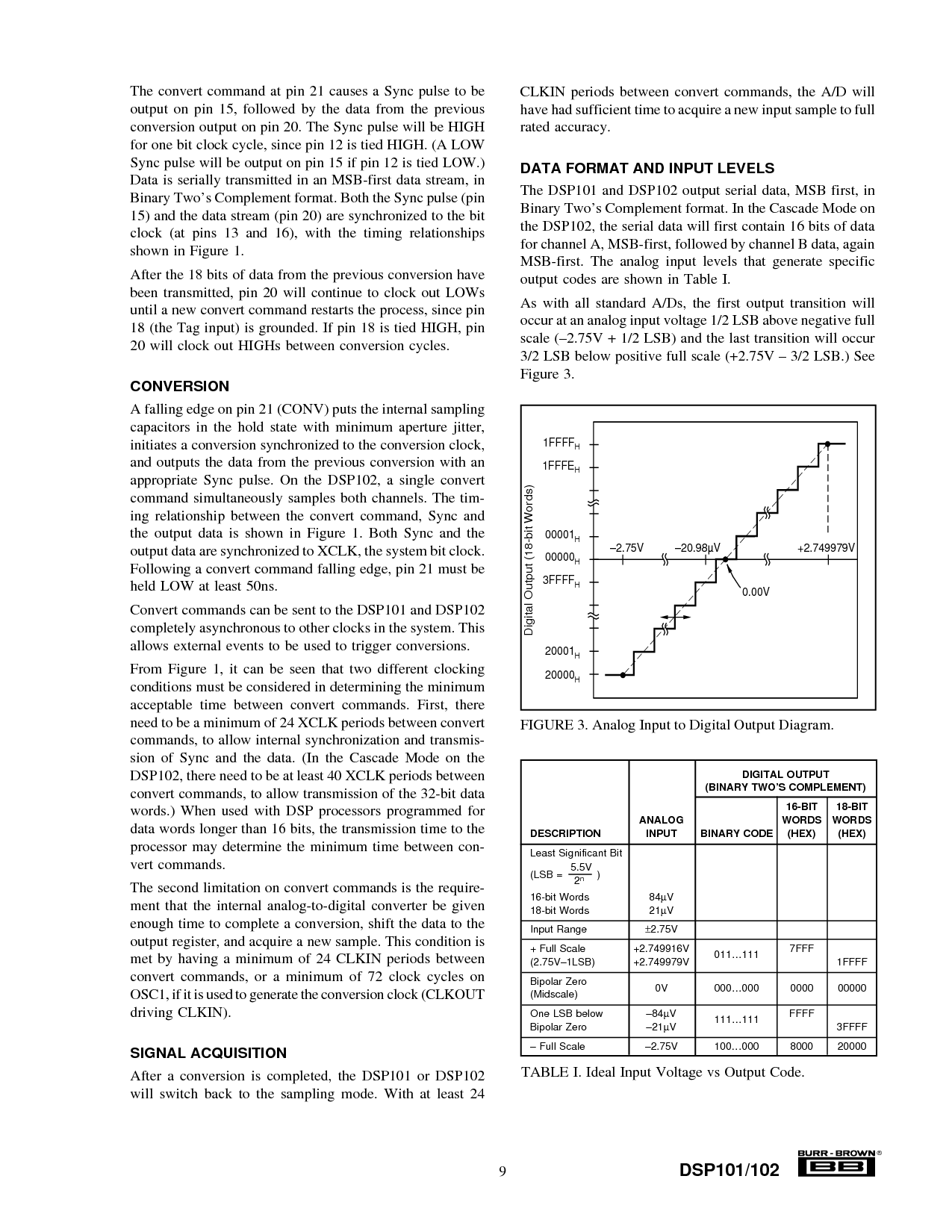

数据 format 和 输入 水平

这 dsp101 和 dsp102 输出 串行 数据, msb 第一, 在

二进制的 二’s complement format. 在 这 cascade 模式 在

这 dsp102, 这 串行 数据 将 第一 包含 16 位 的 数据

为 频道 一个, msb-第一, followed 用 频道 b 数据, 又一次

msb-第一. 这 相似物 输入 水平 那 发生 明确的

输出 代号 是 显示 在 表格 i.

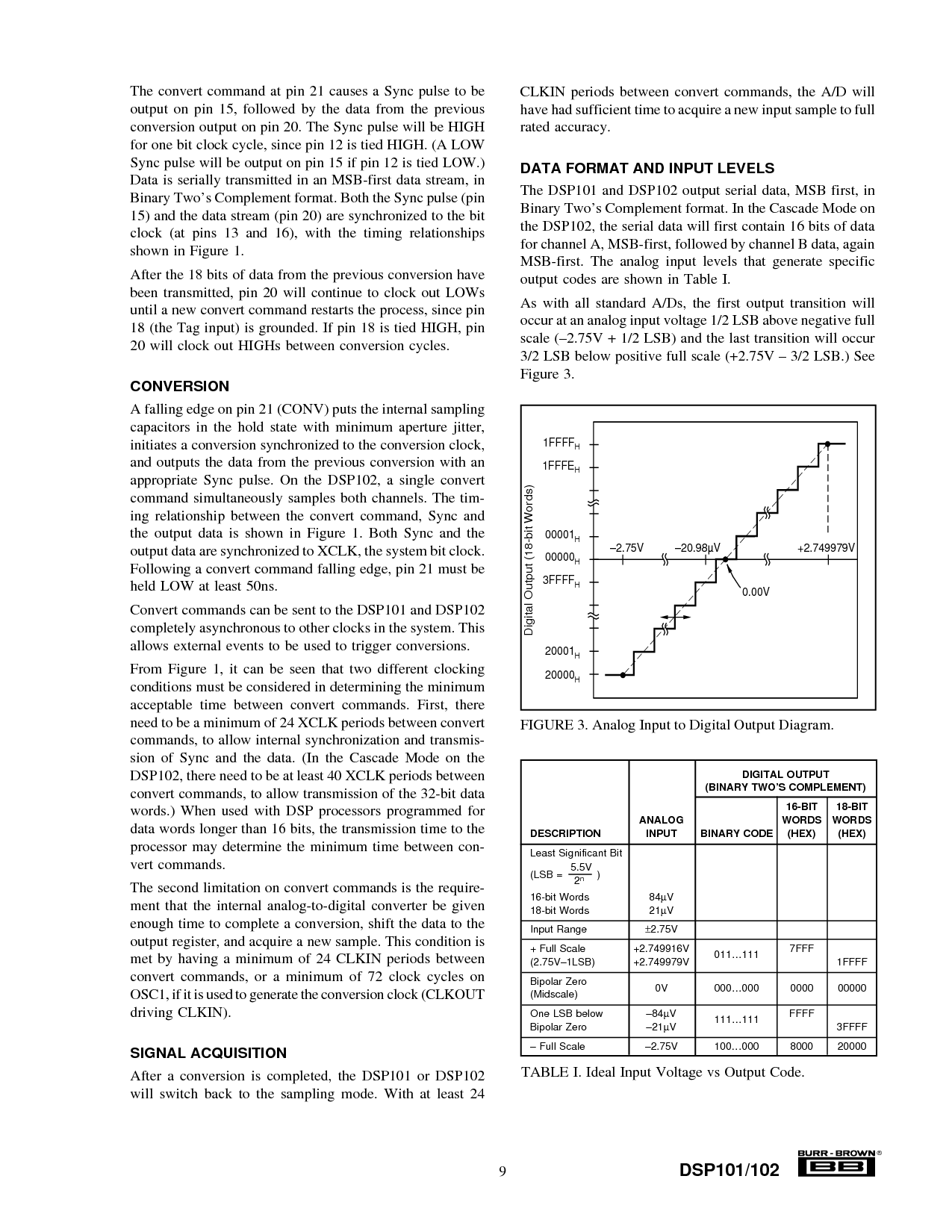

作 和 所有 标准 一个/ds, 这 第一 输出 转变 将

出现 在 一个 相似物 输入 电压 1/2 lsb 在之上 负的 全部

规模 (–2.75v + 1/2 lsb) 和 这 last 转变 将 出现

3/2 lsb 在下 积极的 全部 规模 (+2.75v – 3/2 lsb.) 看

图示 3.

1FFFF

H

1FFFE

H

00001

00000

H

3FFFF

H

20001

H

20000

H

数字的 输出 (18-位 words)

0.00v

+2.749979v–20.98µv–2.75v

H

图示 3. 相似物 输入 至 数字的 输出 图解.

数字的 输出

(二进制的 二’s complement)

16-位 18-位

相似物 WORDS WORDS

描述 输入 二进制的 代号 (十六进制) (十六进制)

least 重大的 位

(lsb = )

16-位 words 84

µ

V

18-位 words 21

µ

V

输入 范围

±

2.75v

+ 全部 规模 +2.749916v 7FFF

(2.75v–1lsb) +2.749979v 1FFFF

双极 零

(midscale)

一个 lsb 在下 –84

µ

V FFFF

双极 零 –21

µ

V 3FFFF

– 全部 规模 –2.75v 100…000 8000 20000

5.5v

2

n

表格 i. 完美的 输入 电压 vs 输出 代号.

0V 000…000 0000 00000

011…111

111…111